基于vhdl蜂鸣器程序设计详解

编程实验

描述

蜂鸣器是一种一体化结构的电子讯响器,采用直流电压供电,广泛应用于计算机、打印机、复印机、报警器、电子玩具、汽车电子设备、电话机、定时器等电子产品中作发声器件。蜂鸣器主要分为压电式蜂鸣器和电磁式蜂鸣器两种类型。蜂鸣器在电路中用字母“H”或“HA”(旧标准用“FM”、“ZZG”、“LB”、“JD”等)表示。本文为大家介绍基于vhdl蜂鸣器程序设计。

实验步骤

1、设置端口

1)输入端口

CLK:40MHZ系统时钟输入端口。

2)输出端口

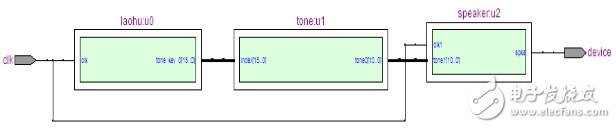

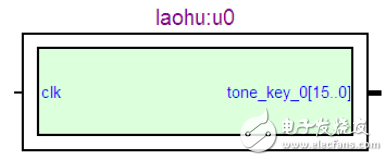

device:乐曲的声音输出端口,输出的是对应各音符频率的方波信号。 2、设置模块 1)自动演奏模块

自动演奏模块可以自动播放电子琴内置乐曲,按节拍读取内置乐谱。将键盘输入的音符信号输出。因此,本模块是向Tone模块提供音符信息。

首先,对40MHz系统时钟进行10M的分频,得到4Hz的信号,这样一秒中就可以按照四拍进行。然后依照此频率进行地址累计。

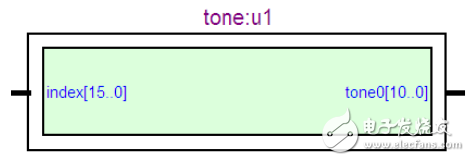

音频发生器模块

根据自动演奏模块的信号输出,不同的信号被翻译为不同的频率。

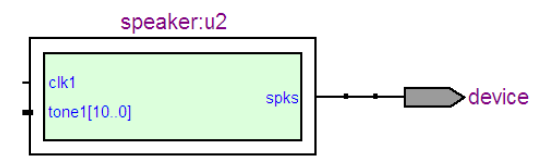

蜂鸣器驱动模块

根据音频发生器发出音频的不同,蜂鸣器得到的驱动也不同。首先,对系统时钟进行40分频,再对1mhz的脉冲再次分频,得到所需要的音符频率,然后再进行2分频。

实验代码

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity tone is port( index: in std_logic_vector(15 downto 0); --音符输入信号

tone0: out integer range 0 to 2047 --音符的分频系数 );

end tone;

architecture behavioral of tone is

begin

search :process(index) --此进程完成音符到音符的分频系数译码,音符的显示,高低音阶

begin

case index is

when “0000000000000001” => tone0<=1433;

when “0000000000000010” => tone0<=1277;

when “0000000000000100” => tone0<=1138;

when “0000000000001000” => tone0<=1074;

when “0000000000010000” => tone0<=960;

when “0000000000100000” => tone0<=853;

when “0000000001000000” => tone0<=759;

when “0000000010000000” => tone0<=716;

when “0000000100000000” => tone0<=358;

when “0000001000000000” => tone0<=319;

when “0000010000000000” => tone0<=284;

when “0000100000000000” => tone0<=268;

when “0001000000000000” => tone0<=239;

when “0010000000000000” => tone0<=213;

when “0100000000000000” => tone0<=190;

when “1000000000000000” => tone0<=638;

when others => tone0<=0;

end case;

end process;

end behavioral;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity speaker is port( clk1: in std_logic; --系统时钟12mhz

tone1: in integer range 0 to 2047; --音符分频系数

spks: out std_logic --驱动扬声器的音频信号 );

end speaker;

architecture behavioral of speaker is

signal preclk, fullspks:std_logic;

begin

p1:process(clk1)--此进程对系统时钟进行16分频

variable count: integer range 0 to 16;

begin

if clk1‘event and clk1=’1‘ then count:=count+1;

if count=8 then

preclk<=‘1’;

elsif count=16 then preclk<=‘0’;

count:=0;

end if;

end if;

end process p1;

p2:process(preclk,tone1)--对0.75mhz的脉冲再次分频,得到所需要的音符频率

variable count11:integer range 0 to 2047;

begin

if preclk‘event and preclk=’1‘ then

if count11

count11:=count11+1;

fullspks<=’1‘;

else

count11:=0;

fullspks<=’0‘;

end if;

end if;

end process p2;

p3:process(fullspks)--此进程对fullspks进行2分频

variable count2: std_logic:=’0‘;

begin

if fullspks’event and fullspks=‘1’ then

count2:=not count2;

if count2=‘1’ then

spks<=‘1’;

else spks<=‘0’;

end if;

end if;

end process p3;

end behavioral;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity laohu is port( clk: in std_logic;--系统时钟;键盘输入/自动演奏

tone_key_0: buffer std_logic_vector(15 downto 0)--音符信号输出

);

end laohu;

architecture behavioral of laohu is

signal count0:integer range 0 to 31;--change

signal clk2:std_logic;

begin p1:process(clk) --对12mhz系统时钟进行3m的分频,得到4hz的信号clk2

variable count:integer range 0 to 3000000;

begin if clk‘event and clk=’1‘ then

count:=count+1;

if count=1500000 then

clk2<=’1‘;

elsif count=3000000 then

clk2<=’0‘;

count:=0;

end if;

end if;

end process p1;

p2:process(clk2)--此进程完成自动演奏部分乐曲的地址累加

begin if clk2’event and clk2=‘1’ then

if count0=29 then

count0<=0;

else count0<=count0+1;

end if;

end if;

end process p2;

p3:process(count0,tone_key_0)

begin

case count0 is--此case语句:存储自动演奏部分的乐曲

when 0 => tone_key_0<=b“00000001_00000000”; --1

when 1 => tone_key_0<=b“00000010_00000000”; --2

when 2 => tone_key_0<=b“00000100_00000000”; --3

when 3 => tone_key_0<=b“00000001_00000000”; --1

when 4 => tone_key_0<=b“00000001_00000000”; --1

when 5 => tone_key_0<=b“00000010_00000000”; --2

when 6 => tone_key_0<=b“00000100_00000000”; --3

when 7 => tone_key_0<=b“00000001_00000000”; --1

when 8 => tone_key_0<=b“00000100_00000000”; --3

when 9 => tone_key_0<=b“00001000_00000000”; --4

when 10 => tone_key_0<=b“00010000_00000000”; --5

when 11 => tone_key_0<=b“00000100_00000000”; --3

when 12 => tone_key_0<=b“00001000_00000000”; --4

when 13 => tone_key_0<=b“00010000_00000000”; --5

when 14 => tone_key_0<=b“00010000_00000000”; --5

when 15 => tone_key_0<=b“00100000_00000000”; --6

when 16 => tone_key_0<=b“00010000_00000000”; --5

when 17 => tone_key_0<=b“00001000_00000000”; --4

when 18 => tone_key_0<=b“00000100_00000000”; --3

when 19 => tone_key_0<=b“00000001_00000000”; --1

when 20 => tone_key_0<=b“00010000_00000000”; --5

when 21 => tone_key_0<=b“00100000_00000000”; --6

when 22 => tone_key_0<=b“00010000_00000000”; --5

when 23 => tone_key_0<=b“00001000_00000000”; --4

when 24 => tone_key_0<=b“00000100_00000000”; --3

when 25 => tone_key_0<=b“00000001_00000000”; --1

when 26 => tone_key_0<=b“00000100_00000000”; --3

when 27 => tone_key_0<=b“00000000_00100000”; --di6

when 28 => tone_key_0<=b“00000001_00000000”; --1

when others => null;

end case;

end process p3;

end behavioral;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity beep0 is

port( clk:in std_logic; device:out std_logic );

end beep0;

architecture behavioral of beep0 is

component laohu is port( clk: in std_logic;--系统时钟;键盘输入/自动演奏

tone_key_0: out std_logic_vector(15 downto 0)--音符信号输出 );

end component;

component tone is

port( index: in std_logic_vector(15 downto 0);--音符输入信号

tone0: out integer range 0 to 2047--音符的分频系数 );

end component;

component speaker is

port(

clk1: in std_logic;--系统时钟12mhz

tone1: in integer range 0 to 2047; --音符分频系数

spks: out std_logic--驱动扬声器的音频信号 );

end component;

signal mid:std_logic_vector(15 downto 0);

signal tones:integer;

begin

u0:laohu port map(clk,mid);

u1:tone port map(mid,tones);

u2:speaker port map(clk,tones,device);

end behavioral;

-

VHDL程序设计教程 (pdf 经典电子书)2009-10-09 29948

-

VHDL语言100例详解2012-08-20 17151

-

FPGA的VHDL程序基本结构是怎样的?FPGA的VHDL程序设计单元关系图2018-09-07 2261

-

VHDL 语言程序的元素2009-09-28 437

-

出租车计价器VHDL程序2008-06-27 2162

-

VHDL设计中信号与变量问题的研究2010-04-12 1537

-

VHDL语言程序设计及应用(第二版)_姜立东2015-07-15 687

-

单片机驱动蜂鸣器原理与程序设计2015-12-23 1063

-

基于LPC2103的交流蜂鸣器音乐播放电路设计书2016-01-13 1142

-

VHDL应用工程2016-02-17 604

-

ARM_C语言程序设计详解2017-10-27 1048

-

vhdl数码管动态扫描程序设计(四种设计方案)2018-01-29 18928

-

使用VHDL硬件描述语言实现基带码发生器的程序设计与仿真2021-01-20 1105

-

STC学习:蜂鸣器2021-12-23 1274

-

multisim蜂鸣器驱动程序详解2024-08-09 3152

全部0条评论

快来发表一下你的评论吧 !