VHDL语言设计四人抢答器(三种设计方案)

编程实验

描述

本文为大家带来三种四人抢答器的VHDL语言设计方案介绍。

VHDL语言设计四人抢答器方案一

设计要求

l、设计用于竞赛的四人抢答器,功能如下:

(1)有多路抢答器,台数为四,能显示抢答台号;

(2)具有抢答开始后20秒倒计时,20秒倒计时后无人抢答显示超时,并报警;

(3)能显示超前抢答台号并显示犯规警报;

2、系统复位后进入抢答状态,当有一路抢答键按下时,该路抢答信号将其余各路抢答封锁,同时铃声响,直至该路按键松开,显示牌显示该路抢答台号。

3、用VHDL语言设计符合上述功能要求的四人抢答器,并用层次设计方法设计该电路。

电路工作原理

简易逻辑数字抢答器由主体电路与扩展电路组成。优先编码电路、锁存器、译码电路将参赛队的输入信号在显示器上输出;用控制电路和主持人开关启动报警电路,以上两部分组成主体电路。通过定时电路和译码电路将秒脉冲产生的信号在显示器上输出实现计时功能,构成扩展电路。

电路主要由脉冲产生电路、锁存电路、编码及译码显示电路、倒计时电路和音响产生电路组成。当有选手抢答时,首先锁存,阻止其他选手抢答,然后编码,再经译码器将数字显示在显示器上同时产生音响。主持人宣布开始抢答时,倒计时电路启动由20计到0,如有选手抢答,倒计时停止,如20秒后无人抢答,则会显示报警。

源程序

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityqdqis

port(clr,clk,clk0,en,a,b,c,d:instd_logic;

dps:outstd_logic_vector(3downto0);

count:outstd_logic_vector(7downto0);

speaker:outstd_logic);

end;

architectureoneofqdqis

signaldps1:std_logic_vector(3downto0);

signalcount1:std_logic_vector(7downto0);

signaltmp1,tmp2,tmp3:std_logic;

begin

p1:process(clr,en,tmp1,tmp2)

begin

ifclr=‘1’then

tmp1<=‘0’;tmp2<=‘0’;

dps1<=“0000”;

elsifen=‘1’then

iftmp1=‘0’then

ifa=‘1’then

tmp1<=‘1’;

dps1<=“0001”;

endif;

ifb=‘1’thentmp1<=‘1’;

dps1<=“0010”;

endif;

ifc=‘1’thentmp1<=‘1’;

dps1<=“0011”;

endif;

ifd=‘1’thentmp1<=‘1’;

dps1<=“0100”;

endif;

endif;

elsifen=‘0’then

iftmp2=‘0’then

ifa=‘1’then

tmp2<=‘1’;

dps1<=“0001”;

endif;

ifb=‘1’then

tmp2<=‘1’;

dps1<=“0010”;

endif;

ifc=‘1’then

tmp2<=‘1’;

dps1<=“0011”;

endif;

ifd=‘1’then

tmp2<=‘1’;

dps1<=“0100”;

endif;

endif;

endif;

endprocess;

p2:process(clr,clk,tmp1,tmp3)

begin

ifclk‘eventandclk=’1‘then

ifclr=’1‘thencount1<=“00100000”;

tmp3<=’0‘;

elsifen=’1‘andtmp1=’0‘andtmp3=’0‘then

ifcount1=“00000000”then

tmp3<=’1‘;

elsifcount1(3downto0)=“0000”then

count1(3downto0)<=“1001”;

count1(7downto4)<=count1(7downto4)-’1‘;

elsecount1(3downto0)<=count1(3downto0)-’1‘;

endif;

endif;

endif;

endprocess;

count<=count1;

dps<=dps1;

speaker<=((tmp3oraorborcord)andclk0);

end;

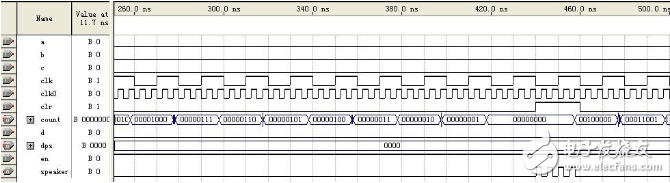

仿真波形

(一)无人抢答的仿真波形

由上图可知,当en=0时此时主持人并没有提出开始抢答的信号.en=1,开始抢答的时候20秒倒计时,时间到而无人抢答。(count=“00000000”),则speaker报警,按下清零开关(clr=1),重新开始20秒倒计时进行下一轮

(二)有人抢答的仿真波形

由上图可知,clr=1,系统进入初始状态,即count=“00100000”,dps=“0000”;en=0时,此时主持人并没有提出开始抢答的信号是不允许抢答的,若有人抢答(b=1),则speaker报警,且数码管显示组别(dps=“0010”)显示出犯规的组别;en=1时,开始正常抢答而且count开始20秒倒计时,在15秒时(count=“00010101”)有人抢答(a=1),倒计时暂停同时锁存器工作将其他组别的信号锁存后面的信号将视为无效,数码管显示组别(dps=“0001”),且speaker报警。

VHDL语言设计四人抢答器方案二

设计任务及要求:

(1)设计用于竞赛抢答的四人抢答器;

①有多路抢答,抢答台数为8;

②具有抢答开始后20秒倒计时,20秒倒计时后无人抢答显示超时,并报警;

③能显示超前抢答台号并显示犯规警报;

(2)系统复位后进入抢答状态,当有一路抢答按键按下,该路抢答信号将其余各路抢答信号封锁,同时铃声想起,直至该路按键松开,显示牌显示该路抢答台号;

(3)用VHDL语言设计符合上述功能要求的四人抢答器,并用层次化设计方法设计该电路;

设计思路

设计制作一个竞赛抢答器,每组受控于一个抢答开关,分别为S1,S2,S3,S4,低电平表示抢答有效;设置主持人控制键K,用于控制整个系统清0和抢答有效控制,按下复位键时,K=0,系统清零;抬起复位键时,K=1,抢答开始;系统具有第一抢答信号鉴别和锁存功能。在主持人将系统复位并使抢答有效开始后,第一抢答者按下抢答按钮,对应的输入引脚接低电位0,电路应记忆下第一抢答者的组别,并封锁其他各组的按钮,即其他任何一组按键都不会使电路响应;系统以两种方式指示第一抢答者:其一是通过译码程序显示其组别号;其二是在第一抢答者产生时,蜂鸣器警示;设置违规电路单元,当抢答者在主持人按下复位清零按钮之前就已经按下抢答按钮时,则给出违规信号为高电平。对应组别的红色信号灯亮;当20秒倒计时后无人抢答显示超时,并报警。

VHDL程序实现

1、正常抢答程序

此模块包括正常抢答第一信号鉴别和显示抢答台号,并发生声音提示。其中S1,S2,S3,S4为抢答按钮,当对应的按钮信号为0时表示有抢答信号;K为主持人按钮,按下复位键K时, K=0,系统清零;抬起复位键时,K=1,抢答开始;G为报警信号。其VHDL源程序如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee. std_logic_arith.all;

use ieee. std_logic_unsigned.all;

--------------------------------------------------------------------

entity qiangda is

port( S1,S2,S3,S4 : in std_logic; --输入:表示4个人,为0表示有抢答

K : in std_logic; --主持人抢答开始键

G : out std_logic; --报警信号

ledag : out std_logic_vector (6 downto 0);

Dout : out std_logic_vector(3 downto 0) ); --抢答结果显示

end qiangda;

--------------------------------------------------------------------

architecture behave of qiangda is

signal Enable_Flag : std_logic;--允许抢答控制变量,为1表示允许抢答

signal S : std_logic_vector(3 downto 0);

signal D : std_logic_vector(3 downto 0);

begin

process(S1,S2,S3,S4,K) --允许抢答控制

begin

S<=S1&S2&S3&S4;

If (K=‘1’) then

Enable_Flag<=‘1’;

elsif(S/=“1111”) then

Enable_Flag<=‘0’;

end if;

end process;

process(S1,S2,S3,S4,K) --抢答结果显示

begin

if(K=‘0’) then

D<=“0000”;

Elsif (Enable_Flag=‘1’) then

if(S1=‘0’) then

D(0)<=‘1’;

G<=‘0’;

elsif(S2=‘0’) then

D(1)<=‘1’;

G<=‘0’;

elsif(S3=‘0’) then

D(2)<=‘1’;

G<=‘0’;

elsif(S4=‘0’) then

D(3)<=‘1’;

G<=‘0’;

end if;

dout<=d;

end if;

end process;

process(d) --显示抢答成功者号码

begin

case d is

when “0000”=>ledag<=“0111111”;

when “0001”=>ledag<=“0000110”;

when “0010”=>ledag<=“1011011”;

when “0100”=>ledag<=“1001111”;

when “1000”=>ledag<=“1100110”;

when others=>ledag<=“0000000”;

end case;

end process;

end behave;

2、抢答倒计时程序

此模块为抢答20s倒计时程序,在主持人按下按钮K后此模块即开始工作,在20s倒计时完后会有声音提示,G为声音报警信号。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNT IS

PORT (CLK, Enable_Flag: IN STD_LOGIC;

H,L: OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

G:OUT STD_LOGIC); --声音报警

END COUNT;

ARCHITECTURE COUNT_ARC OF COUNT IS

BEGIN

PROCESS (CLK, Enable_Flag)

VARIABLE HH, LL: STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

IF CLK‘EVENT AND CLK=’1‘THEN

IF Enable_Flag=’1‘THEN

IF LL=0 AND HH=0 THEN

G<=’1‘;

ELSIF LL=0 THEN

LL: =“1001”;

HH: =HH-1;

ELSE

LL: =LL-1;

END IF;

ELSE

G<=’0‘;

HH: =“1001”;

LL: =“1001”;

END IF;

END IF;

H<=HH;

L<=LL;

END PROCESS;

END COUNT_ARC;

3、超前犯规抢答程序

此模块为违规电路。当抢答者在主持人复位系统之前就已按下抢答按钮,即当RESET=0时,有抢答信号出现,则Y=11表示某组违规,当RESET = 1时,显示违规组别。其中K为主持人按钮,S1,S2,S3,S4为抢答按钮,R1,R2,R3,R4为对应组别犯规红色显示灯。其VHDL源程序如下:

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY wg IS

PORT(K: IN std_logic;

S1, S2, S3, S4: IN std_logic;

R1, R2, R3, R4: OUT std_logic; --红色灯指示超前抢答台号

y: OUT std_logic_VECTOR (1 DOWNTO 0) );

END wg;

ARCHITECTURE a OF wg IS

SIGNAL TEMP1: STD_LOGIC;

SIGNAL TEMP2: STD_LOGIC_VECTOR (1 DOWNTO 0);

BEGIN

TEMP1<=S1 OR S2 OR S3 OR S4 ;

TEMP2<=K&TEMP1;

process(TEMP2) --显示抢答成功者号码

begin

case TEMP2 is

when “01”=>Y<=“11”;

when “10”=>Y<=“00”;

when “11”=>Y<=“00”;

when others=>Y<=“00”;

end case;

if(K<=‘0’) then

if(S1=‘0’) then

R1<=‘0’;

elsif(S2=‘0’) then

R2<=‘0’;

elsif(S3=‘0’) then

R3<=‘0’;

elsif(S4=‘0’) then

R4<=‘0’;

end if;

end if;

end process;

VHDL语言设计四人抢答器方案三

问题描述

设计一个4人参加的智力竞赛抢答计时器。电路具有回答问题时间控制功能。要求回答问题时间小于等于100妙(显示为0~99),时间显示采用倒计时方式。当达到限定时间时,发出声响以示警告;当有某一参赛者首先按下抢答开关时,相应显示灯亮并伴有声响,此时抢答器不再接受其他输入信号。

功能要求

1、用feng模块将选手按下按键信号输出高电平给锁存模块lockb,进行锁存的同时发出aim信号实现声音提示,并使count模块进行答题时间的倒计时,在计满100妙后送出声音提示;

2、用ch41a模块将抢答结果转换为二进制数;

3、用sel模块产生数码管片选信号;

4、用ch42a模块将对应数码管片选信号,送出需要的显示信号;

5、用七段译码器dispa模块进行译码。

各模块VHDL源代码

1、抢答鉴别模块FENG的VHDL源程序

--feng.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY FENG IS

PORT(CP,CLR:IN STD_LOGIC;

Q :OUT STD_LOGIC);

END FENG;

ARCHITECTURE FENG_ARC OF FENG IS

BEGIN

PROCESS(CP,CLR)

BEGIN

IF CLR=‘0’THEN

Q<=‘0’;

ELSIF CP‘EVENT AND CP=’0‘THEN

Q<=’1‘;

END IF;

END PROCESS;

END FENG_ARC;

2、片选信号产生模块SEL的VHDL源程序

--sel.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SEL IS

PORT(CLK:IN STD_LOGIC;

a:OUT INTEGER RANGE 0 TO 7);

END SEL;

ARCHITECTURE SEL_ARC OF SEL IS 片选信号产生模块SEL

BEGIN

PROCESS(CLK)

VARIABLE AA:INTEGER RANGE 0 TO 7;

BEGIN

IF CLK’EVENT AND CLK=‘1’THEN

AA:=AA+1;

END IF;

A<=AA;

END PROCESS;

END SEL_ARC;

3、锁存器模块LOCKB的VHDL源程序

-lockb.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LOCKB IS

PORT(D1,D2,D3,D4:IN STD_LOGIC;

CLK,CLR:IN STD_LOGIC;

Q1,Q2,Q3,Q4,ALM:OUT STD_LOGIC);

END LOCKB;

ARCHITECTURE LOCK_ARC OF LOCKB IS

BEGIN

PROCESS(CLK)

BEGIN

IF CLR=‘0’THEN

Q1<=‘0’;

Q2<=‘0’;

Q3<=‘0’;

Q4<=‘0’;

ALM<=‘0’; 模块LOCKB

ELSIF CLK‘EVENT AND CLK=’1‘THEN

Q1<=D1;

Q2<=D2;

Q3<=D3;

Q4<=D4;

ALM<=’1‘;

END IF;

END PROCESS;

END LOCK_ARC;

4、转换模块CH41A的VHDL源程序

--ch41a..vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CH41A IS

PORT(D1,D2,D3,D4:IN STD_LOGIC;

Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END CH41A;

ARCHITECTURE CH41_ARC OF CH41A IS 转换模块CH41A

BEGIN

PROCESS(D1,D2,D3,D4)

VARIABLE TMP:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

TMP:=D1&D2&D3&D4;

CASE TMP IS

WHEN “0111”=>Q<=“0001”;

WHEN “1011”=>Q<=“0010”;

WHEN “1101”=>Q<=“0011”;

WHEN “1110”=>Q<=“0100”;

WHEN OTHERS=>Q<=“1111”;

END CASE;

END PROCESS;

END CH41_ARC;

5、3选1模块CH31A的VHDL源程序

--ch31a.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CH31A IS

PORT(SEL:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

D1,D2,D3:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END CH31A;

ARCHITECTURE CH31_ARC OF CH31A IS

BEGIN

PROCESS(SEL,D1,D2,D3)

BEGIN

CASE SEL IS

WHEN “000”=>Q<=D1;

WHEN “001”=>Q<=D2;

WHEN “111”=>Q<=D3;

WHEN OTHERS=>Q<=“1111”;

END CASE;

END PROCESS;

END CH31_ARC;

6、倒计时模块COUNT的VHDL源程序

倒计时模块COUNT如图16-7所示,该模块实现答题时间的倒计时,在计满100s后送出声音提示。

--count.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNT IS

PORT(CLK,EN:IN STD_LOGIC; 倒计时 模块COUNT

H,L:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

SOUND:OUT STD_LOGIC);

END COUNT;

ARCHITECTURE COUNT_ARC OF COUNT IS

BEGIN

PROCESS(CLK,EN)

VARIABLE HH,LL:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF CLK’EVENT AND CLK=‘1’THEN

IF EN=‘1’THEN

IF LL=0 AND HH=0 THEN

SOUND<=‘1’;

ELSIF LL=0 THEN

LL:=“1001”;

HH:=HH-1;

ELSE

LL:=LL-1;

END IF;

ELSE

SOUND<=‘0’;

HH:=“1001”;

LL:=“1001”;

END IF;

END IF;

H<=HH;

L<=LL;

END PROCESS;

END COUNT_ARC;

7、显示译码模块DISP的VHDL源程序

--disp.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DISP IS 显示译码模块DISP

PORT(D:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Q:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END DISP;

ARCHITECTURE DISP_ARC OF DISP IS

BEGIN

PROCESS(D)

BEGIN

CASE D IS

WHEN“0000”=>Q<=“0111111”;

WHEN“0001”=>Q<=“0000110”;

WHEN“0010”=>Q<=“1011011”;

WHEN“0011”=>Q<=“1001111”;

WHEN“0100”=>Q<=“1100110”;

WHEN“0101”=>Q<=“1101101”;

WHEN“0110”=>Q<=“1111101”;

WHEN“0111”=>Q<=“0100111”;

WHEN“1000”=>Q<=“1111111”;

WHEN“1001”=>Q<=“1101111”;

WHEN OTHERS=>Q<=“0000000”;

END CASE;

END PROCESS;

END DISP_ARC;

-

怎样设计一个四人参加的智力竞赛抢答计时器2022-01-11 1849

-

怎样去设计一个基于STM32的四人抢答器2021-09-24 3523

-

基于STM32的抢答器设计2021-07-26 3168

-

设计一个四人抢答器的说明书详细概述2019-12-04 2590

-

使用FPGA和VHDL语言进行的抢答器设计资料合集免费下载2019-06-03 1503

-

plc控制的抢答器设计(三种实用设计方案介绍)2018-01-31 84108

-

四人抢答器电路设计方案汇总(六款模拟电路设计原理图详解)2018-01-29 362946

-

十路抢答器电路设计方案汇总(三款模拟+仿真设计电路图)2018-01-18 19761

-

四人抢答器电路图2016-06-27 3868

-

四路抢答器 用74LS74作为D触发器2012-12-22 17242

-

八路定时抢答器的设计方案2012-08-16 10527

-

vhdl四人抢答器2012-07-17 10528

-

四人智力竞赛抢答器2008-12-01 14581

全部0条评论

快来发表一下你的评论吧 !