N通道和P通道场效应晶体管(FET)之间的区别是什么?

描述

晶体管是现代电子电路中至关重要的半导体器件。它们可以执行两种主要功能。首先,作为其真空管前身三极管,晶体管可以放大电信号。其次,晶体管可以作为计算机的信息处理和存储的开关设备。场效应晶体管是控制电流通过电场的半导体器件。

晶体管不仅可以放大电信号,还可以作为开关设备。计算机利用晶体管的开关能力进行算术和逻辑运算以及信息存储。它们使用二进制代码——以基数2书写的数字——来表示数字和功能。一系列的两个状态——0和1——表示数字。数字电路中的晶体管也以两个状态工作:“开”和“关”——或导通和不导通。“开”对应一个二进制数字状态,而“关”对应另一个。因此,包含适当切换晶体管的电路元素集合可以表征一个数字。

由FET的p-n结扩散过程形成的偶极层建立电场。这些电场控制输出的电路导通路径。这一机制是“场效应”一词的基础。对这些器件的兴趣主要源于其输入电路具有单个反向偏置二极管的特性。FET需要极小的直流输入电流,具有非常高的输入阻抗。

场效应晶体管的类型

场效应晶体管主要有三种类型:结型场效应晶体管(缩写为JFET,或简称为FET)、金属氧化物半导体场效应晶体管(MOSFET)和金属半导体场效应晶体管(MESFET)。

金属氧化物半导体的其他缩写有MOST(MOS晶体管)和IGFET(绝缘栅场效应晶体管)。MESFET是一种现代发展,采用高速度特性为基础半导体材料的砷化镓(GaAs)。数字应用中,MOSFET常用于集成电路,而JFET在模拟应用中更为常见。

本文介绍了结型场效应晶体管(JFET),并探讨了这些设备运行的原理。

结型场效应晶体管

结型场效应晶体管是一种三端器件,其中施加在一个端子的电压控制着另两个端子之间的电流——输出电路电流。

JFET有两种类型:n通道和p通道。由于电子的移动速度快于孔,n通道JFET比p通道JFET更为常见。

在双极结晶体管(BJT)中,导通水平依赖于两种载流子——电子和孔。然而,JFET是一种单极器件,因为其导通仅依赖于一种类型的载流子——电子(n通道)或孔(p通道)。

JFET的其他重要特性包括:

· 制造简单。

· 尺寸小,适合于LSI和VLSI数字阵列。

· 高输入阻抗——通常为几兆欧姆。

· 噪声比BJT小。

· 在零漏电流下没有偏置电压。

n通道结型场效应晶体管

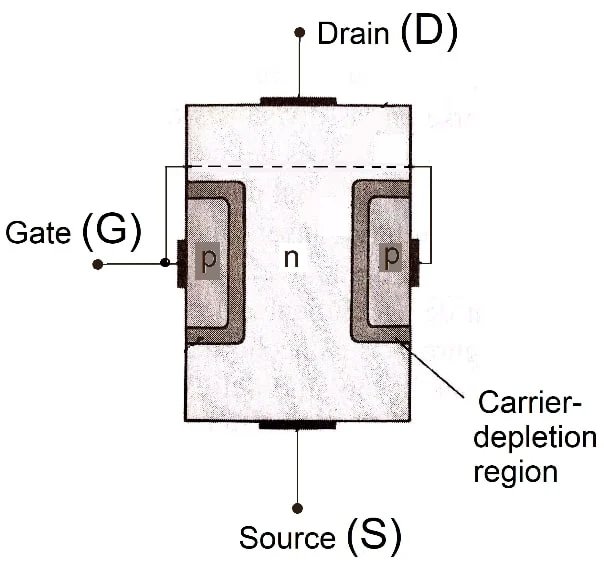

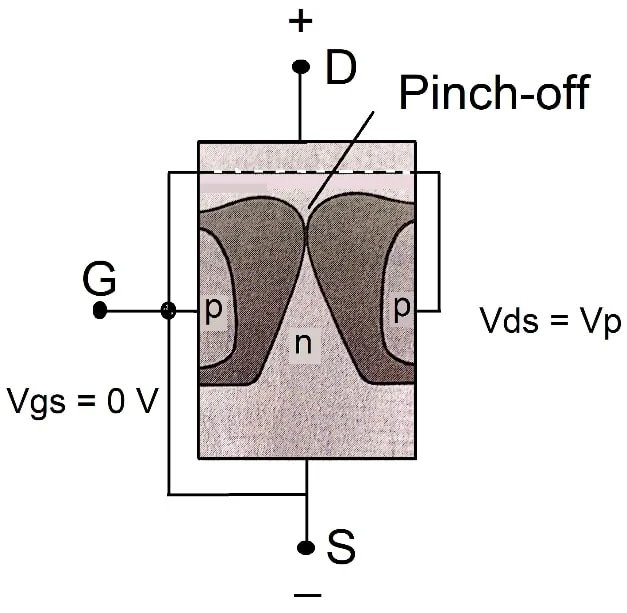

图1展示了n通道JFET的示意图。该图所示的几何形状简化了对JFET原理的分析。

图1

器件的两侧有重掺杂的p型受体杂质区域,形成栅极G。注意两个p型区域与栅极端子的连接。

两个栅区之间的区域是通道,构成了n型材料的结构。这个狭窄的半导体通道为源极和漏极之间提供了导通路径。大多数载流子通过源极S进入设备,并通过漏极D离开。源侧可以是通道的任一端。

该结构的操作基础是通过调整栅极G上的电压来改变S和D端子之间的电阻。

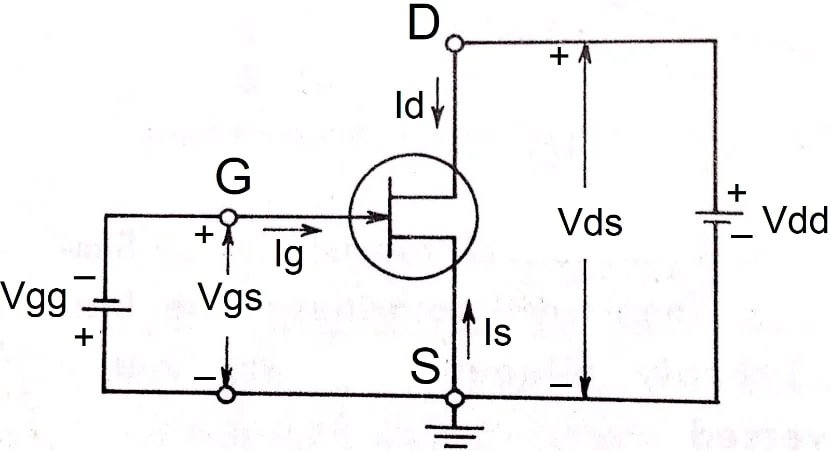

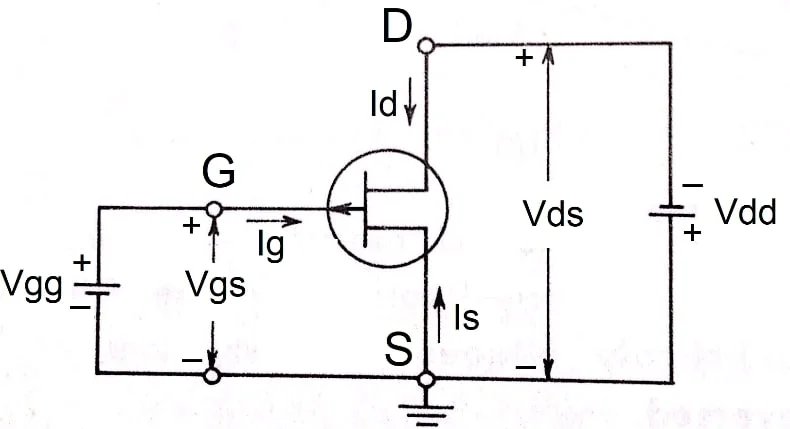

图2显示了n通道JFET的电路符号以及电流方向和电压极性的约定。

图2

栅极上的箭头指示从p型到n型JFET的结的方向。

Is = 从S流入的常规电流。

Id = 从D流入的常规电流。

Ig = 从G流入的常规电流。栅电流的流向是栅结前向偏置。

Vds = 漏源施加电压——如果d比s更正,则为正值。

Vdd = 漏极供电电压(外部电压源)。

Vgg = 栅极供电电压(外部电压源)。

Vgs = 栅源施加电压——如果g比s更正,则为正值。Vgs用于反向偏置p-n结(Vgs = - Vgg)。

对于n通道JFET,Id和Vds为正,Is和Vgs为负。

n通道JFET的工作原理

在对JFET端子施加任何外部电压之前,两个p-n结处于无偏置状态,形成载流子耗尽区或空间电荷区。多余的载流子(电子)被移除或“耗尽”了载流子耗尽区。因此,载流子耗尽区几乎没有自由载流子,无法支持导通(如图1所示)。

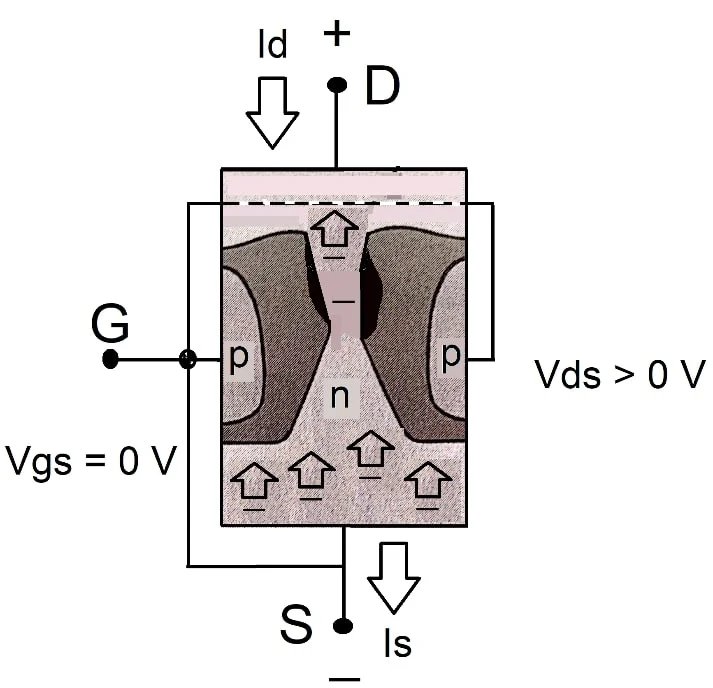

图3显示了Vgs = 0 V的条件——栅极与源极短路——并且Vds具有较低的正值。

图3

图3

正的漏极端子吸引通道中的电子,产生电流Id。

根据约定,电流流动方向与电子流动方向相反,因此电流Id流入D。

电流Is的大小和方向与Id相同。Is的正方向被定义为流入S。因此,在这种情况下,Is是负值。电流Ig非常小,这是JFET的一个重要特性。

通道的阻抗限制了图3中的电荷流动的大小。

注意,载流子耗尽区在靠近D侧时变得更宽。假设电阻均匀分布,通道中的电压降将从S的0 V增加到D的Vds。然后,从S到D的p-n结将越来越多地反向偏置。随着结上的反向偏置增加,静止的未覆盖电荷区域的厚度也增加。

未覆盖电荷是载流子耗尽区中的束缚电荷——在p型侧是负离子,在n型侧是正离子。它们在结处形成一个偶极层。源自正离子并终止于负离子的电场线是结上电压降的来源。术语“场效应”描述了这一机制,因为电流控制是由于与未覆盖电荷区域相关的场的扩展和反向偏置的增加。

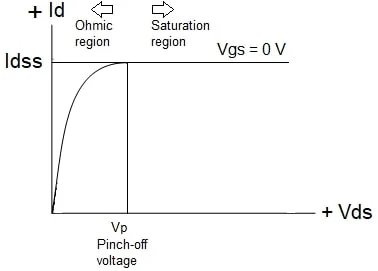

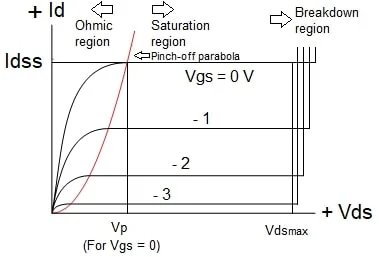

图4显示了n通道JFET的源漏特性,给出了Id与Vds的关系,且Vgs = 0。

图4

图4

当Id = 0时,通道是开放的。当Vds的值增加到几伏时,电流按欧姆定律线性上升;这就是为什么图形几乎呈直线增长——电阻是恒定的,n型JFET表现为简单的半导体电阻。

Vds的增量使耗尽区域变宽,通道的导电部分开始缩小——逐渐降低通道的有效宽度并增加其电阻。

由于通道中的欧姆降,缩小并不是均匀的,而是在距离源极更远的地方更为明显。

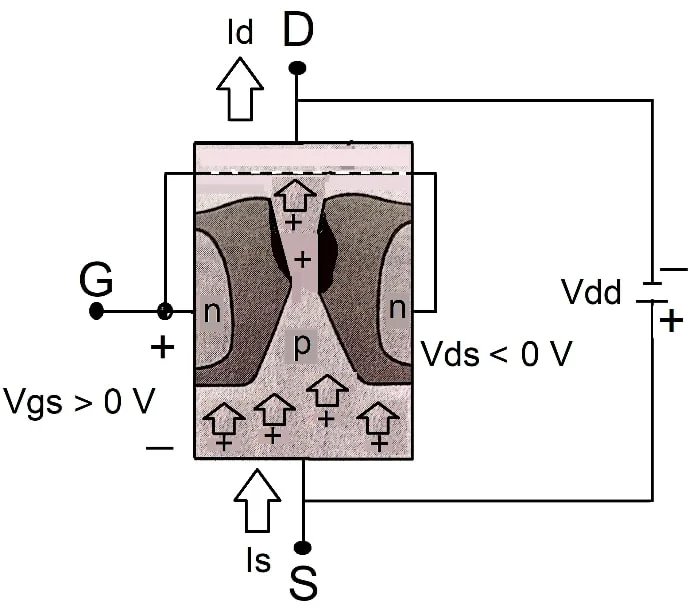

将Vds增加到看似两个耗尽区会接触的水平,如图5所示,导致一种被称为“挤压”的状态。在这种情况下,Vds = Vp——挤压电压。

图5

图5

当Vds达到Vp后,图4中的曲线开始平坦化。电流Id接近一个恒定值——饱和水平——表示为Idss(饱和短路漏电流)。曲线的水平区域中通道的电阻趋向于无穷大。在挤压状态下,存在一个小通道,电流密度很高。

在图5中,通道正好处于漏端的挤压阈值。将Vds增加到超过Vp会延长沿通道的两个耗尽区的接触,但Idss保持不变。在这种情况下,JFET充当电流源。

在挤压值时,通道不能完全关闭,使Id降至零——相反,Id保持在图4所示的饱和水平。如果是那样的话,提供p-n结反向偏置的欧姆降将会消失——失去导致挤压的耗尽区域。

Vgs提供额外的反向偏置

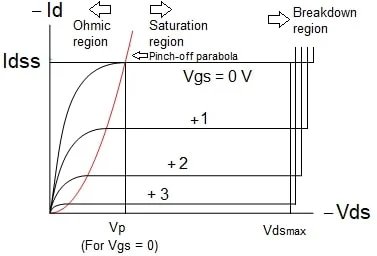

栅源电压(Vgs)控制JFET。设置栅极端子在低于源极的潜在电平时,会产生一系列Id与Vds的曲线,以Vgs为参数。图6展示了n通道JFET的典型曲线。

施加栅电压Vgs以提供额外的反向偏置,建立类似于Vgs = 0时的耗尽区域,但在较低的Vds值下,导致挤压——和饱和水平——在更小的Vds值下发生。然后,Vgs帮助Vds产生挤压。由于通道中Vds的降低,挤压在较小的漏电流下发生。

对栅极施加一些正电压——朝向前向偏置——使得产生挤压所需的Vds值增加,同时导致挤压出现的漏电流也相应增加。为了避免在栅极端子上产生不必要的电流,不宜施加高正电压。

如前所述,每个特性曲线在小的Vds值下都有一个欧姆区域——Id与Vds成正比——以及在大的Vds值下的恒定电流区域——在该区域内Id对Vds的响应很小。当Vds超过挤压水平时,被挤压的通道将电流限制在挤压发生时的大小。

图6还显示,挤压电压呈抛物线下降,而在大Vds值下,饱和电流的大小随着Vgs的负值增大而减少。

图6

图6

当Vgs = -Vp时,产生的饱和水平对应于最小的Id电流,我们可以得出结论,晶体管处于“关闭”状态。

注意,当Vds达到较高的幅度时,曲线突然上升到看似无穷大的水平。这种上升标志着p-n结的雪崩击穿;在这种情况下,只有输出电路元件限制了通过通道的电流。

施加在任何两个JFET端子之间的最大电压是导致p-n结雪崩击穿的最低电压。图6表明,当栅极反向偏置更强时,雪崩在较低的Vds值下发生。这是因为反向偏置栅电压(Vgs)叠加在漏电压(Vds)上,增加了p-n结上的实际电压。

P通道结型场效应晶体管

p通道JFET是n通道的反转,p型和n型材料的结构如图7所示。

图7

图7

图8显示了p通道JFET的电路符号和极性约定。

p通道JFET的电流方向和电压极性与n通道JFET相反;Id和Vds为负,Is和Vgs为正。因此,从栅极到源极的正电压增加会限制通道。

图8

图8

图8保留了图2中用于n通道JFET的参考,适用于电流的Id、Is和Ig的方向,以及电压Vds和Vgs的极性。栅极结的箭头指向相反的方向(显示从p型到n型的路径)。

图9显示了p通道JFET的典型曲线。

图9显示Vgs为正值,Vds为负值——源极电位高于漏极。

图9

图9

同样,在Vds为高负值时,曲线会突然上升到极端水平,暗示雪崩击穿。

注意:

这两种类型的晶体管——n通道和p通道——被称为互补的。电路中的n通道JFET可以由类似额定值的p通道晶体管替换,反转电源(Vdd)极性以及所有对极性敏感的器件,如电解电容器和二极管。

关于场效应晶体管

JFET的三个电气端子是漏极(D)、源极(S)和栅极(G)。

大多数载流子从源极通过通道流向漏极。通道可以是n型或p型晶体。栅源电压控制电场——以及通道中的漏电流(Id)。栅接点通常在其上施加反向偏置电压,导致栅极端子上几乎没有流动电流。

考虑n通道设备,如果栅源电压Vgs = 0 V而漏源电压Vds为正,电子会由于电场在通道中漂移。漏电流Id与通道的电阻成正比,前提是Vds较小。

在p-n结处,载流子耗尽区域的宽度取决于电压Vgs。Vgs的变化会改变通道的尺寸。载流子耗尽区域充当阀门,以控制通道中的电流量,从而影响电流Id的大小。

正的漏电压使p-n结反向偏置,主要在通道的漏端附近。当Vds达到挤压电压(Vp)时,通道的厚度在靠近漏端的地方几乎减小到零。当Vds = Vp时,Id并不为零,因为在挤压点和源端之间仍存在该电压,产生的电场使载流子通过通道加速到漏端。

对于Vds > Vp的值,栅极与漏极之间的耗尽区域厚度增加,而挤压点与源之间几乎没有变化。因此,额外的电压出现在耗尽区域,通道沿线的电场变化很小。其结果是Id值保持恒定。

在Vds = Vp和Vgs = 0 V下测得的电流称为饱和短路漏电流(Idss)。JFET通常在Vds > Vp和栅极施加反向偏置的情况下运行。当Vds + Vgs > Vp时,Id几乎独立于Vds。

在高Vds值下,p-n结会产生雪崩击穿。JFET的输入阻抗非常高,但在发生雪崩击穿时会急剧下降。

p通道JFET具有p型通道和n型栅极。它的工作方式类似于n通道晶体管,但电压和电流极性相反。

浮思特科技深耕功率器件领域,为客户提供IGBT、IPM模块等功率器件以及单片机(MCU)、触摸芯片,是一家拥有核心技术的电子元器件供应商和解决方案商。

-

结型场效应晶体管和N沟道场效应晶体管有什么区别2024-10-07 2056

-

MOSFET和鳍式场效应晶体管的不同器件配置及其演变2023-02-24 13728

-

场效应晶体管的选用经验分享2021-05-13 1945

-

如何进行场效应晶体管的分类和使用2020-07-02 2090

-

功率场效应晶体管的工作特性2019-10-11 13446

-

场效应晶体管的分类及作用2019-05-08 4248

-

MOS管与场效应晶体管背后的联系,看完后就全明白了2019-04-15 3303

-

选择合适的场效应晶体管,知道这六大诀窍就不用发愁了2019-04-02 2738

-

如何判断场效应晶体管方向,学会这几步轻松搞定2019-03-29 3865

-

揭秘场效应晶体管的使用诀窍,看完这里你就了然于胸2019-03-21 2888

-

场效应晶体管开关电路2010-05-24 12308

-

结型场效应晶体管是什么?2010-03-04 4091

-

场效应晶体管的分类及使用2010-01-13 974

-

什么是场效应晶体管2009-05-24 7683

全部0条评论

快来发表一下你的评论吧 !