Friendly Elec基于Allwinner H5的NanoPi NEO2开发方案

控制/MCU

描述

Friendly Elec公司的NanoPI NEO2是新一代超小型ARM计算机,比奥利奥饼干还要小,比卡片电脑还要快,采用全新64位四核A53处理器H5,内置六核Mail450 GPU,集成512M DDR3内存,可支持运行Ubuntu Core, Armbian等嵌入式操作系统.NanoPI NEO2采用了千兆以太网接口,并带有1个标准USB接口,因此非常适合对体积要求高,数据传输量大,数据传输速度快,和更高计算性能的物联网应用;它也是创客们发挥创意的绝佳选择.本文介绍了Allwinner H5处理器特性,框图,以及NanoPI NEO2超小型ARM计算机主要特性,框图和电路图.

The Allwinner H5 is a highly cost-efficient quad-core OTT Box processor,which is a part of growing home entertainment products that offer high-performance processing with a high degree of functional integration.

Allwinner H5处理器特性概述:

• CPU: Quad-core ARM CortexTM-A53 Processor, a power-efficient ARM v8 architecture, it has 64 and 32bit execution states for scalable high performance ,which includes a NEON multimedia processing engine.

• Graphics: The hexa-core ARM Mali450 GPU including dual Geometry Processors(GP) and quad Pixel Processors(PP), provides users with superior experience in video playback and mainstream game; OpenGL ES2.0 and OpenVG1.1 standards are supported.

• Video Engine: H5 provides multi-format high-definition video encoder/decoder with dedicated hardware, including H.265 decoder by 4K@30fps , H.264 decoder by 4K@30fps, MPEG1/2/4 decoder by 1080p@60fps, VP8/AVS jizhun decoder by 1080p@60fps, VC1 decoder by 1080p@30fps, H.264 encoder by 1080p@60fps.

• Display Subsystem: Supports DE2.0 for excellent display experience, and two display interfaces for HDMI1.4 and CVBS display.

• Memory Controller: The processor supports many types of external memory devices, including DDR3/DDR3L, NAND Flash(MLC,SLC,TLC,EF),Nor Flash, SD/SDIO/MMC including eMMC up to rev5.1.

• Security System: The processor delivers hardware security features that enable trustzone security system, Digital Rights Management(DRM) ,information encryption/decryption, secure boot, secure JTAG and secure efuse.

• Interfaces: The processor has a broad range of hardware interfaces such as parallel CMOS sensor interface, 10/100/1000Mbps EMAC with FE PHY, USB OTG v2.0 operating at high speed(480Mbps) with PHY, USB Host with PHY and a variety of other popular interfaces(SPI,UART,CIR,TSC,TWI,SCR).

Allwinner H5处理器主要特性:

CPU Architecture

Quad-core ARM CortexTM-A53 MPCoreTM Processor

Thumb-2 Technology

Supports NEON Advanced SIMD(Single Instruction Multiple Data)instruction for acceleration of media and signal processing functions

Supports Large Physical Address Extensions(LPAE)

VFPv4 Floating Point Unit

Independent 32KB L1 Instruction cache and 32KB L1 Data cache

Shared 512KB L2-cache

GPU Architecture

Hexa-core ARM Mali450 GPU

Dual Geometry Processors with 32KB L2 cache

Quad Pixel Processors with 128KB L2 cache

Concurrent multi-core processing

3000Mpix/sec and 163Mtri/sec

Full scene over-sampled 4X anti-aliasing engine with no additional bandwidth usage

OpenGL ES 1.1/2.0 and OpenVG 1.1 support

Memory Subsystem

Boot ROM

On chip ROM

Supports secure and non-secure access boot

Supports system boot from the following devices:

- NAND Flash

- SD/TF card

- eMMC

- Nor Flash

Supports system code download through USB OTG

SDRAM

Compatible with JEDEC standard DDR3/DDR3L SDRAM

Supports clock frequency up to 667MHz(DDR3-1333)

32-bit bus width

Up to 3GB address space

Supports 2 chip selects

16 address signal lines and 3 bank signal lines

Supports Memory Dynamic Frequency Scale(MDFS)

Random read or write operation is supported

NAND Flash

Compliant with ONFI 2.3 and Toggle 1.0

Up to 2 flash chips

8-bit data bus width

Up to 64-bit ECC per 1024 bytes

Supports 1024, 2048, 4096, 8192, 16K bytes size per page

Supports SLC/MLC/TLC flash and EF-NAND memory

Supports SDR, ONFI DDR and Toggle DDR NAND

Embedded DMA to do data transfer

Supports data transfer together with normal DMA

SMHC

Up to 3 SD/MMC host controller(SMHC) interfaces

Complies with eMMC standard specification V5.1, SD physical layer specification V3.0, SDIO card specification V3.0

1-bit or 4-bit data bus transfer mode for SD/TF cards up to 50MHz in SDR mode

1-bit or 4-bit data bus transfer mode for connecting to an external Wi-Fi module up to 150MHz in SDR mode and 50MHz in DDR mode

1-bit ,4-bit or 8-bit data bus transfer mode for MMC cards up to 150MHz in SDR mode or 100MHz in DDR mode

Supports block size of 1 to 65535 bytes

Embedded special DMA to do data transfer

Supports hardware CRC generation and error detection

System Peripherals

Timer

2 on-chip Timers with interrupt-based operation

1 watchdog to generate reset signal or interrupt

Two 33-bit Audio/Video Sync(AVS) Counter to synchronize video and audio in the player

High Speed Timer

1 High Speed Timer with 56-bit counter

56-bit counter that can be separated to 24-bit high register and 32-bit low register

Clock source is synchronized with AHB clock, much more accurate than other timers

RTC

Time,calendar

Counters second,minutes,hours,day,week,month and year with leap year generator

Alarm:general alarm and weekly alarm

One 32KH***anout

GIC

Supports 16 Software Generated Interrupts(SGIs), 16 Private Peripheral Interrupts(PPIs) and 125 Shared Peripheral Interrupts(SPIs)

DMA

Up to 12-channel DMA

Interrupt generated for each DMA channel

Transfers data width of 8/16/32/64-bit

Supports linear and IO address modes

Programs the DMA burst size

Supports data transfer types with memory-to-memory, memory-to-peripheral, peripheral-to-memory

CCU

9 PLLs

Supports an external 24MHz crystal oscillator and an on-chip 16MHz RC oscillator

Supports clock configuration and clock generated for corresponding modules

Supports software-controlled clock gating and software-controlled reset for corresponding modules

PWM

Supports outputting two kinds of waveform: continuous waveform and pulse waveform

0% to 100% adjustable duty cycle

Up to 24MHz output frequency

Thermal Sensor

Temperature Accuracy : ±3℃ from 0℃ to +100℃, ±5℃ from -20℃ to +125℃

Supports over-temperature protection interrupt and over-temperature alarm interrupt

Averaging filter for thermal sensor reading

2 temperature-sensing cell embedded :sensor0 for CPU,sensor1 for GPU

KEYADC

Analog to digital converter with 6-bit resolution for key application

Maximum sampling frequency up to 250 Hz

Supports general key, hold key and already hold key

Supports single , normal and continuous work mode

Message Box

Two users for Message Box instance

Eight Message Queues for the MSGBox instance

Each of Queues could be configured as transmitter or receiver for user

Two interrupts for the MSGBox instance

Register polling for the MSGBox instance

32-bit message width

Four-message FIFO depth for each message queue

Spinlock

32 spinlocks

Two kinds of status of lock register: TAKEN and NOT TAKEN

Crypto Engine(CE)

Supports symmetrical algorithm: AES, DES, TDES

Supports hash algorithm:SHA-1/SHA-224/SHA-256,MD5,HMAC

Supports 160-bit hardware PRNG with 175-bit seed

Supports 256-bit TRNG

Supports ECB,CBC, CTR, CTS modes for AES

Supports ECB, CBC, CTR modes for DES

Supports ECB, CBC, CTR modes for TDES

128-bit, 192-bit and 256-bit key size for AES

Embedded special DMA to do data transfer

Security ID(SID)

Supports 2K-bit EFUSE for chip ID and security application

CPU Configuration

Configure related CPU parameters, including power on, reset, cache, debug, and check the status of CPU

One 64-bit common counter

Display Subsystem

DE2.0

Output size up to 4096x4096

Supports four alpha blending channel for main display, two channel for aux display

Supports four overlay layers in each channel, and has a independent scaler

Supports potter-duff compatible blending operation

Supports input format YUV422/YUV420/YUV411/ARGB8888/XRGB8888/RGB888/ARGB4444/ARGB1555 and RGB565

Supports Frame Packing/Top-and-Bottom/Side-by-Side Full/Side-by-Side Half 3D format data

Supports SmartColor 2.0 for excellent display experience

- Adaptive edge sharping

- Adaptive color enhancement

- Adaptive contrast enhancement and fresh tone rectify

Supports writeback for high efficient dual display

Display Output

Supports HDMI V1.4 output up to 4K@30fps

- Compatible with HDMI 1.4 specification

- Compatible with HDCP 1.2 for HDMI

- Supports EDID block read by DDC

- Supports HPD

- Integrated CEC hardware

- Supports TMDS clock from 27MHz to 297MHz

- Supports RGB888,YUV444 video formats with only 8bit color depth

4K@30Hz

1920 x 1080p@50/60Hz

1920 x 1080p@24Hz

1920 x 1080i@50/60Hz

1280 x 720p@50/60Hz

720 x 480p@60Hz

720 x 576p@50Hz

3D Frame Packing 1920 x 1080p@24Hz

- Supports L-PCM audio format

Up to 192KHz IEC-60958 audio sampling rate

Maximum 24bit, 8 channel

- Supports IEC-61937 compressed audio format

Supports TV CVBS output

- Standard NTSC-M and PAL-B,D,G,H,I output

- Plug status auto detecting

Video Engine

Video Decoder

Supports multi-format video playback, including:

- H.265 MP/L5.0: 4K@30fps

- H.264 BP/MP/HP Level4.2: 4K@30fps

- H.263 BP: 1080p@60fps

- MPEG1 MP/HL: 1080p@60fps

- MPEG2 MP/HL: 1080p@60fps

- MPEG4 SP/ASP L5: 1080p@60fps

- Sorenson Spark: 1080p@60fps

- VP8 N/A: 1080p@60fps

- VC1 SP/MP/AP: 1080p@30fps

- AVS/AVS+ jizhun: 1080p@60fps

- xvid N/A: 1080p@60fps

- MJPEG: 1080p@30fps

Supports 1080p blu-ray 3D

Supports 3D size:3840x1080,1920x2160

Supports decoding output format:YV12

Video Encoder

Supports H.264 video encoder up to 1080p@60fps

Supports input picture size up to 4800x4800

Supports input format: tiled (128x32)/YU12/YV12/NU12/NV12/ARGB/YUYV

Supports Alpha blending

Supports thumb generation

Supports 4x2 scaling ratio: from 1/16 to 64 arbitrary non-integer ratio

Supports rotated input

Image Subsystem

CSI

Supports 8-bit YUV422 CMOS sensor interface

Supports CCIR656 protocol for NTSC and PAL

Up to 5M pixel camera sensor

Supports video capture resolution up to 1080p@30fps

Audio Subsystem

Audio Codec

Two audio digital-to-analog(DAC) channels

- 100 ± 3 dB SNR@A-weight

- Supports ADC sample rate from 8 KHz to 192 KHz

Two audio analog-to-digital(ADC) channels

- 93 ± 3 dB SNR@A-weight

- Supports ADC sample rate from 8 KHz to 48 KHz

Supports analog/ digital volume control

Supports Dynamic Range Controller(DRC) adjusting the DAC playback output

Supports Dynamic Range Control(DRC) adjusting the ADC recording input

Three audio inputs:

- Two differential microphone inputs

- One stereo Line-in L/R channel input

One audio output: Stereo line-out L/R channel output

I2S/PCM

2 I2S/PCM controllers

Compliant with standard Inter-IC sound(I2S) bus specification

Compliant with left-justified, right-justified, PCM mode, and TDM(Time Division Multiplexing) format

Supports 8-channel in TDM mode

Full-duplex synchronous work mode

Mater and slave mode configured

Clock up to 100 MHz

Adjustable audio sample resolution from 8-bit to 32-bit

Sample rate from 8 KHz to 192 KHz

Supports 8-bit u-law and 8-bit A-law companded sample

Supports programmable PCM frame width:1 BCLK width(short frame) and 2 BCLKs width(long frame)

One 128 depth x 32-bit width FIFO for data transmit, one 64 depth x 32-bit width FIFO for data receive

Programmable FIFO thresholds

One Wire Audio(OWA)

IEC-60958 transmitter functionality

Compliance with S/PDIF Interface

Supports channel status insertion for the transmitter

Hardware parity generation on the transmitter

One 32×24 bits FIFO (TX) for audio data transfer

Programmable FIFO thresholds

External Peripherals

USB

One USB 2.0 OTG,with integrated USB PHY

- Complies with USB2.0 Specification

- Supports High-Speed (HS,480Mbps),Full-Speed(FS,12Mbps) and Low-Speed(LS,1.5Mbps) in host mode

- Complies with Enhanced Host Controller Interface(EHCI)Specification, Version 1.0, and the Open Host Controller Interface(OHCI) Specification, Version 1.0a for host mode

- Up to 8 User-Configurable Endpoints in device mode

- Supports point-to-point and point-to-multipoint transfer in both host and peripheral mode

Three USB Host, with integrated USB PHY

- Complies with Enhanced Host Controller Interface(EHCI)Specification, Version 1.0, and the Open Host Controller Interface(OHCI) Specification, Version 1.0a.

Ethernet

Integrated an internal 10/100M PHY

Supports 10/100/1000Mbps data transfer rate

Supports MII/RGMII/RMII interface

Supports full-duplex and half-duplex operation

Programmable frame length

Automatic CRC and pad generation controllable on a per-frame basis

Options for Automatic Pad/CRC Stripping on receive frames

Programmable frame length to support Standard or Jumbo Ethernet frames with sizes up to 16 KB

Programmable Inter Frame Gap (40-96 bit times in steps of 8)

Supports a variety of flexible address filtering modes

CIR

A flexible receiver for IR remote

Programmable FIFO threshold

UART

Up to 5 UART controllers, one UART for CPUx debug, one UART for CPUs debug, others for UART applications

UART0: 2-wire; UART1/2/3: 4-wire; S_UART: 2-wire

Compliant with industry-standard 16450 and 16550 UARTs

Supports word length from 5 to 8 bits, an optional parity bit and 1,1.5 or 2 stop bits

Programmable parity(even, odd and no parity)

64-byte Transmit and receive data FIFOs for all UART

SPI

Up to 2 SPI controllers

Full-duplex synchronous serial interface

Master/Slave configurable

Mode0~3 are supported for both transmit and receive operations

Two 64-byte FIFO for SPI-TX and SPI-RX operation

DMA-based or interrupt-based operation supported

Polarity and phase of the chip select(SPI_SS) and SPI_Clock(SPI_SCLK) are configurable

The maximum frequency is 100MHz

Supports single and dual read mode

TWI

Up to 4 TWI(Two Wire Interface) controllers

Supports Standard mode(up to 100K bps) and Fast mode(up to 400K bps)

Master/Slave configurable

Allows 10-bit addressing transactions

Perform arbitration and clock synchronization

Allows operation from a wide range of input clock frequencies

TSC

Up to 4 TSC(Transport Stream Controller)

Compliant with the industry-standard AMBA Host Bus(AHB) Specification, Revision 2.0.Supports 32-bit Little Endian bus

Supports DVB-CSA V1.1 Descrambler

One external Synchronous Parallel Interface(SPI) or one external Synchronous Serial Interface(SSI)

Configurable SPI and SSI timing parameters

Hardware packet synchronous byte error detecting

Hardware PCR packet detecting

SCR

Up to 2 SCR(Smart Card Reader) controllers

Supports APB slave interface for easy integration with AMBA-based host systems

Supports the ISO/IEC 7816-3:1997(E) and EMV2000 (4.0) Specifications

Supports adjustable clock rate and bit rate

Configurable automatic byte repetition

Supports asynchronous half-duplex character transmission and block transmission

Supports synchronous and any other non-ISO 7816 and non-EMV cards

Performs functions needed for complete smart card sessions, including:

- Card activation and deactivation

- Cold/warm reset

- Answer to Reset (ATR) response reception

- Data transfers to and from the card

Package

FBGA 347 balls, 0.65mm ball pitch, 14mm x 14mm

图1.Allwinner H5处理器框图

NanoPI NEO2是友善之臂团队(Friendly Elec)推出的全新一代超小型ARM计算机,它采用全志64位四核A53处理器H5, 内置六核Mail450 GPU, 集成512M DDR3内存,可支持运行Ubuntu Core,Armbian等嵌入式操作系统。NEO2依然小巧精致,尺寸如一,并且和第一代NEO接口兼容。

更为惊人的是,在极其有限的空间里,NEO2采用了千兆以太网接口,并带有1个标准USB接口,因此非常适合对体积要求高,数据传输量大,数据传输速度快,和更高计算性能的物联网应用;它也是创客、高端极客们发挥创意的绝佳选择。

NanoPI NEO2超小型ARM计算机主要特性:

The NanoPI NEO2 is a newly released super tiny ARM board by FriendlyElec. It uses Allwinner’s 64-bit H5 quad-core SoC (ARM Cortex-A53). It has internal hexa-core Mail450 GPU, 512M DDR3 RAM. AUbuntuCore and Armbian image files are ready for it.

The NanoPi NEO2 inherits NEO’s form factor and has compatible interfaces and ports with NEO. In addition in such a small dimension it has Gbps Ethernet and one USB host port. These features make it especially suitable for applications that require high data throughput , speedy data transmission and high performance. Hobbyists and makers will just love it.

硬件指标:

CPU: Allwinner H5, Quad-core 64-bit high-performance Cortex A53

DDR3 RAM: 512MB

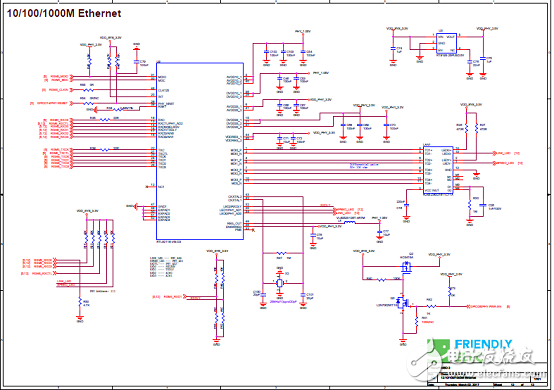

网络:10/100/1000M 以太网口, 采用RTL8211E-VB-CG网络传输芯片

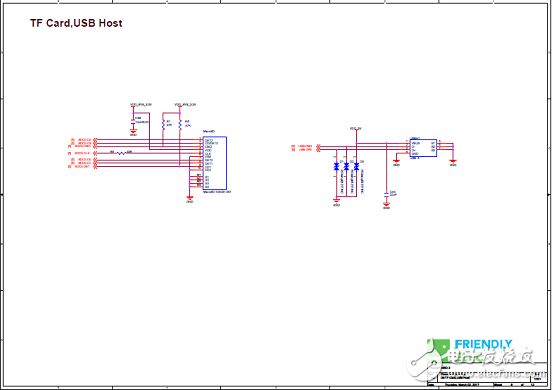

USB Host: 3路,其中1路为标准A型口,另外2路位于GPIO2

MicroSD Slot:1个, 支持启动和存储系统

指示灯: 2个, 分别用于电源, 和系统状态(蓝色)

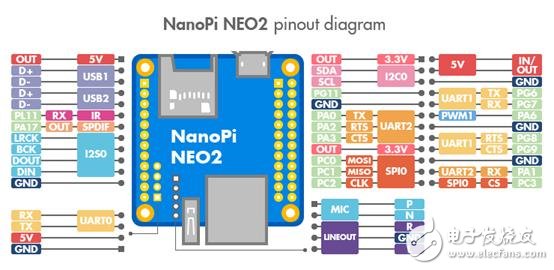

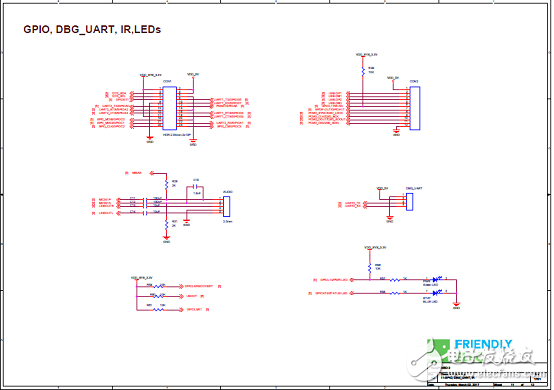

GPIO1: 24pin, 2.54mm间距双排针,兼容树莓派GPIO之管脚1-24,含UART, SPI, i2c, IO等管脚资源

GPIO2: 12pin, 2.54mm间距双排针, 含USB, 红外接收, I2S, IO等管脚资源

调试串口: 4Pin, 2.54mm间距单排针

音频输入和输出: 5Pin, 2.0mm间距单排针

PCB Size: 40 x 40mm

MicroUSB: 供电(5V/2A),并具备OTG功能

OS/Software: u-boot,Ubuntu Core

Weight: 13g(WITHOUT Pin-headers)

CPU: Allwinner H5, Quad-core 64-bit high-performance Cortex A53

DDR3 RAM: 512MB

Connectivity: 10/100/1000M Ethernet, RTL8211E-VB-CG chip

USB Host: USB Type A x 1 and USB pin header x 2

MicroSD Slot: MicroSD x 1 for system boot and storage

LED: Power LED x 1, System LED(Blue) x 1

GPIO1: 2.54mm pitch 24 pin-header, compatible with Raspberry Pi’s GPIO pin1 - pin 24. It includes UART, SPI, I2C, IO etc

GPIO2: 2.54mm pitch 12 pin-header. It includes USB, IR receiver, I2S, IO etc

Serial Debug Port: 2.54mm pitch 4pin-header

Audio In/Out: 2.0mm pitch 5 pin-header

MicroUSB: Power input(5V/2A) and OTG

PCB Dimension: 40 x 40mm

Working Temperature: -30℃ to 70℃

Weight: 13g(WITHOUT Pin-headers)

OS/Software: u-boot,Ubuntu Core

软件特性:

uboot

mainlineuboot released on May 2017

UbuntuCore 16.04

64-bit system

mainline kernel: Linux-4.11.2

rpi-monitor: check system status and information

npi-config: system configuration utility for setting passwords, language, timezone, hostname, SSH and auto-login,and enabling/disabling i2c, spi, serial and PWM. When enabling PWM it will prompt that Serial debug port will be disabled.

software utility: wiringNP to access GPIO pins

software utility: RPi.GPIO_NP to access GPIO pins

networkmanager: manage network

system log output from serial port

supports USB WiFi module: refer to #Connect USB WiFi to NEO

supports audio recording and playing with 3.5mm audio jack

supports I2C 0/1

fixed MAC address

Ubuntu OLED

mainline kernel: Linux-4.11.2

supportsFriendlyElec’s OLED module

图2.NanoPI NEO2超小型ARM计算机外形图

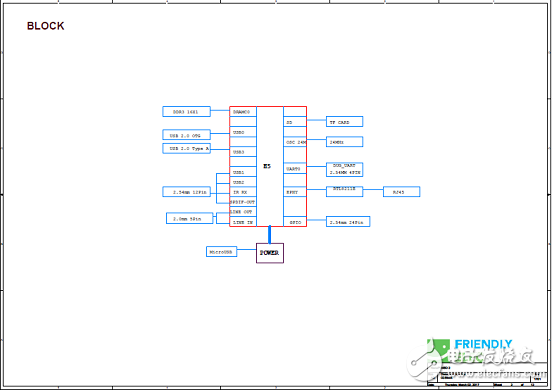

图3.NanoPI NEO2超小型ARM计算机框图

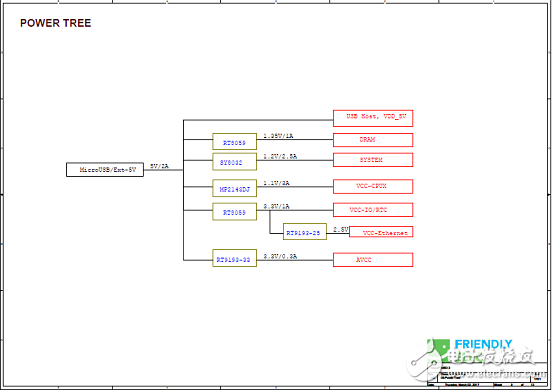

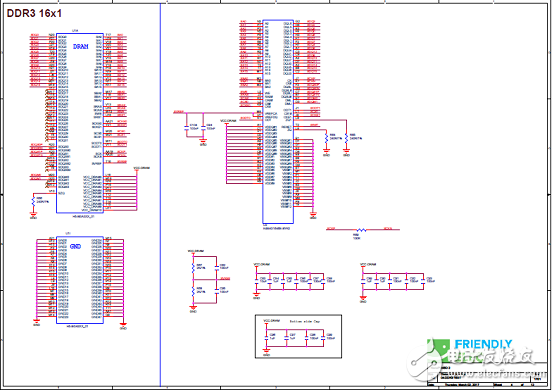

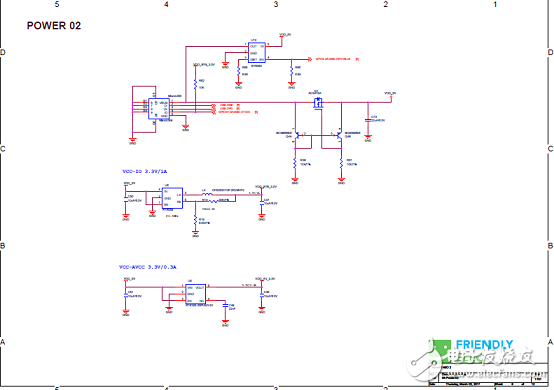

图4.NanoPI NEO2超小型ARM计算机电路图(1)

图5.NanoPI NEO2超小型ARM计算机电路图(2)

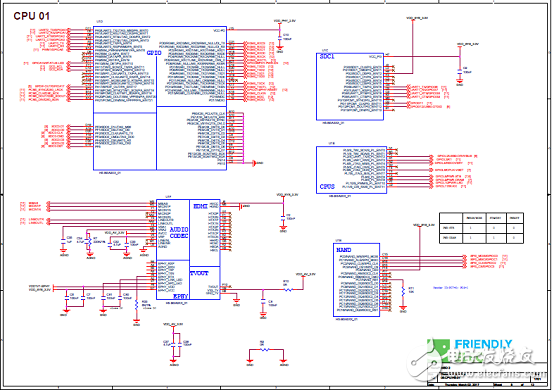

图6.NanoPI NEO2超小型ARM计算机电路图(3)

图7.NanoPI NEO2超小型ARM计算机电路图(4)

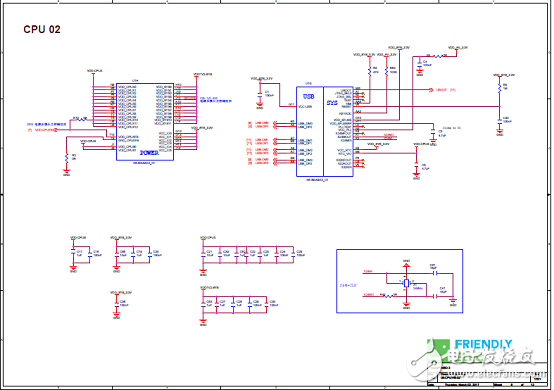

图8.NanoPI NEO2超小型ARM计算机电路图(5)

图9.NanoPI NEO2超小型ARM计算机电路图(6)

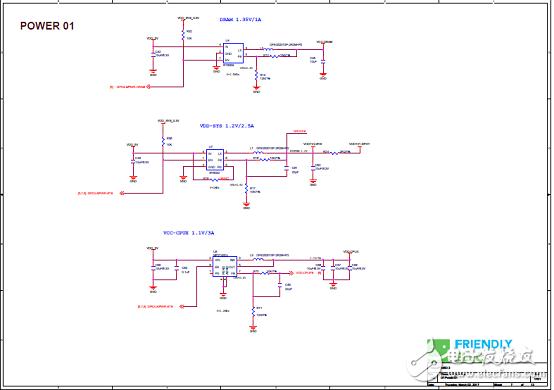

图10.NanoPI NEO2超小型ARM计算机电路图(7)

图11.NanoPI NEO2超小型ARM计算机电路图(8)

图12.NanoPI NEO2超小型ARM计算机电路图(9)

图13.NanoPI NEO2超小型ARM计算机电路图(10)

- 相关推荐

-

友善超小NanoPi NEO2,全志H5,64位四核A53开发板,运行UbuntuCore2017-03-14 0

-

NanoPi NEO2开发套件免费试用2017-05-08 0

-

1-bay NAS Dock v1.2 for NanoPi NEO/NEO22017-05-12 0

-

【NanoPi NEO2试用申请】智能家庭控制器2017-05-31 0

-

【NanoPi NEO2试用体验】[NanoPi NEO2测试实验] 0、开箱感受2017-06-06 0

-

【NanoPi NEO2试用体验】开箱上电2017-06-07 0

-

【NanoPi NEO2试用体验】网络分享-ssh登陆2017-06-08 0

-

【NanoPi NEO2试用体验】开箱体验2017-06-12 0

-

【NanoPi NEO2试用体验】NEO2搭建samba服务2017-06-14 0

-

【NanoPi NEO2试用体验】Linux内核编译运行2017-06-24 0

-

友善NanoPi NEO Plus2,全志H5,千兆网口,IoT开发板,WiFi蓝牙2017-07-04 0

-

NanoPi NEO Plus2开发板免费试用2017-07-17 0

-

NanoPi NEO2创客秘籍2017-08-28 0

-

请问NanoPi NEO2稳定性怎么样?2019-04-01 0

-

nanopi neo2应用指南2023-10-20 312

全部0条评论

快来发表一下你的评论吧 !