与门真值表和与非门真值表的区别

芯片引脚图

描述

与门真值表

与门(英语:AND gate)又称“与电路”、逻辑“积”、逻辑“与”电路。是执行“与”运算的基本逻辑门电路。有多个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

基本功能及真值表

与门是实现逻辑“乘”运算的电路,有两个以上输入端,一个输出端(一般电路都只有一个输出端,ECL电路则有二个输出端)。只有当所有输入端都是高电平(逻辑“1”)时,该电路输出才是高电平(逻辑“1”),否则输出为低电平(逻辑“0”)。[1] 其二输入与门的数学逻辑表达式:Y = AB,对应的真值表如下

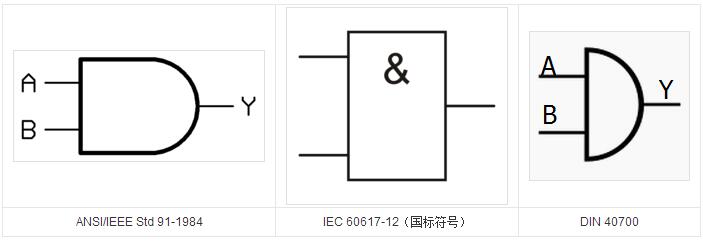

逻辑符号

与门有3种逻辑符号,包括:形状特征型符号(ANSI/IEEEStd 91-1984)、IEC矩形国标符号(IEC 60617-12)、DIN符号(DIN 40700)。

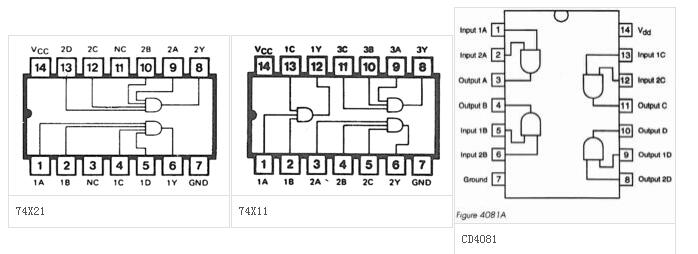

集成电路

与门是基本的逻辑门,因此在TTL和CMOS集成电路中都是可以使用的。标准的74系列CMOS集成电路有74X08、74X09(OC),包含四个独立的2输入与门;74X11,包含三个独立的3输入与门;74X21,包含两个独立的4输入与门。CD4000系列集成电路有:CD4081,包含四个2输入端与门;CD4082,包含两个4输入端与门。

引脚分配如下:

与非门真值表

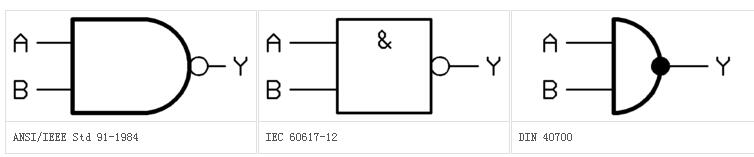

与非门是与门和非门的结合,先进行与运算,再进行非运算。与非运算输入要求有两个,如果输入都用0和1表示的话,那么与运算的结果就是这两个数的乘积。如1和1(两端都有信号),则输出为0;1和0,则输出为1;0和0,则输出为1。与非门的结果就是对两个输入信号先进行与运算,再对此与运算结果进行非运算的结果。简单说,与非与非,就是先与后非。

电工学里一种基本逻辑电路,是与门和非门的叠加,有两个输入和一个输出。

CMOS电路中的逻辑门有非门、与门、与非门、或非门、或门、异或门、异或非门,施密特触发门、缓冲器、驱动器等。

与非门则是当输入端中有1个或1个以上是低电平时,输出为高电平;只有所有输入是高电平时,输出才是低电平。与非门芯片:74ls系列:74ls00、74LS20,CMOS系列:CD4011

与非门真值表

逻辑符号

与门真值表和与非门真值表的区别

与门真值表:有0出0,全1出1

与非门真值表:有0出1,全1出0

- 相关推荐

- 热点推荐

-

怎么利用QuartuesII查元件真值表2012-11-15 3389

-

74LS00芯片资料及真值表2012-12-07 22122

-

怎么利用QuartusII查元件真值表2012-12-20 7430

-

求常用单片机的功能表、引脚图、真值表2013-04-25 3258

-

关于多位输入真值表的问题2013-07-11 2538

-

帮忙看下,我仿真出来的怎么和真值表不一样啊,是不是.....2013-10-08 3824

-

输入真值表相同 输出结果不同 74HC1382014-10-26 8686

-

与非门可以去掉吗?2015-11-14 5972

-

LUT真值表在实施期间发生了变化2018-11-01 2747

-

利用74LS00二输入与非门实现“与电路”?2020-11-04 9974

-

LUT与真值表有何关系2021-11-02 3617

-

7406的引脚功能及真值表2008-02-28 22207

-

真值表,真值表是什么意思2010-03-08 29850

-

与门真值表2011-03-20 27588

全部0条评论

快来发表一下你的评论吧 !