jk边沿触发器工作原理

电子常识

描述

JK触发器简介

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

JK触发器工作特性

建立时间:是指输入信号应先于CP信号到达的时间,用tset表示。由图7.5.5可知,J、K信号只要不迟于CP信号到达即可,因此有tset=0。保持时间:为保证触发器可靠翻转,输入信号需要保持一定的时间。保持时间用tH表示。如果要求CP=1期间J、K的状态保持不变,而CP=1的时间为tWH,则应满足:tH≥tWH。

传输延迟时间:若将从CP下降沿开始到输出端新状态稳定地建立起来的这段时间定义为传输时间,则有:tPLH=3tpdtPHL=4tpd最高时钟频率:因为主从触发器都是由两个同步RS触发器组成的,所以由同步RS触发器的动态特性可知,为保证主触发器的可靠翻转,CP高电平的持续时间tWH应大于3tpd。同理,为保证从触发器能可靠地翻转,CP低电平的持续时间tWL也应大于3tpd。因此,时钟信号的最小周期为:Tc(min)≥6tpd最高时钟频率fc(max)≤1/6tpd。

如果把图7.5.5的J、K触发器接成T触发器使用(即将J和K相连后接至高电平),则最高时钟频率还要低一些。因为从CP的下降沿开始到输出端的新状态稳定建立所需要的时间为tPHL≥4tpd,如果CP信号的占空比为50%,那么CP信号的最高频率只能达到fc(max)=1/2tPHL=1/8tpd。

边沿JK触发器的特点

①边沿触发,无一次变化问题。

②功能齐全,使用方便灵活。

③抗干扰能力极强,工作速度很高。

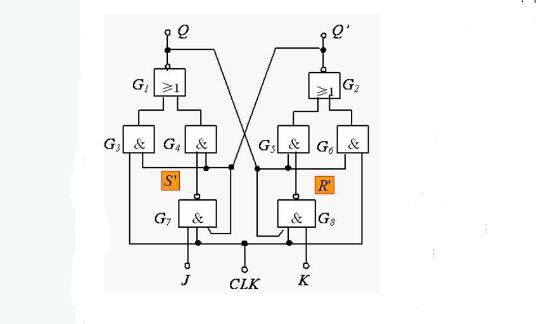

边沿JK触发器工作原理

(1)CLK=1时,有:

则触发器状态保持不变,此时G7、GS的输出为:

此将作为触发器状态转移的准备条件。

(2)CLK由1跳变到0时,CLK首先封锁了G3、使其输出为0,这样由余下的门就构成类似两个与非门组成的钟控JK触发器

则:

此时触发器将具有JK触发器的功能。

此后G7G8 J被CLK= =0封锁,输出为1,触发器犬态维持不变,触发器在完成一次状态转移后,不再发生多次翻转现象。

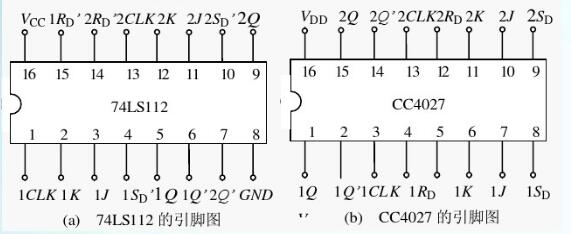

集成边沿式JK触发器

1、74LS112为CLK 下降沿触发

2、CC4027为CLK 上升沿触发且其异步输入端RP和SP为高电平有效。

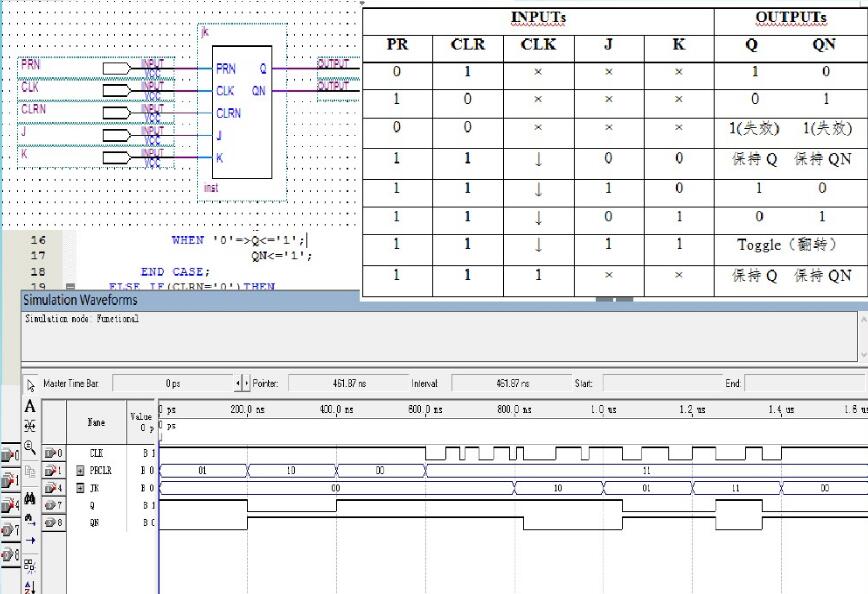

边沿式JK触发器设计及波形仿真

-

jk触发器和t触发器的工作原理、特点和应用2024-08-28 8595

-

主从jk触发器和边沿jk触发器的区别2024-08-22 7394

-

同步触发器和边沿触发器的区别2024-08-12 3495

-

主从jk触发器工作原理2019-08-05 43655

-

什么是边沿触发器_边沿D触发器介绍2018-01-31 73116

-

jk触发器是什么原理_jk触发器特性表和状态转换图2017-12-25 192315

-

JK触发器,JK触发器是什么意思2010-03-08 7448

-

CMOS触发器的结构与工作原理2009-10-17 7942

-

主从jk触发器电路及工作原理2008-01-21 18333

全部0条评论

快来发表一下你的评论吧 !