时序逻辑电路分析有几个步骤(同步时序逻辑电路的分析方法)

数字电路图

描述

分析时序逻辑电路也就是找出该时序逻辑电路的逻辑功能,即找出时序逻辑电路的状态和输出变量在输入变量和时钟信号作用下的变化规律。上面讲过的时序逻辑电路的驱动方程、状态方程和输出方程就全面地描述了时序逻辑电路的逻辑功能。

因此,只要写出时序逻辑电路的这3组方程,它的逻辑功能也就描述清楚了。但是用3组方程描述电路的逻辑功能非常不直观,不能直接看出电路状态和输出变量的与输入变量和时钟信号之间的对应关系,为了直观地描述时序电路的逻辑功能,还有其他的表示方法:状态转换表、状态转换图和时序图。下面结合时序电路的分析,具体介绍这3种时序电路逻辑功能的描述方法。

由于触发器电路中的触发器元件动作特点不同,在时序逻辑电路中又分为同步时序逻辑电路和异步时序逻辑电路。在同步时序逻辑电路中,各触发器状态的变化都是在同一时钟脉冲的作用下同时发生的。而在异步时序逻辑电路中,各触发器状态的变化不是同时发生的。

时序逻辑电路分析步骤

第一步:分析电路结构,写出各触发器的驱动方程。

第二步:将驱动方程代入相应触发器的特性方程,求得各触发器的次态方程,也就是时序逻辑电路的状态方程。

第三步:根据电路图写出输出方程。

第四步:根据状态方程和输出方程,列出该时序带电路的状态表,画出状态图或时序图。

时序逻辑电路的分析举例

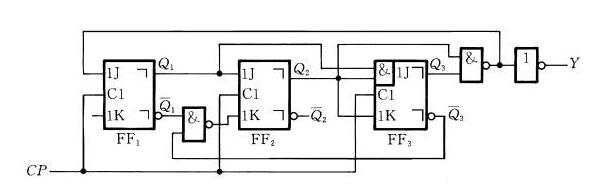

图一就是一个时序逻辑电路图,下面以此为例介绍同步时序电路的分析方法:

第一步:分析电路结构,写出各触发器的驱动方程

该时序电路包含3个触发器FF1,FF2,FF3,这3个触发器都是上升沿触发的边沿JK触发器,而且它们的时钟脉冲相同,都是CP脉冲,即3个触发器的触发时刻都是CP脉冲的上升沿,因此该时序电路是同步的。该时序电路没有输入变量,有输出变量Y。

列写方程时,各触发器的输入、输出变量、时钟脉冲分别用相应字母加触发器编号的下角标表示。如FF1触发器的输入、输出变量分别表示为J1、K1、Q1、 ,其时钟脉冲为C1或CP1。其他以此类推。

,其时钟脉冲为C1或CP1。其他以此类推。

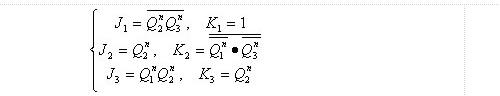

根据电路图写出各个触发器的驱动方程

说明:如果触发器的输入端悬空,则相当于接高电平“1”,故K1=1。FF3触发器的J端有两个输入,它们“与”运算后作为J端的输入,故J3=Q1·Q2。Q1n、Q2n、Q3n表示触发器的现态(原态)。

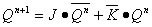

第二步:将驱动方程代入相应触发器的特性方程,求得各触发器的次态方程,也就是时序逻辑电路的状态方程。

将式(1)代入JK触发器的特性方程 ,求得各触发器的次态方程

,求得各触发器的次态方程

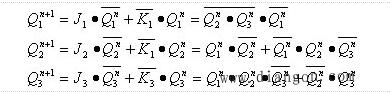

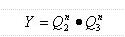

第三步:根据电路图写出输出方程

第四步:根据状态方程和输出方程,列出该时序带电路的状态表,画出状态图或时序图。

为了形象地描述时序逻辑电路的逻辑功能,可以把电路在一系列时钟信号作用下状态转换的全部过程描述出来。描述时序逻辑电路状态转换全部过程的方法有状态转换表、状态转换图和时序图等几种。

同步时序逻辑电路的分析方法

分析时序电路,即找出给定时序电路的逻辑功能

一、分析步骤:

1 、写出驱动方程(即触发器输入信号的逻辑函数式)

2 、写出状态方程(将驱动方程代入相应触发器的特性方程)

3 、写出电路的输出方程(有些电路可能没有输出)

4 、列出状态表(或状态图)

5 、确定电路的逻辑功能

二、例 P227 写出驱动方程、状态方程和输出方程

( 1 )驱动方程  J 2 = Q 1 J 3 = Q 1 Q K 1 1

J 2 = Q 1 J 3 = Q 1 Q K 1 1

K 3 = Q 2

K 3 = Q 2

( 2 )根据 JK 触发器特性方程  写出状态方程

写出状态方程

;

;  ;

;

( 3 )输出方程 Y = Q 2 Q 3

- 相关推荐

- 热点推荐

- 时序逻辑电路

-

时序逻辑电路的功能表示方法有哪些2024-08-28 2348

-

时序逻辑电路有哪些 时序逻辑电路和组合逻辑电路区别2024-02-06 14535

-

时序逻辑电路的相关概念和分析方法2023-06-21 9049

-

时序逻辑电路设计之同步计数器2023-05-22 5740

-

时序逻辑电路的主要故障分析2018-04-09 7018

-

时序逻辑电路由什么组成_时序逻辑电路特点是什么2018-03-01 112409

-

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别2018-01-30 95158

-

时序逻辑电路的分析与设计2016-09-02 1247

-

fpga时序逻辑电路的分析和设计2012-06-20 10041

-

时序逻辑电路2010-08-10 967

-

同步时序逻辑电路2009-09-01 1160

-

时序逻辑电路分析实例2009-04-07 5089

全部0条评论

快来发表一下你的评论吧 !