集成最新的接口IP以优化功耗、成本和上市时间势在必行

连接器

描述

在未来两年内将有望继续扩大的低成本智能手机正在推动着整个智能手机市场的发展,智能手机在新兴市场中的广泛采用和在成熟市场中替换功能机或基本型手机都是这个市场发展的推动因素。细分的低成本智能手机使多家移动手机设备制造商能够进入智能手机市场,这些制造商通过在高端和低端细分市场中与排名第一的手机供应商三星电子(Samsung)竞争,缩小了他们之间的差距。

在这些市场中竞争的设备制造商必须提供高性价比的智能手机,并且需要在其旗舰型智能手机产品之下提供一档或两档让人满意的功能集。对于低成本智能手机设备,诸如防水型设备或再添加一个心跳感应器并使用高性能存储都不是必须特性。然而,拥有高质量的前置、后置摄像头和一个高分辨率的显示屏则都是关键功能—用户期望在他们的低成本智能手机中也拥有它们。

要为新兴和成熟市场中的新用户提供低成本、高质量的智能手机,制造商必须要有高集成度的硬件芯片(IC),这些芯片以一种高性价比的方式提供必须具备的高端功能。

因此,智能手机器件制造商必须投资于系统集成,降低硬件成本。降低芯片成本给应用处理器供应商带来了压力,他们被要求在智能手机中尽可能集成许多系统元器件,并在特定的价格范围内为低成本智能手机的子细分市场打造最优化的系统级芯片(SoC)。

在致力于降低成本和功耗的同时,设计师必须不断推动设计创新迈向新的天地。因此,集成最新的接口IP以优化功耗、成本和上市时间势在必行。

摄像头和显示屏的接口协议

由移动行业处理器接口(MIPI)联盟基于MIPI D-PHY制定的摄像头串行接口(CSI-2)和显示屏串行接口(DSI)协议被广泛应用于移动设备中,该协议为低成本智能手机细分市场提供了一套灵活的、高性价比的解决方案;而D-PHY是在MIPI CSI-2和DSI应用中把图像传感器和显示屏与移动手机和嵌入式应用中的SoC连接在一起的物理层。它们是应用处理器和显示屏(使用DSI协议)或摄像头和图像传感器(使用CSI-2协议)之间的事实标准接口。MIPI协议专为满足图像传感器和显示应用的功能需求而设计和优化,同时使成本和功耗降到最低。D-PHY经济地实现了高速和低速数据流,它通过物理层-协议接口(PPI)连接实现了协议层的连接。

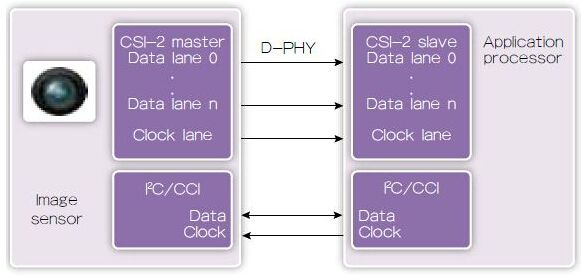

如图1所示,CSI-2是一条用于移动应用的高性能串行互连总线,它把摄像头传感器连接到数字图像模块,如主处理器或图像处理器。CSI-2使用MIPID-PHY来作为物理层和高速差分接口,通常带有好几条数据通道(典型的是1、2、4或甚至是8条)和一条普通差分时钟通道。出于配置的目的,一个基于I2C的边带摄像头控制接口(CCI)被用来连接控制主机和摄像头之间的信号。CSI-2协议支持应用处理器、摄像头传感器和桥接应用中所需的主机和设备接口。

图1:MIPI摄像头串行接口(CSI-2)。

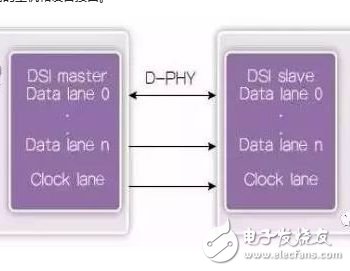

图2:MIPI显示屏串行接口(DSI)

如图2所示, DSI是一条高速、高分辨率的串行互联总线, 它为显示设备提供连接。DSI使用MIPI标准D- PHY 来作为物理层高速差分接口,带有多达4条数据通道和一条普通差分时钟通道。像素数据和指令被串行化送到一个单独的物理流中,而状态能够从显示中读回。该协议支持应用处理器、显示面板和桥接应用中所需的主机和设备接口。它也支持运行在视频模式和指令模式中的显示设备, 因为在更复杂和更低功耗实现中的需求依赖于系统实现和应用。当显示面板上集成了显示控制器和帧缓冲器时, 就需要指令模式。转换通常是以一条指令接着数据像素/参数的形式发生。在指令模式中, 主机可写入和读出面板寄存器和帧缓冲器, 而在视频模式中转换时,像素数据就被实时地从主机转到面板。

推动更高的数据速率

当今市场上大多数可供使用的图像和显示传感器都是在过去5到7年内开发的,支持每条通道高达1,000 Mbps的高速突发模式。有好几款设备都已量产,并支持超过1,000Mbps的速率,因为其目标是在相同数量的连接触点上增加带宽。

近期发布的MIPI联盟D- PHYv1.2规范把D-PHY的高速突发功能扩展到了每条通道2.5Gbps。显示屏和图像传感器的开发人员们现在可以充分利用相同的设计和架构,来使用四条数据通道支持高达10Gbps的聚合宽带,或使用八条数据通道仅需稍作改动来支持20Gbps的数据速率。使用长期存在的、已验证过的、由多家供应商开发的且不断完善的架构,提供了一种快速而低风险的方式,来达到想要的带宽、上市时间和低成本的目标。

推动更低功耗

D-PHY的可扩展性有助于节省功耗。它使用了许多可选的数据通道,并关闭了未使用的数据通道。在大部分情况下, 数据通道为了高速传输都运行在单向模式下,此时一个Mas terD-PHY和Slave D-PHY分别源发送和接收时钟。例如,SoC侧实现的一个DSI主机应用使用了一个MasterD-PHY来在板上作为源将信号发送给显示屏,同时CSI-2主机应用使用一个Slave D-PHY来从图像传感器接收信号。

因为D-PHY不绑定在某个特定速率上,它可在寻找一个时钟信号时基于产生的流量来优化功耗,该时钟信号与实际需要的数据速率相关。这种灵活性通过消除对不必要的存储器缓存的需求和设计复杂性,创造了一种高性价比的解决方案。除此之外,DPHY支持高、低速(或低功率)运行。高速传输使用了时钟通道,而低功率运行模式使用自带时钟数据以节省功率,同时时钟通道保持空闲。

推动更低的成本

MIPID-PHY v1.2规范包括为更高带宽图像和显示传感器提供各种吞吐量的增强,但是它也有助于降低成本。

能够用较少数据通道发送相同数量数据的能力有助于降低芯片的面积和使用更少的引脚,它们都直接与应用处理器的芯片成本相关。应用处理器需要以4 Gbps的速率与一个图像传感器连接, 可以使用两条运行在2.0Gbps的数据通道,而不是四条运行在1.0Gbps的数据通道。当这种减少通道和引脚数量的方法被用于好几个图像传感器时,将显著降低芯片和封装成本。

总结

Synopsys的DesignWare MIPI IP已经使许多SoC 开发人员能够通过使用D-PHY 、CSI-2和DSIIP来实现量产。Design Ware MIPID-PHYv1.2 IP显著地降低了面积、成本和功耗。该IP把产品上市时间缩到最短,同时可针对CSI-2和DSI应用利用其可配置性选项和丰富的解决方案而使投资回报率达到最高,同时减少了支持多款应用所需的SoC设计数量。

-

面对竞争 Lattice持续优化FPGA成本和功耗2012-08-14 1225

-

FPGA开发如何降低成本,比如利用免费的IP内核2024-04-28 996

-

NB-IoT的芯片为什么功耗低?商用芯片何时上市?2016-12-15 3758

-

利用集成式工业接口数字隔离器减少尺寸与成本2018-10-26 1108

-

科发鑫 IP6808 全集成无线充方案 可过认证 技术支持2019-01-28 1699

-

基于Virtex-5 LXT助力串行背板接口设计2019-04-12 1247

-

基于Virtex-5 LXT的串行背板接口设计2019-04-16 1485

-

应对串行背板接口设计挑战2019-05-05 1591

-

低功耗DFM和高速接口2019-05-20 2027

-

SoC FPGA的电机控制IP模块和经过验证参考设计2019-06-24 3369

-

3G手机射频集成变革势在必行2019-06-26 2231

-

基于Foundation IP的低功耗IoT SoC实现2019-07-26 4467

-

带有接口的时间戳PCF212xAT2020-03-20 1398

-

用接口IP实现HDMI的便携式低功耗方案2010-03-13 572

-

Versal Premium ACAP:在灵活应变的平台上突破性集成功耗优化的网络IP2023-09-15 505

全部0条评论

快来发表一下你的评论吧 !