分层 DFT 流程及步骤介绍

电子说

描述

传统的全芯片 ATPG 正日渐衰退,对于许多现有的和未来的集成芯片器件来说,一项主要挑战就是如何为庞大数量的设计创建测试图案。对于有百万门甚至数亿门的设计,传统上等到设计完成再创建测试图案的方法是不切实际的,产生所有这些图案需要庞大的计算能力和相当多的时间。分层可测试性设计通过在区块或内核上完成了 DFT 插入和图案生成解决了这个问题。这大大减少了图案生成时间和所需的计算资源。它还能让你在设计过程中提前完成大部分 DFT 和图案生成,从而大幅提高可预测性并降低风险。本文将介绍分层 DFT 流程的:插入扫描包装器 (Wrapper)、为内核生成灰盒图像,将内核级图案重定向到集成芯片顶层的简单映射步骤。

二、为什么即插即用是合理的?

即插即用这种方法带来的一个重要好处就是,在设计过程中你可以在内核层面提前完成所有工作。这降低了许多类型的风险,因为任何问题都可以提前解决,让最终芯片测试架构和结果变得更可预见。在内核层面做更多的测试工作还能让各单独的开发团队独立工作,然后向做芯片集成工作的同事交付标准的 DFT 操作和测试图案等数据。此外,一旦设计和图案数据完成,同样的数据可以被重新用于任何使用该内核的芯片设计。即插即用方法同样非常灵活。如果设计出现问题,需要进行工程更改(ECO),那么只需要对进行ECO的内核重新生成测试图案。

三、使用包装器链打造独立内核

分层和内核的即插即用方法的基本要求之一是,确保每个内核可以独立进行测试。DFT 工具可以从内核IO开始,并横穿内核逻辑直到找到第一个寄存器,然后将其包括在包装器链中。这些单元由于同时执行功能性任务和测试任务,因而被称为共享包装器单元。许多设计包含寄存器IO,这样进出内核的信号的时序能得到很好地确定。这使包装器插入变得非常简单。

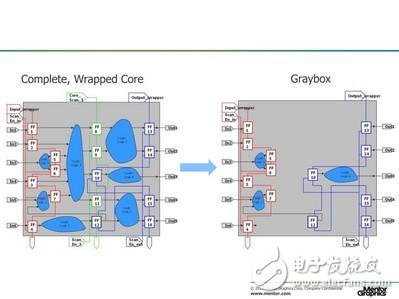

包装器链同时还支持顶层IC建模和规则检查。一旦包装器链被插入,DFT 工具程序可以分析任何内核,并找出IO和包装器链之间存在什么样的逻辑。利用该逻辑,内核的部分图像被写出,我们称之为灰盒(图1)。灰盒被用来验证内核在顶层的连接是否正确(设计规则检查),同时也被用来创建各种内核之间的简单互连测试。

图1:当扫描链插入内核,包装器链的结构允许将内核隔离为一个完整的包装器内核,如左图所示。右图显示了一个灰盒模型,其中顶层测试只需要内核IO和包装器链之间的逻辑。

图1:当扫描链插入内核,包装器链的结构允许将内核隔离为一个完整的包装器内核,如左图所示。右图显示了一个灰盒模型,其中顶层测试只需要内核IO和包装器链之间的逻辑。

四、内核层面的模式生成

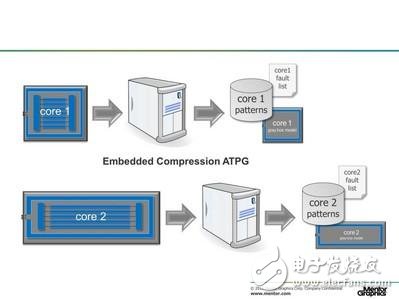

分层DFT的优点是,内核DFT和 ATPG 的进行能够完全独立于其他内核(图2)。即便 IO 值未知,包装器链也能使 ATPG 实现高覆盖率。ATPG 工具只需要得到测试图形将重定向的指示,这样未知值就可以通过IO赋值,同时恰当的数据被存出来,这些恰当的数据包括需要在IC顶层验证的任何时钟或被约束引脚。

图2:利用分层测试方法,所有区块的 ATPG 工作可以在各内核上独立完成。

五、将内核测试图案重定向并整合到顶层

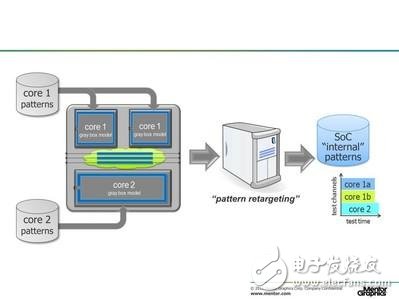

分层 DFT 方法可以便捷地实现顶层IC的测试图案整合。第一步是执行一些基本的DFT设计规则检查(DRC)。完成这一步只需要有顶层网表和所有内核的灰盒模型(图3)。分层DFT方法常常使用IC 层测试访问机制(TAM),将芯片的IO定向到需要测试的特殊区块或区块组。它既可以简单到只需要几个多路复用器,也可以复杂得多。复用的内核通常有并联广播到所有内核的输入信道,这样从一套输入信道就得到同样的测试。我们比较建议将TAM建立在 IJTAG 的基础上,因为IJTAG是一个非常广泛而灵活的标准,也最适用于即插即用。

图3:模式重定向需要独立生成的内核测试图案,并对其进行重新定向,使之可以从IC层执行。这张图显示了被重定向并整合的三个内核测试图案,使其并行执行。对于一个典型的 IC来讲,会有一些区块的测试图案被整合,而另一部分区块需要被放到另一阶段进行测试。

图3:模式重定向需要独立生成的内核测试图案,并对其进行重新定向,使之可以从IC层执行。这张图显示了被重定向并整合的三个内核测试图案,使其并行执行。对于一个典型的 IC来讲,会有一些区块的测试图案被整合,而另一部分区块需要被放到另一阶段进行测试。

分层方法的最后一步是生成测试各内核之间互连的IC层测试图案。灰盒模型在这里被应用。它是设计后期的 ATPG 步骤,因为所有内核设计和 TAM 首先必须在此之前完成。

六、下一步是什么?

分层 DFT的扫描和包装器插入、灰盒生成和测试图案重定向等基本特性为许多设计提供了一个显著优势。但是选择哪些模块并行测试,哪些串行测试,使测试效率得到优化还需要很多做很多工作。有效的顶层规划要求一些内核测试图案信息必须是有效的。与帮助确定最佳压缩配置的压缩分析的功能类似,顶层TAM规划在内核设计可用时更为高效。针对这个问题正在开发的方法之一是将IC信道带宽动态分配给各个内核。这样的话,在设计TAM前就不需要知道内核测试图案的性质。此外,动态分配扫描信道将减少整个测试图案集的大小。

七、报告总结

分层DFT方法正在被许多设计所采用,它显著加快了 ATPG 的速度,降低了工作站的规模。这对于数亿门或以上的超大规模设计来说至关重要。分层DFT 的另一大优点是它很大程度上改进了工序,带来了即插即用的便利。因此,只要内核设计完成,那么更多的DFT和 ATPG 工作可以在设计周期的更早阶段进行,这些都有利于降低风险、提高可预见性、以及后期的 ECO。

-

DFT在信号处理中的应用 DFT与FFT的区别2024-12-20 4777

-

pcb设计一般流程步骤2023-12-13 6204

-

DFT的简单介绍(上)2023-12-06 2853

-

fft和dft的区别联系2023-09-07 9734

-

对DFT数字设计流程的介绍2023-03-06 5555

-

一个典型设计的DFT组件2022-11-30 1715

-

HAB boot的启动流程与实现步骤2022-08-12 2403

-

芯片制造工艺流程步骤2021-12-15 46673

-

采购业务处理流程步骤教程下载2021-09-09 1458

-

利用PADS可测试性设计优化PCB测试点和DFT审核2019-05-14 5105

-

明导:转向使用即插即用的分层DFT2017-12-04 965

-

DFT_DFT设计概述2012-05-30 10386

-

DFT的快速算法-FFT2011-09-07 1403

-

什么是DFT,DFT是什么意思2010-06-07 31688

全部0条评论

快来发表一下你的评论吧 !