解析CD4017集成电路的逻辑功能

芯片引脚图

描述

0、引言

CD4017C集成电路应用非常广泛,但大多资料对其内部电路逻辑功能的推导却是轻描淡写,甚至不乏错误之处,文中通过约翰逊计数器32种随机输出码状态转换的逻辑计算和分析,对CD4017C集成电路内部逻辑电路的结构、原理作了深入详细的阐述。

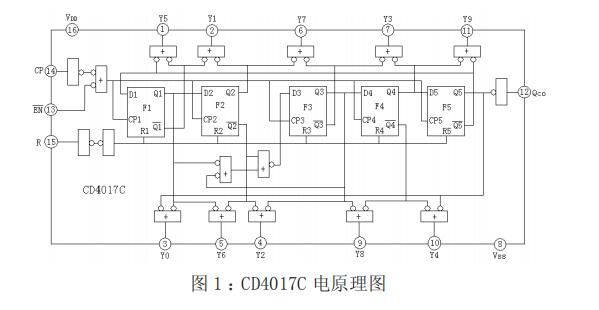

1、CD4017C集成电路的引脚功能(见图1)

CD4017C集成电路共有11个输出端:3脚(Y0)、2脚(Y1)、4脚(Y2)、7脚(Y3)、10脚(Y4)、1脚(Y5)、5脚(Y6)、6脚(Y7)、9脚(Y8)、11脚(Y9)分别为第0~第9输出端;12脚(Qco)为级联进位输出端。3个输入端:13脚(EN)为时钟脉冲输入端,下降沿计数有效;14脚(CP)为时钟脉冲输入端,上升沿计数有效;15脚(R)为复位清零输入端,加高电平或正脉冲时计数器清零。2个供电端:8脚(Vss)为电源负端;16脚(VDD)为电源正端3~18V。

2、十进制约翰逊计数器电路分析(见图1)

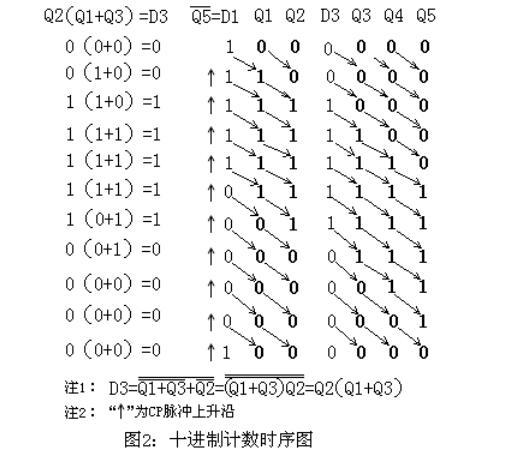

十进制约翰逊计数器实质上是一种串行移位寄存器,由D触发器Fl~F5构成,除了第3个触发器是通过组合逻辑电路作用于F3的D3端以外,其余各级均是将前一级触发器的输出端Q连接到后一级触发器的输入端D的,计数器最后—级F5的 端连接到第一级的D1端。当加上清零脉冲后,Q1~Q5均为“0”,由于Q1的数据输入端D1是Q5输出的反码

端连接到第一级的D1端。当加上清零脉冲后,Q1~Q5均为“0”,由于Q1的数据输入端D1是Q5输出的反码 ,因此,输入第—个时钟脉冲后,Q1即为“l”,这时Q2-Q5均依次进行移位输出,Ql的输出移至Q2,Q2的输出需经组合逻辑电路转化成D3后才能移至Q3,Q3的输出移至Q4,Q4的输出移至Q5,Q5的输出被移出(溢出),如果继续输入脉冲,则Q1为新的

,因此,输入第—个时钟脉冲后,Q1即为“l”,这时Q2-Q5均依次进行移位输出,Ql的输出移至Q2,Q2的输出需经组合逻辑电路转化成D3后才能移至Q3,Q3的输出移至Q4,Q4的输出移至Q5,Q5的输出被移出(溢出),如果继续输入脉冲,则Q1为新的 ,Q2~Q5仍然依次按上述规律移位输出,从而导出十进制计数循环状态(见图2),这就是我们所需十进制计数循环的10种状态。

,Q2~Q5仍然依次按上述规律移位输出,从而导出十进制计数循环状态(见图2),这就是我们所需十进制计数循环的10种状态。

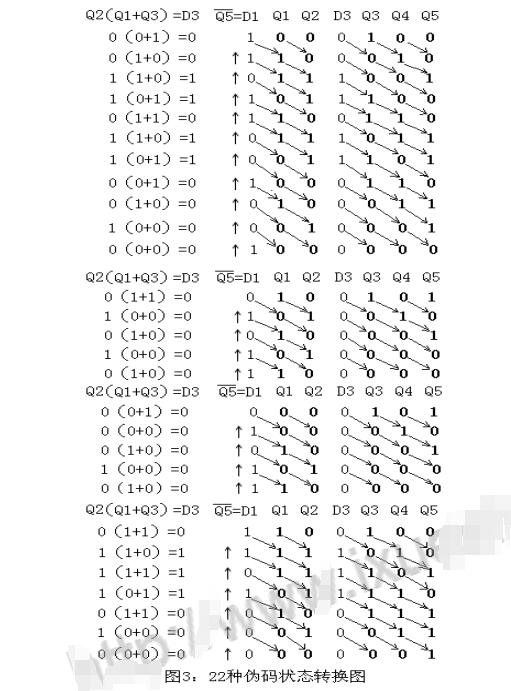

然而由五级计数单元组成的约翰逊计数器,其输出端可以有 =32种组合状态,而构成十进制计数器只需10种计数状态,因此,当电路接通电源之后,有可能进入我们所不需要的22种伪码状态中的任一状态,并伴随触发脉冲上升沿的出现自动进行移位寄存(见图3)

=32种组合状态,而构成十进制计数器只需10种计数状态,因此,当电路接通电源之后,有可能进入我们所不需要的22种伪码状态中的任一状态,并伴随触发脉冲上升沿的出现自动进行移位寄存(见图3)

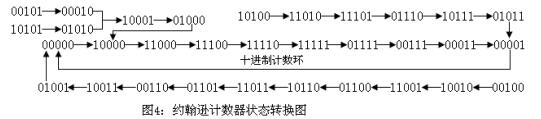

由图3不难看出当电源接通后,即便不清零的话,无论计数单元出现哪种随机组合,最多经过10个时钟脉冲输入之后,都会自动滑入我们所需的图2所列状态中的一种状态。综上所述,可以得到十进制约翰逊计数器总的状态转换图(见图4)

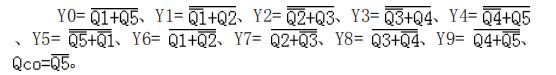

3、时序译码电路分析(见图1)

将每个十进制数对应的Q1Q2Q3Q4Q5代入以上的逻辑表达式,便可算出每个十进制数对应的Y0~Y9、Qco的输出结果(见表1)。

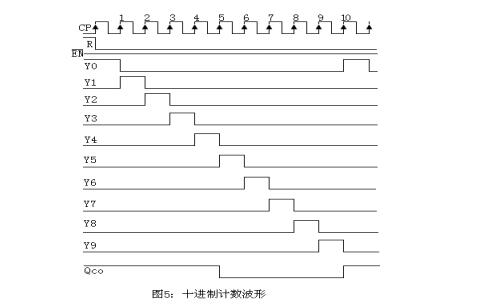

从两个时钟脉冲输入端的内部逻辑电路看,CP1~CP5= ,利用CP上升沿(CP=1)计数时,EN端必须接低电平(EN=0),CP1~CP5才能为上升沿1,反之,利用EN下降沿(EN=0)计数时,CP端必须接高电平(CP=1),CP1~CP5同样才能为上升沿1,CP和EN的其它三种输入组合都使CP1~CP5为0,计数器处于保持状态。在“R”端加上高电平或正脉冲时,计数器中各计数单元F1~F5均被置零,计数器为“00000”状态。CD4017有10个译码输出端Y0~Y9,计数时它会随时钟脉冲的输入而依次出现高电平,见表1。此外,为了级联方便,还设有进位输出端Qco,每输入10个时钟脉冲,就可得到一个进位输出脉冲,所以Qco可作为下一级计数器的时钟信号。从上述分析中可以看出,CD4017的基本功能是对“CP”端输入脉冲的个数进行十进制计数,并按照输入脉冲的个数顺序将脉冲分配在Y0~Y9这十个输出端,计满十个数后计数器复零,同时输出—个进位脉冲(见图5)。

,利用CP上升沿(CP=1)计数时,EN端必须接低电平(EN=0),CP1~CP5才能为上升沿1,反之,利用EN下降沿(EN=0)计数时,CP端必须接高电平(CP=1),CP1~CP5同样才能为上升沿1,CP和EN的其它三种输入组合都使CP1~CP5为0,计数器处于保持状态。在“R”端加上高电平或正脉冲时,计数器中各计数单元F1~F5均被置零,计数器为“00000”状态。CD4017有10个译码输出端Y0~Y9,计数时它会随时钟脉冲的输入而依次出现高电平,见表1。此外,为了级联方便,还设有进位输出端Qco,每输入10个时钟脉冲,就可得到一个进位输出脉冲,所以Qco可作为下一级计数器的时钟信号。从上述分析中可以看出,CD4017的基本功能是对“CP”端输入脉冲的个数进行十进制计数,并按照输入脉冲的个数顺序将脉冲分配在Y0~Y9这十个输出端,计满十个数后计数器复零,同时输出—个进位脉冲(见图5)。

4、结束语

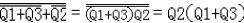

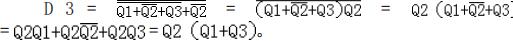

和CD4017C集成电路相互通用的还有CD4017B,两者内部电路略有不同,CD4017B唯一不同于CD4017C的地方是D3的逻辑运算方法稍有不同,但运算的结果是完全一样的,如CD4017C集成电路的D3= ;而CD4017B集成电路的

;而CD4017B集成电路的

- 相关推荐

- 热点推荐

- CD4017

-

集成芯片cd4017的功能2024-03-20 5706

-

cd4017工作原理及应用电路图,introduction of cd40172018-09-20 6570

-

用cd4017顺序开关电路图(cd4017引脚功能及应用电路)2018-04-02 64342

-

cd4017工作原理详解(cd4017引脚图及功能_内部结构及应用电路图)2018-01-31 455062

-

CD4017实现流水灯电路2016-01-11 2495

-

CD4017应用电路2016-01-10 7556

-

CD4017集成电路应用集合2011-09-05 7740

-

CD4017集成电路总汇2011-04-07 3461

-

CD4017组成的充电器电路2009-11-19 2213

-

cd4017内部电路图2009-11-17 3319

-

CD4017组成的电子八音盒电路图2009-09-28 7548

-

CD4017显示电路2008-06-29 2646

全部0条评论

快来发表一下你的评论吧 !