边沿触发器波形图

电子常识

描述

主从触发器可以有效克服钟控触发器的空翻现象,但主从触发器还存在一次翻转现象,降低了抗干扰能力。

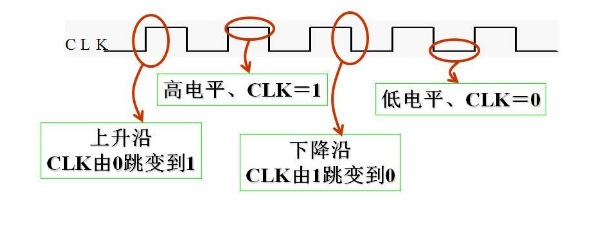

边沿触发器:只有在CP的上升沿(前沿)或下降沿(后沿)时刻才对输入信号响应(不管CP=1的时间有多长)。在CP=0、CP=1期间,输入信号变化不会引起触发器状态的变化。因此触发器不但克服了空翻现象,而且大大的提高了抗干扰能力,工作更为可靠。

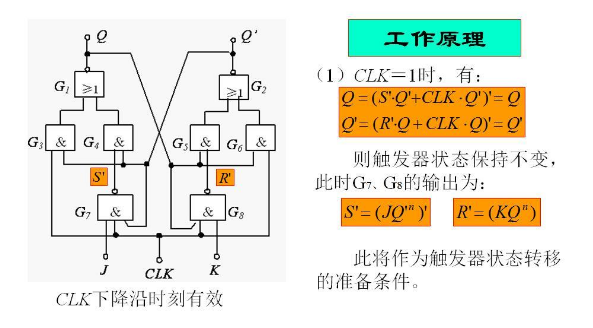

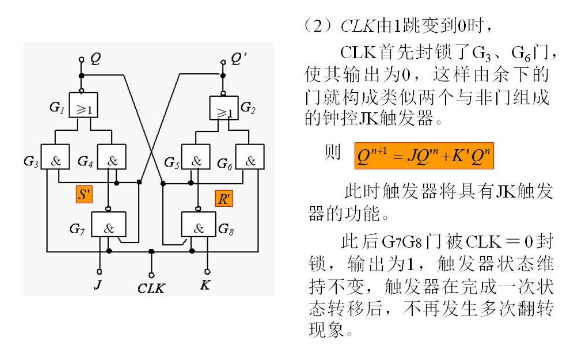

边沿JK触发器

边沿JK触发器不仅可以克服电位触发方式的多次翻转现象,而且仅仅在时钟脉冲CLK的上升沿或下降沿才对激励信号相应,如此可大大提高了抗干扰能力。

边沿JK触发器工作原理

边沿JK触发器的特点

① 边沿触发,无一次变化问题。

② 功能齐全,使用方便灵活。

③ 抗干扰能力极强,工作速度很高。

边沿触发

现在,我们希望CP一直为0或者一直为1的期间都不会触发,只在CP从低到高,或者从高到低变化的瞬间触发。我们即将发明的新型触发器叫做“边沿触发”的D触发器,因为它只在CP脉冲的边沿触发。边沿触发的触发器,实际上还分“上升沿D触发器”和“下降沿D触发器”。

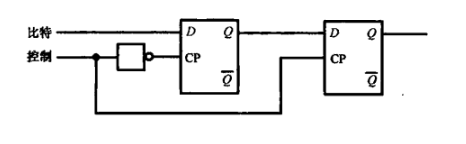

下面只讲前一种,即上升沿D触发器,要制作一个上升沿D触发器,其实很简单,它的秘密在于,可以像下图那样,将两个D触发器首尾相连。

这个大触发器实际上由两个小的D触发器首尾相连而成,前一个触发器的输出是后一个触发器的输入。而且,这两个触发器永远不会同时工作,因为两个触发器的控制脉冲的值是相反的。

如果你想在这个电路里保存一个比特,必须先使控制端为0。这时,左边的触发器CP=1,它可以把任何药保存的比特吃进肚子里,并且立即传送给右边的触发器。但是,很遗憾,右边的触发器不工作。

现在,如果控制器从0跳变到1,说时迟那时快,一起都颠倒了,左边的触发器拒绝再吃掉任何比特,右边的触发器一下子活跃起来,把左边那个触发器的输出保存起来。换句话说,直到这个时候,比特才算是被这个大触发器保存了。

此后,如果控制端从1又回到0,即下降沿,左边的触发器苏醒过来,但右边的触发器却开始休眠,但它仍有能力维持原先的输出不变。也就是说,控制脉冲的下将沿不会改变这个大触发器的内容。

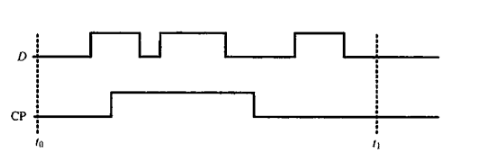

同样是之前的脉冲图示,在这个边沿触发器最终保存的值为:1

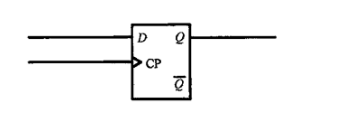

上面这个二合一的大触发器,不管控制端是0、1还是从1到0的下降沿,它都不能保存比特,除非一种情况,那就是从0到1的跳变,即上升沿。为了便于表示,上升沿D触发器的符合如下图。

-

同步触发器和边沿触发器的区别2024-08-12 3559

-

边沿触发器的类型有哪些2024-08-11 1926

-

边沿触发器的状态变化由什么控制2024-08-09 1753

-

主从rs触发器波形图介绍2018-02-08 22754

-

什么是边沿触发器_边沿D触发器介绍2018-01-31 73155

-

jk边沿触发器工作原理2018-01-30 38503

-

RS 和JK 触发器的波形图怎么画!!!!2012-12-20 13966

-

边沿触发SR触发器2010-08-10 7101

-

CMOS触发器在CP边沿的工作特性研究2009-10-17 2371

-

D触发器原理图和真值表以及波形图分析2007-09-11 189372

全部0条评论

快来发表一下你的评论吧 !