d锁存器与sr锁存器的区别

电子常识

描述

d锁存器

锁存器就是把单片机的输出的数据先存起来,可以让单片机继续做其它事。

比如74HC373是一种CMOS电路8D锁存器

74LS373是一种TTL电路 8D锁存器

74LS74 是一种TTL 带置位复位正触发双D触发器

它的LE为高的时候,数据就可以通过它。当为低时,它的输出端就会被锁定,即为刚才通过的数据,这样,就可以保持这个状态.D锁存器 锁存器对时钟脉冲电平(持续时间)敏感,在一持续电平期间都运作。

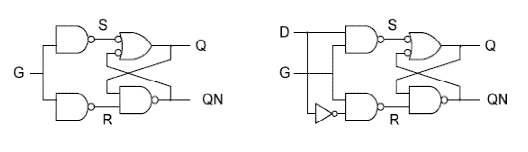

基本单元是最基础的存储器器件,并在特定的情况下发挥着重要的作用。但是,如果在一个基本单元上再加上两个逻辑门,那么就可以构造出更有用的存储器器件,该器件就称为D锁存器。D锁存器使用基本单元作为存储部件,但它只允许在时序控制信号有效时才能改变(或编程)存储器存储的逻辑值。因此,D锁存器有两个输入-时序控制信号和数据输入。时序控制信号,通常也称为“门信号”,或“时钟”,或是“锁存使能”,主要用于同步新数据何时可以写入存储器,何时不能写入。如下图左图所示,可以看出当门信号无效时,S和R信号为1且输出Q由存储在基本单元反馈回路的值决定(所以Q就是存储的逻辑值)。再看右图,可以看出当门信号有效时,D(数据)输入将S和R驱动到各自相反的电平,从而在基本单元中强制了一个置位或复位操作。通过组合时序信号和数据输入信号来强制基本单元的置位或复位操作,我们就构造出了一个非常有用的存储器器件。D锁存器已经广泛使用在所有类型的现代数字电路中了。

如下图所示为D锁存器时序方框图。注意,当门信号有效时,输出Q只是简单的“跟随”输入。但是当门信号无效时,输出“记住”了门信号下降沿时的D值。

1、 在G有效前,Q未定义;Q有效时,Q得到D的值

2、 G无效而D有效,Q不改变

3、 D和G都有效;Q得到D的值

4、 G下降沿;Q存储了D值

5、 D下降沿,而G无效,Q值不改变

6、 G有效,Q得到D值

7、 G有效时,Q跟随D值

sr锁存器

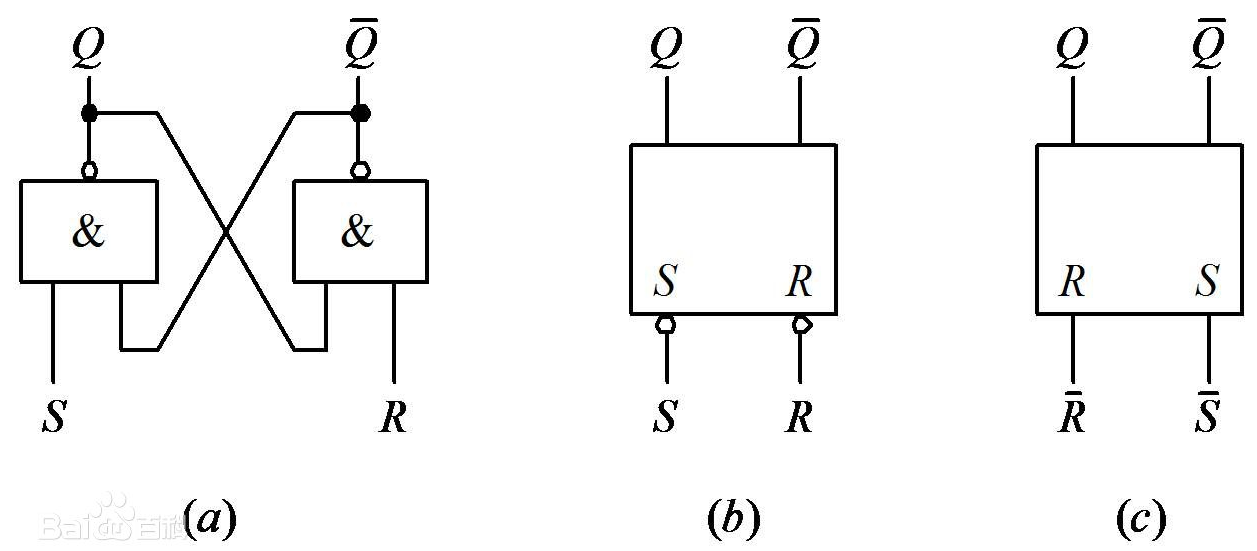

RS触发器是构成其它各种功能触发器的基本组成部分。又称为基本RS触发器。结构是把两个与非门或者或非门G1、G2的输入、输出端交叉连接。

工作原理

基本RS触发器的逻辑方程为:Qn+1=S=RQn (注:

以用与非门构成的RS锁存器为例)(低电平有效)

约束方程:S‘+R’=1(S‘和R’代表的是S和R的取反 S和 R )

根据上述两个式子得到它的四种输入与输出的关系:

S‘=0,R’=1:无论触发器原来处于何种状态,由于S=1,则Q=1,Q非=0,触发器处于“1”态(或称置位状态)。触发器的状态是由S所决定的,称S为直接置位端。

S‘=1,R’=0:无论触发器原来处于何种状态,由于R=0,则Q=0,Q非=1,触发器处于“0”态(或称复位状态)。触发器的状态是由R所决定的,称R为直接复位端。

S‘=1,R’=1:触发器维持原来状态不变。

S‘=0,R’=0:此时无法确定触发器的状态。一般这是不允许的,因此触发器的输入端S、R不能同时为1。

如上所述,当触发器的两个输入端加入不同逻辑电平时,它的两个输出端Q和Q非有两种互补的稳定状态。一般规定触发器Q端的状态作为触发器的状态。通常称触发器处于某种状态,实际是指它的Q端的状态。Q=1、Q非=0时,称触发器处于1态,反之触发器处于0态。R=1,S=0,使触发器置1,或称置位。因置位的决定条件是S=0,故称S 端为置1端。R=0,S=1时,使触发器置0,或称复位。

同理,称R端为置0端或复位端。若触发器原来为1态,欲使之变为0态,必须令R端的电平由1变0,S端的电平由0变1。这里所加的输入信号(低电平)称为触发信号,由它们导致的转换过程称为翻转。由于这里的触发信号是电平,因此这种触发器称为电平控制触发器。从功能方面看,它只能在S和R的作用下置0和置1,所以又称为置0置1触发器,或称为置位复位触发器。其逻辑符号如图7.2.1(b)所示。由于置0或置1都是触发信号低电平有效,因此,S端和R端都画有小圆圈。

3.当RS端均无效时,触发器状态保持不变。

触发器保持状态时,输入端都加非有效电平(高电平),需要触发翻转时,要求在某一输入端加一负脉冲,例如在S端加负脉冲使触发器置1,该脉冲信号回到高电平后,触发器仍维持1状态不变,相当于把S端某一时刻的电平信号存储起来,这体现了触发器具有记忆功能。

4.当RS端均有效时,触发器状态不确定。

在此条件下,两个与非门的输出端Q和Q非全为1,在两个输入信号都同时撤去(回到1)后,由于两个与非门的延迟时间无法确定,触发器的状态不能确定是1还是0,因此称这种情况为不定状态,这种情况应当避免。从另外一个角度来说,正因为R端和S端完成置0、置1都是低电平有效,所以二者不能同时为0。

此外,还可以用或非门的输入、输出端交叉连接构成置0、置1触发器,其逻辑图和逻辑符号分别如图7.2.2(a)和7.2.2(b)所示。这种触发器的触发信号是高电平有效,因此在逻辑符号的S端和R端没有小圆圈。

-

d锁存器解决了sr锁存器的什么问题2024-08-28 1748

-

sr锁存器和触发器的逻辑功能区别2024-07-23 1863

-

什么是锁存器 与寄存器有何区别2023-04-09 11450

-

SR锁存器和D锁存器的特点2023-02-27 11148

-

[6.2.1]--5.2.1SR锁存器学习电子知识 2022-11-16

-

分析一下SR锁存器的原理2022-08-20 7920

全部0条评论

快来发表一下你的评论吧 !