关于小信号输出阻抗的模拟仿真技术

模拟技术

描述

测一个cascode的输出阻抗,直接在源端加直流电压源AC=1,然后让直接AC仿真,最后用电压除以电流,得出输出阻抗。一切需要求Rout的电路也可以通过加vcvs实现,得到它的输出阻抗。

前几天看到自己之前计算的design error budget,其中有关于Rout的具体要求和mismatch的最大值。一想到马上要面临的design review,顿时打了个激灵,吓得跑去乖乖跑了一下仿真。

(一)Rout

一个简单的cascode(或者一切需要求Rout的电路),如何得到它的输出阻抗呢?

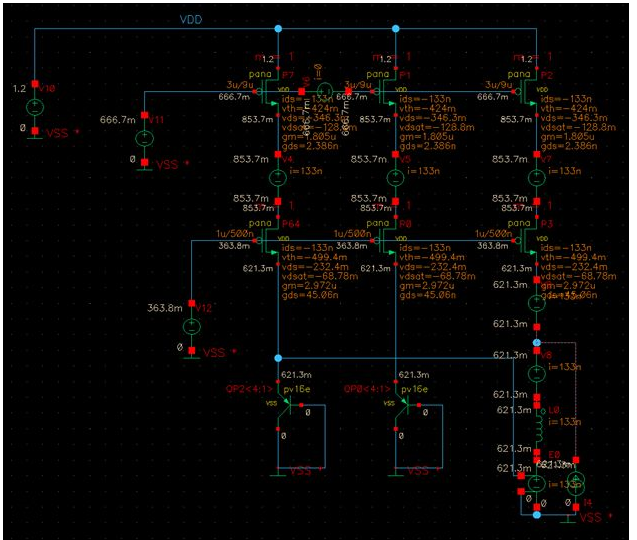

先扔出一个cadence的schematic:

(抱歉!为了能够plot电流,我放了不少dc=0的vdc,比如V4,V5,V7.。。.。不知道为何直接plot那些transistor的电流,都不可以……如果大家有好的方法,请务必指教!)

VDD=1.2V。最上面两排的pmos被两个固定的电压源bias。

因为我的cascode是拿来bias BJT的,所以前两路下面都是BJT(为什么要放两个一样的branch?那个……因为我还有mismatch要跑)。最右边的一路,有些特别。

最右边的最下面是一个vcvs(还是analogLib那个libaray里面的)。之所以没有直接加BJT,是担心BJT的等效电阻破坏了这个求cascode Rout的支路。所以,我就只用了vcvs作为固定的DC偏置电压。(其实再想想,直接用BJT也是可以的,关键在于上面的一个理想电感,数值越大越理想)。当时没想太多,所以就自作主张用了vcvs……

求解小信号都需要跑AC simulation,V=I*R,R=V/I

为了简便,我就在最右边加上了idc。这个idc的DC 是0,但是AC是1。因此,我需要得到的Rout就直接是被highlight的那条线的AC电压了。

嗯,那就来跑个AC看看吧!

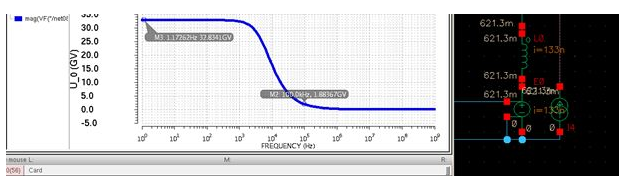

呼呼!长得蛮像opamp的AC曲线呢!

DC的时候,居然有32.8341GV,也就是说,Rout是32.8341GOhm。哇!真的很大呢!

对比一下手算的结果:P2的gds是2.386n,P3的gm是2.972u,gds是45.06n,所以粗略的计算,DC的Rout应该是gm3/(gds2*gds3),也就是27.64GOhm。

嗯,总的来说,差别不是很大,毕竟实际的公式没有这么粗略啦!

然后,因为我的电路工作时,会有一个100KHz的sampling clock,我就特地标注了一下100KHz时候的数值,是1.8836GOhm。

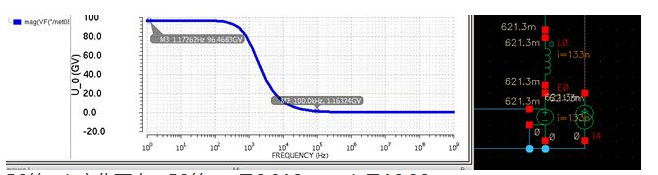

之后,习惯折腾的本人,改变了一下P3的W和L。刚刚是1u/500n,我把它改成了2u/1u,然后重新跑了一遍,得到了新的结果:

P2的gds变化不大,P3的gm是2.918u,gds是12.32n。

对比一下上面的结果,变化最显著的是gds3,明显小了很多。因此,DC的Rout也变大成了96.4683GOhm。

嗯,意料之中啊!短沟道效应。

等等!100KHz时,怎么变小了?从1.8836GOhm变成了1.18324GOhm……这也太……

寄生的cap增大了,所以下降的频率被提前了。看来,若是结构不变,想要大的DC gain,还是要付出一些额外的代价啊!

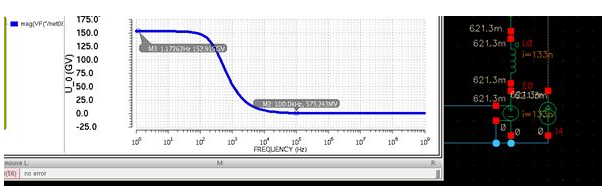

为了验证自己的想法,作者君继续调了P3到4u/2u,得到了下面的波形:

不出所料,DC的Rout也变大成了152.915GOhm。100KHz对应的Rout也变小成了573.243MOhm。

-

ADAS研发与测试的模拟仿真技术2020-09-02 0

-

输出阻抗的测定电路图2009-08-08 1706

-

阻抗是什么_输入阻抗和输出阻抗的理解2018-01-11 34573

-

称重传感器的输出阻抗类型2019-09-27 5309

-

模拟仿真技术是什么2020-05-19 16280

-

解析开环输出阻抗与闭环输出电阻区别2021-02-14 12178

-

传感器的输出阻抗是怎么一回事2022-03-01 4409

-

传感器的输出阻抗简单介绍2022-03-14 2025

-

放大器输出阻抗的参数是如何计算与仿真2023-02-22 3623

-

功率信号源的输出阻抗是多大的2023-08-01 857

-

请教关于LVDS阻抗匹配的问题 LVDS输出阻抗偏大会出现什么情况?2023-10-18 1754

-

振荡器中使用hbsp去仿真输出阻抗分析2023-12-05 1533

-

输入阻抗与输出阻抗的概念2024-05-28 3421

-

信号发生器输出阻抗设置在哪里2024-06-03 1664

-

安泰: 功率放大器的输出阻抗是什么意思2024-12-06 152

全部0条评论

快来发表一下你的评论吧 !