瀚海微SD NAND之SD 协议(45)SD电路设计

电子说

描述

固定延迟UHS-I主机设计实例

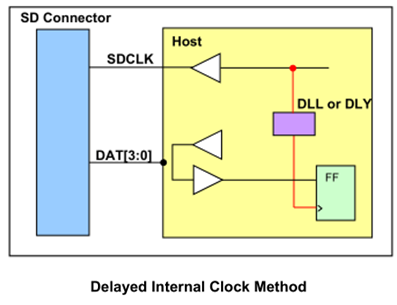

内部时钟延迟方法采样时钟由内部时钟通过DLL或延迟线创建。

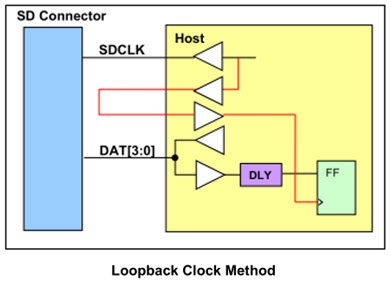

环回时钟的创建图

下图显示了环回时钟的一个示例实现。

适用于固定输出延时定时。

但是,主机设计人员需要注意由于额外路由CLKl跟踪而产生的过多EMI。

主机需要额外的两个引脚。

可以通过插入延迟线、R、C或使用DLL来调整接收机触发器的设置和保持时间。

UHS-1调谐程序

调谐是指在主机中寻找最优采样点的过程。

一旦SD卡从默认速度转移到SDR104模式,调谐过程就开始了。

调谐过程扫描UI (Unit Interval),以获得最佳采样点。

主机采样点调谐:

1.主机复位采样控制块

2.主机发出发送调优块命令来读取调优块。

3.卡发送调谐块作为读取数据。主机接收它并与已知的调优块模式进行比较。

4.主机将采样控制块增加一步。

5.主机为下一个调优块发送读取命令。

重复上面的步骤3到步骤5来覆盖整个UI。

在覆盖整个Ul之后,主机能够识别可用的有效窗口。

主机将采样控制块设置到有效窗口的中心。

主机采样点调优完成后,可以开始读/写操作。

主机设计建议

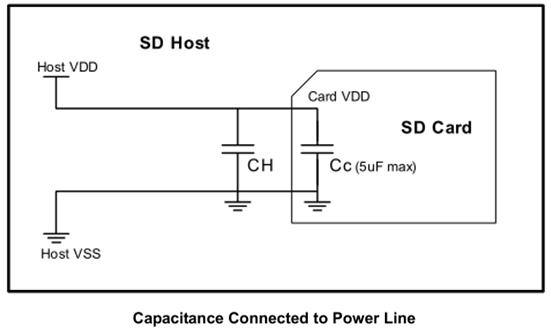

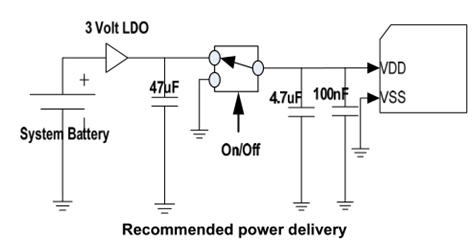

插在电源线上的去耦电容由于插在VDD和VSS之间的卡电容,SD卡插入时产生涌流。

本附录提供了一种使用安装在SD NAND附近的去耦电容来降低由浪涌电流引起的电压降的方法。

如果主机支持热插入,并且电源电路通常与其他设备一起使用,则主机应考虑并减少浪涌电流的影响。

采用限流电路等另一种方法也是可行的。

上图显示了去耦电容器的典型组成。

SD存储卡中去耦电容的最大电容定义为5uF。

去耦电容CH用于减小卡热插拔时的压降,最好放置在离连接器越近的地方。

在卡连接到主机之前,电容CH以电压VDD充电,Cc不充电。

当卡刚与主机连接时,卡瞬间短路,电流从CH流向Cc,直到CH的电压与Cc相等,此时由于CH中充电的能量被移动到Cc,瞬间电压从Vop略有下降。

这个降电压在这里定义为Vdrop。

在那之后,电压回到由电源充电的VDD。

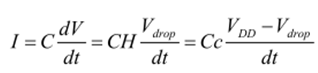

从CH到Cc的浪涌电流计算如下:

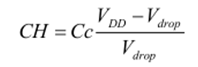

去耦电容CH的计算公式如下:

如果VDD是3.0V。Vdrop为0.3V(最大),以限制电压降小于VDD的10%。

由于SD内存卡Cc为5uF(最大),CH计算为45uF(最小)。

因此,仅支持SD存储卡的主机推荐去耦电容为47uF。

SDIO卡Cc定义为10uF(最大),然后计算CH为90uF(最小)。

因此,对于支持SDIO卡的主机,推荐去耦电容为100uF。

去耦电容

4.7uF电容的目的是支持低速浪涌电流。与4.7uF并联的100nF电容器用于高速浪涌电流。

这两个电容都可以作为噪声滤波。

电容器的物理位置应尽可能靠近SD插座VDD和VSS引脚。较小的电容器应靠近SD NAND。

电源开关主要用于SD卡的上电和电源回收。当开关LDO输出提供给卡时,47uF主要用作4.7uF电容的充电辅助。为了将3伏轨道上的电压降至最小,47uF充当中间储层,为4.7uF电容器充电,电源开关未连接到3伏轨道时环绕。

接地将快速可靠地释放VDD线路上的残余电压。这确保了可靠的电源回收。

但是,当开关将卡电源线接地时,作为短路,使充满电的4.7uF电容放电,产生较大的涌流。

审核编辑 黄宇

-

【贴片SD Card介绍】贴片式tf卡/SD NAND/SD2.0协议2023-07-28 8831

-

什么是SD NAND存储芯片? SD NAND与TF卡的区别2024-01-06 3789

-

贴片式SD卡功能介绍【MK SD NAND】2024-07-05 2919

-

瀚海微SD NAND之SD 协议(29)硬件接口2024-09-24 1496

-

瀚海微SD NAND之SD 协议(36)SPI模式2024-10-08 1479

-

瀚海微SD NAND之SD 协议(37)SPI总线保护和读写2024-10-09 1453

-

SD NAND技术简介2024-12-05 1427

-

SD NAND 概述2024-12-06 1497

-

SD NAND、SPI NAND 和 Raw NAND 的定义与比较2025-01-15 2124

-

SD卡—雷龙 SD NAND2025-07-21 4138

-

瀚海微SD NAND/TF卡——数据世界的全能搭档2025-10-13 578

-

瀚海微SD NAND/TF卡:赋能全场景数据存储,定义高效安全新基准2025-10-14 457

-

一文秒懂XTX SD NAND2025-10-30 1605

-

解决SD NAND CRC校验失败的综合指南:瀚海微存储产品的可靠性保障2025-11-21 661

-

ESP32 驱动瀚海微SD NAND 完整方案 + FAT/FAT32 驱动核心区别2026-02-02 834

全部0条评论

快来发表一下你的评论吧 !