74hc165中文资料详细(74hc165工作原理_引脚图及功能_应用电路_逻辑图)

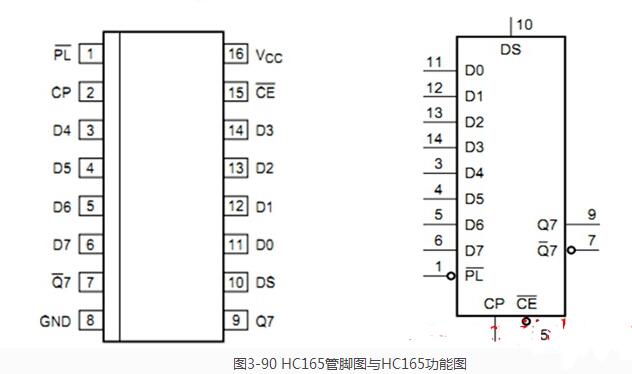

芯片引脚图

描述

74hc165简介

74HC165是8位并行读取或串行输入移位寄存器,可在末级得到互补的串行输出(Q7和!Q7),当异步并行读取引脚(!PL)输入为低时,从D0到D7口输入的并行数据将被读取进寄存器内。而当异步并行读取引脚为高时,数据将在每个时钟脉冲的上升沿从引脚串行进入寄存器并将现有数据右移一位(以此类推)。利用这种特性,只要把Q7输出绑定到下一级的输入,即可实现移位寄存器位数的扩展。74HC165的时钟输入是一个“门控与”结构,CP(时钟脉冲)和CE(时钟允许)共同产生有效时钟输入。只有在CE(时钟允许)为低时,CP(时钟脉冲)才有效。

74hc165特性

8位同步并行输入

异步串行输出

兼容JEDEC标准no.7A

ESD保护

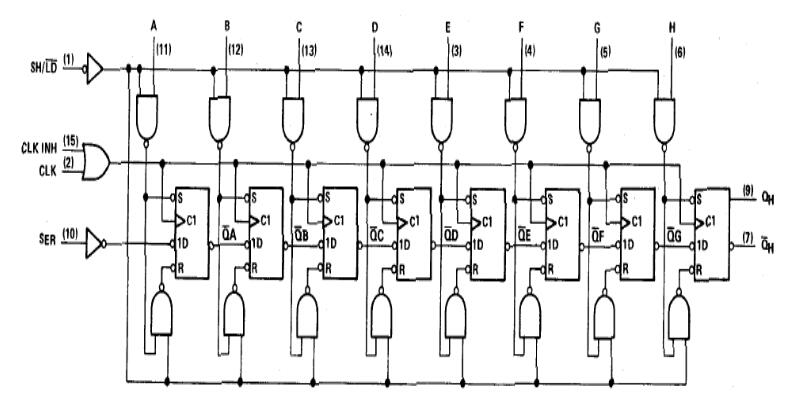

74HC165逻辑图

74hc165基本参数

电压:2.0~6.0V

驱动电流:+/-5.2mA

传输延迟:16ns@5V

最高频率:56MHz@5V

逻辑电平:CMOS

工作温度:-40~+85℃

封装:SO16,SSOP16,DIP16,TSSOP16

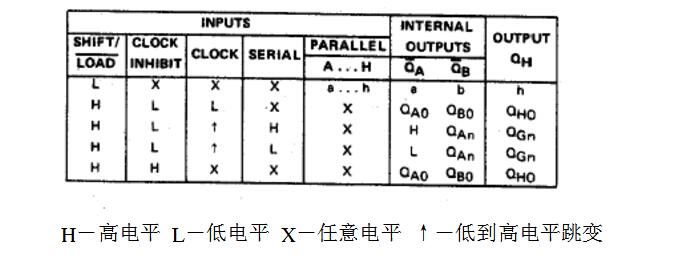

74HC165真值表

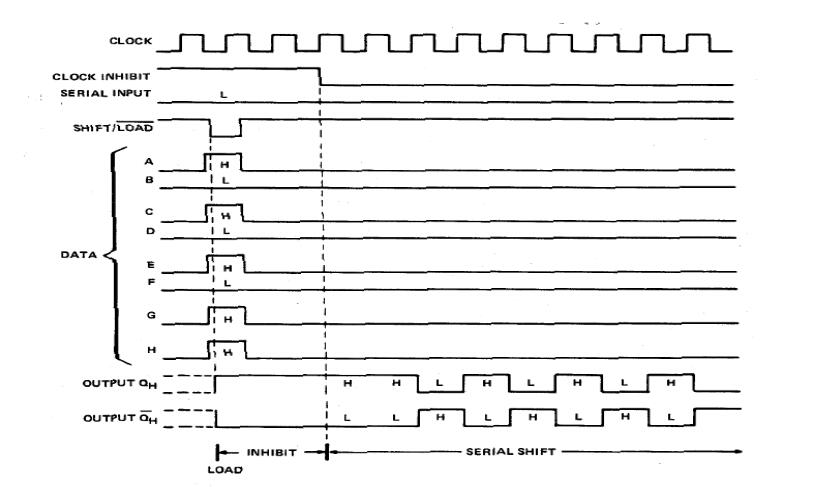

74HC165时序图

74hc165工作原理

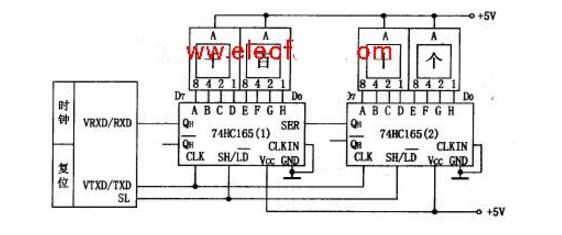

74HC165是八位并行输入/串行输出移位寄存器,两片74HC165串联在一起,在时钟脉冲的作用下,从KB-DAT读入串行数据,可完成对16位键盘数据扫描读取。 74HC165是一款高速CMOS器件,74HC165遵循JEDEC标准no.7A。74HC165引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC165是8位并行输入串行输出移位寄存器,可在末级得到互斥的串行输出(Q0和Q7),当并行读取(PL)输入为低时,从D0到D7口输入的并行数据将被异步地读取进寄存器内。而当PL为高时,数据将从DS输入端串行进入寄存器,在每个时钟脉冲的上升沿向右移动一位(Q0→Q1→Q2,等等)。利用这种特性,只要把Q7输出绑定到下一级的DS输入,即可实现并转串扩展。

74HC165的时钟输入是一个“门控或”结构,允许其中一个输入端作为低有效时钟使能(CE)输入。CP和CE的引脚分配是独立的并且在必要时,为了布线的方便可以互换。只有在CP为高时,才允许CE由低转高。在PL上升沿来临之前,CP或者CE应当置高,以防止数据在PL的活动状态发生位移。

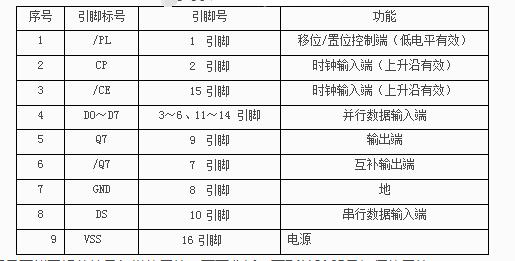

74hc165引脚图及功能

引脚功能表:

光看管脚说明是不能了解芯片是怎样使用的。下面分析一下74HC165是如何使用的。

①当输入端(SH/LD)为低:

从D0到D7口输入的并行数据将被异步地读取进寄存器内,然后通过DS输出。

②当输入端(SH/LD)为高:

数据将从DS(10引脚)输入端串行进入寄存器,在每个时钟脉冲的上升沿向右移动一位。利用这种特性,只要把Q7输出绑定到下一级的DS输入,即可实现并转串扩展。(在我们的开发板,DS端是悬空的),通过时钟管脚,上升沿有效,在每个时钟脉冲的上升沿向右移动一位(D0→D1→D2→D3→…→D7)一位一位将数据往外读出和移出。

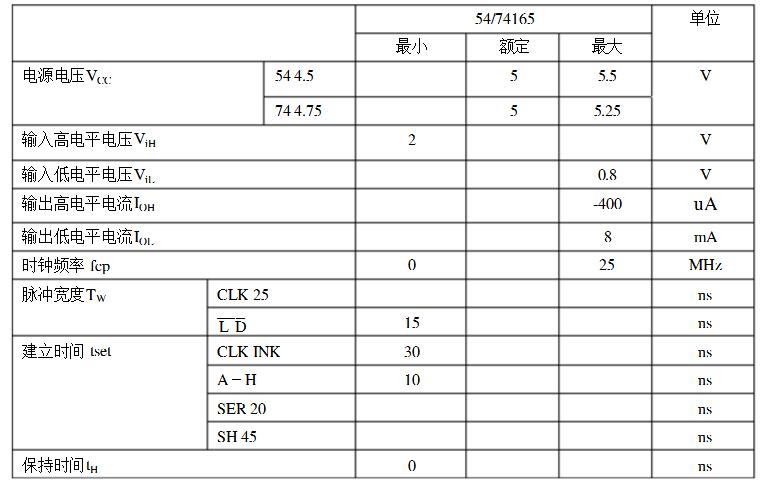

74HC165推荐工作条件

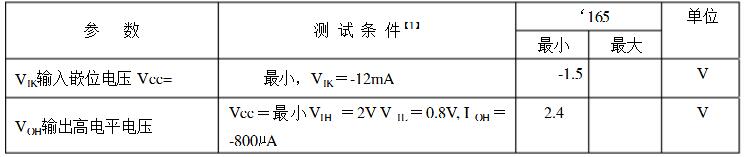

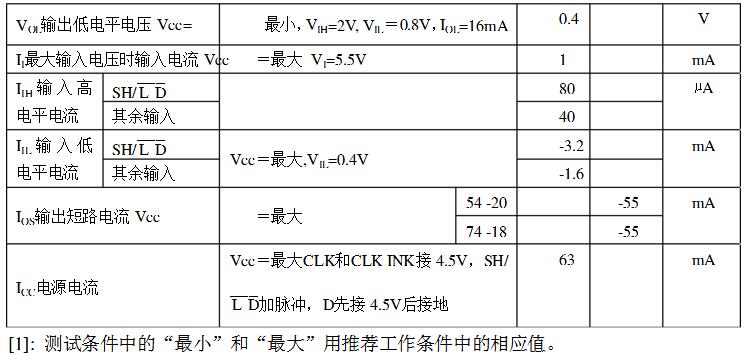

74HC165静态特性

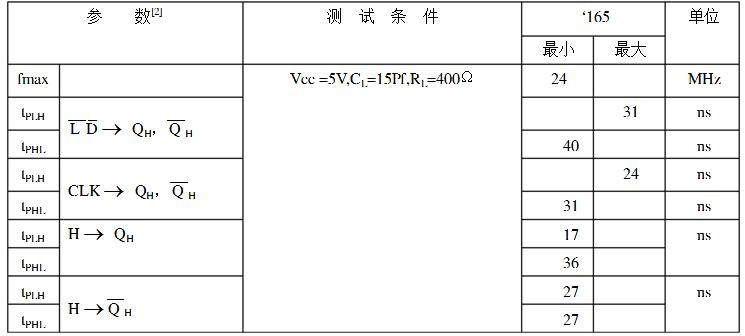

74HC165动态特性

fmax 最大时钟频率。tPLH输出由低电平到高电平传输延迟时间 tPHL输出由高电平到低电平传输延迟时间

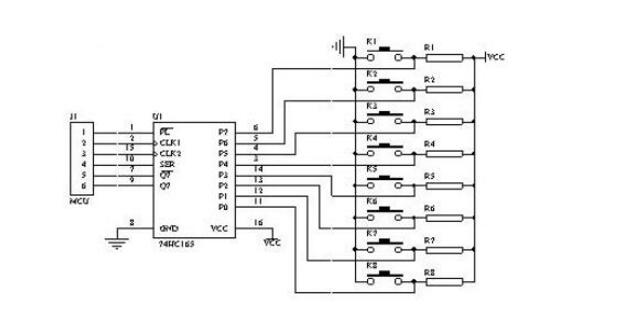

74hc165应用电路

74hc165典型应用电路图

74HC165扩展的4位BCD码码盘电路

推荐阅读:

-

fyc4480

2018-08-28

0 回复 举报我就搞不懂,哪里来的输入端SH/LD 1条回复 收起回复

fyc4480

2018-08-28

0 回复 举报我就搞不懂,哪里来的输入端SH/LD 1条回复 收起回复 -

樱空释¥

0

第一个引脚移位/置位控制端

樱空释¥

0

第一个引脚移位/置位控制端

- 相关推荐

- 热点推荐

- 74HC165

-

请教一个74HC165问题2022-03-25 6605

-

如何对74HC165的代码Proteus仿真2021-09-29 1965

-

74HC165编程篇2021-07-02 1425

-

用74HC165读8个按键状态2018-02-02 13053

-

74HC165功能说明资料下载2017-12-20 2471

-

74HC165英版数据手册2016-12-09 1392

-

74HC165英文手册2016-11-02 1123

-

74HC165读取按键键值的问题2016-03-15 16130

-

74HC1652015-06-15 6561

-

74hc165求助2014-06-28 3818

-

并串转换74hc1652013-10-12 2643

-

74hc165应用电路2008-09-22 8898

全部0条评论

快来发表一下你的评论吧 !