深度学习方案ASIC、FPGA、GPU比较 哪种更有潜力

人工智能

描述

几乎所有深度学习的研究者都在使用GPU,但是对比深度学习硬鉴方案,ASIC、FPGA、GPU三种究竟哪款更被看好?主要是认清对深度学习硬件平台的要求。

今天被罗振宇的跨年演讲刷爆了朋友圈。不过他讲深度学习和GPU的时候,真让人虐心。

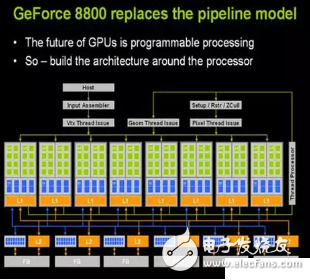

显卡的处理器称为图形处理器(GPU),它是显卡的“心脏”,与CPU类似,只不过GPU是专为执行复杂的数学和几何计算而设计的,这些计算是图形渲染所必需的。

对深度学习硬件平台的要求

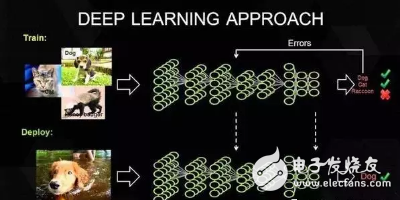

要想明白“深度学习”需要怎样的硬件,必须了解深度学习的工作原理。首先在表层上,我们有一个巨大的数据集,并选定了一种深度学习模型。每个模型都有一些内部参数需要调整,以便学习数据。而这种参数调整实际上可以归结为优化问题,在调整这些参数时,就相当于在优化特定的约束条件。

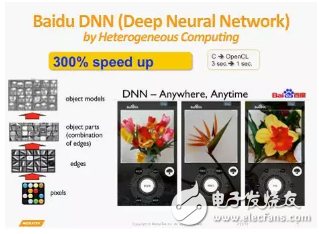

百度的硅谷人工智能实验室(SVAIL)已经为深度学习硬件提出了DeepBench基准,这一基准着重衡量的是基本计算的硬件性能,而不是学习模型的表现。这种方法旨在找到使计算变慢或低效的瓶颈。 因此,重点在于设计一个对于深层神经网络训练的基本操作执行效果最佳的架构。那么基本操作有哪些呢?现在的深度学习算法主要包括卷积神经网络(CNN)和循环神经网络(RNN)。基于这些算法,DeepBench提出以下四种基本运算:

矩阵相乘(Matrix Multiplication)——几乎所有的深度学习模型都包含这一运算,它的计算十分密集。

卷积(Convolution)——这是另一个常用的运算,占用了模型中大部分的每秒浮点运算(浮点/秒)。

循环层(Recurrent Layers )——模型中的反馈层,并且基本上是前两个运算的组合。

All Reduce——这是一个在优化前对学习到的参数进行传递或解析的运算序列。在跨硬件分布的深度学习网络上执行同步优化时(如AlphaGo的例子),这一操作尤其有效。

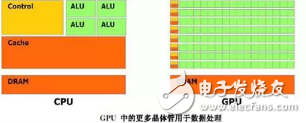

除此之外,深度学习的硬件加速器需要具备数据级别和流程化的并行性、多线程和高内存带宽等特性。 另外,由于数据的训练时间很长,所以硬件架构必须低功耗。 因此,效能功耗比(Performance per Watt)是硬件架构的评估标准之一。

GPU在处理图形的时候,从最初的设计就能够执行并行指令,从一个GPU核心收到一组多边形数据,到完成所有处理并输出图像可以做到完全独立。由于最初GPU就采用了大量的执行单元,这些执行单元可以轻松的加载并行处理,而不像CPU那样的单线程处理。另外,现代的GPU也可以在每个指令周期执行更多的单一指令。所以GPU比CPU更适合深度学习的大量矩阵、卷积运算的需求。深度学习的应用与其原先的应用需求颇为类似。GPU厂家顺理成章的在深度学习,找到了新增长点。

英伟达以其大规模的并行GPU和专用GPU编程框架CUDA主导着当前的深度学习市场。但是越来越多的公司开发出了用于深度学习的加速硬件,比如谷歌的张量处理单元(TPU/Tensor Processing Unit)、英特尔的Xeon Phi Knight‘s Landing,以及高通的神经网络处理器(NNU/Neural Network Processor)。

多亏了新技术和充满GPU的计算机数据中心,深度学习获得了巨大的可能应用领域。这家公司的任务中很大一部分都只是获取用来探索这些可能性的时间和计算资源。这项工作极大地扩张了设计空间。就科学研究而言,覆盖的领域已经在指数式扩张了。而这也已经突破了图像识别的范畴,进入到了语音识别、自然语言理解等其它任务中。正因为覆盖的领域越来越多,微软在提高其GPU集群的运算能力的同时也在探索使用其它的专用处理器,其中包括FPGA——一种能针对特定任务(如深度学习)编程的芯片。而且这项工作已经在全世界的技术和人工智能领域掀起了波澜。英特尔完成了其历史上最大的并购案,收购了专注FPGA的Altera。

FPGA的优势是,如果计算机需要改变,它可以被重新装配。但是,最通用、最主流的方案仍旧是使用 GPU,以并行处理大量数学运算。不出预料,GPU 方案的主要推动者是该市场的霸主英伟达。

英伟达旗舰显卡 Pascal Titan X

事实上, 2009 年之后人工神经网络的复兴与 GPU 有紧密联系——那一年,几名斯坦福的学者向世界展示,使用 GPU 可以在合理的时间内训练深度神经网络。这直接引发了 GPU 通用计算的浪潮。

英伟达首席科学家、斯坦福并发 VLSI 架构小组的负责人 William J. Dally 表示:“行内每个人现在都在做深度学习,这方面,GPU 几乎已经达到了最好。”

几乎所有深度学习的研究者都在使用GPU

熟悉深度学习的人都知道,深度学习是需要训练的,所谓的训练就是在成千上万个变量中寻找最佳值的计算。这需要通过不断的尝试实现收敛,而最终获得的数值并非是人工确定的数字,而是一种常态的公式。通过这种像素级的学习,不断总结规律,计算机就可以实现像像人一样思考。如今,几乎所有的深度学习(机器学习)研究者都在使用GPU进行相关的研究。当然,只是“几乎”。除了GPU之外,包括MIC和FPGA也提供了不同的解决方案。

“技术发展和科技的发展,是需要不同的技术一起来参与。无论是GPU也好、FPGA也好或者是专用的神经网芯片也好,它的主要目的都是推动深度学习(机器学习)这个方向的技术发展。那么我们在初期,确实可以尝试不同的技术,来探讨哪种技术可以更好的适合这项应用。从目前来看,深度学习大量的使用,主要集中在训练方面。那么在这个领域,GPU确实是非常适合的,这也体现在所有的这些工业界的大佬如BAT、谷歌,Facebook等等,都在使用GPU在做训练。”NVIDIA如是说。面对FPGA以及ASIC的挑战,NVIDIA表示“考虑是否设计低功耗的GPU,来满足用户的需求”。

除了硬件方面的因素之外,英伟达从软件方面解答了GPU对于深度学习应用的价值。首先从深度学习应用的开发工具角度,具备CUDA支持的GPU为用户学习Caffe、Theano等研究工具提供了很好的入门平台。其实GPU不仅仅是指专注于HPC领域的Tesla,包括Geforce在内的GPU都可以支持CUDA计算,这也为初学者提供了相对更低的应用门槛。除此之外,CUDA在算法和程序设计上相比其他应用更加容易,通过NVIDIA多年的推广也积累了广泛的用户群,开发难度更小。最后则是部署环节,GPU通过PCI-e接口可以直接部署在服务器中,方便而快速。得益于硬件支持与软件编程、设计方面的优势,GPU才成为了目前应用最广泛的平台。

深度学习发展遇到瓶颈了吗?

我们之所以使用GPU加速深度学习,是因为深度学习所要计算的数据量异常庞大,用传统的计算方式需要漫长的时间。但是,如果未来深度学习的数据量有所下降,或者说我们不能提供给深度学习研究所需要的足够数据量,是否就意味着深度学习也将进入“寒冬”呢?“做深度神经网络训练需要大量模型,然后才能实现数学上的收敛。深度学习要真正接近成人的智力,它所需要的神经网络规模非常庞大,它所需要的数据量,会比我们做语言识别、图像处理要多得多。假设说,我们发现我们没有办法提供这样的数据,很有可能出现寒冬”。

其实深度学习目前还在蓬勃发展往上的阶段。比如说我们现阶段主要做得比较成熟的语音、图像方面,整个的数据量还是在不断的增多的,网络规模也在不断的变复杂。

对于NVIDIA来说,深度学习是GPU计算发展的大好时机,其实这是一场各个能够实现深度学习各个芯片,以及巨头赛跑的结局。谁最先找到自己逼近深度学习最适合的芯片模式,谁就是胜利者。

GPU、FPGA 还是专用芯片?

尽管深度学习和人工智能在宣传上炙手可热,但无论从仿生的视角抑或统计学的角度,深度学习的工业应用都还是初阶,深度学习的理论基础也尚未建立和完善,在一些从业人员看来,依靠堆积计算力和数据集获得结果的方式显得过于暴力——要让机器更好地理解人的意图,就需要更多的数据和更强的计算平台,而且往往还是有监督学习——当然,现阶段我们还没有数据不足的忧虑。未来是否在理论完善之后不再依赖数据、不再依赖于给数据打标签(无监督学习)、不再需要向计算力要性能和精度?

退一步说,即便计算力仍是必需的引擎,那么是否一定就是基于GPU?我们知道,CPU和FPGA已经显示出深度学习负载上的能力,而IBM主导的SyNAPSE巨型神经网络芯片(类人脑芯片),在70毫瓦的功率上提供100万个“神经元”内核、2.56亿个“突触”内核以及4096个“神经突触”内核,甚至允许神经网络和机器学习负载超越了冯·诺依曼架构,二者的能耗和性能,都足以成为GPU潜在的挑战者。

不过,这些都尚未产品化的今天,NVIDIA并不担忧GPU会在深度学习领域失宠。首先,NVIDIA认为,GPU作为底层平台,起到的是加速的作用,帮助深度学习的研发人员更快地训练出更大的模型,不会受到深度学习模型实现方式的影响。其次,NVIDIA表示,用户可以根据需求选择不同的平台,但深度学习研发人员需要在算法、统计方面精益求精,都需要一个生态环境的支持,GPU已经构建了CUDA、cuDNN及DIGITS等工具,支持各种主流开源框架,提供友好的界面和可视化的方式,并得到了合作伙伴的支持,例如浪潮开发了一个支持多GPU的Caffe,曙光也研发了基于PCI总线的多GPU的技术,对熟悉串行程序设计的开发者更加友好。相比之下,FPGA可编程芯片或者是人工神经网络专属芯片对于植入服务器以及编程环境、编程能力要求更高,还缺乏通用的潜力,不适合普及。

目前来说,GPU贵,功耗高,运行效率比FPGA高,易使用。FPGA功耗,单颗性能是低的,单颗FPGA的硬件设计挑战没有GPU大,但是总体性价比和效率不占优;Intel收购Altera是否可以通过其工艺实力,给其带来极具的功能提升,我们还在长期的期待过程中。FPGA如果实现深度学习功能,还需要大批量使用,才能实现完整的功能,且需要与CPU相结合。

另外一个问题是,FPGA的大规模开发难度偏高,从业人员少。我们可以通过ARM战胜MIPS、以及STM32的迅速发展可以看到,一个好的生态环境,更多的从业人口,比技术、性价比本身更利于其发展。所以易用性是几个并行技术发展的一个重要考量维度。

FPGA犹如乐高,其灵活性,根据实际应用的需求,构建我所需要的硬件组件。但是乐高本身就是一种浪费:其功耗性能比,可变布线资源、多余的逻辑资源,其实都是浪费。所以你如果用乐高做一个机器人跟一个专门为格斗而开发的机器人对抗,结果可想而知。

FPGA在深度学习的应用场景,存在的价值在于其灵活性。DNN是深度神经网络系统的统称,实际使用的时候,使用几层网络,最终结果用什么样的筛选策略,在不同的应用和不同的设计框架下面,对硬件的诉求并不相同。

要看设计者的建模方案。GPU的一个缺点是,他的组件模块是乘法器、加法器。虽然深度学习的参数都是数学模型,需要对RTL级别的变化,但是GPU的硬件资源是以乘法器、加法器这样量级的硬件单元组成的。如果GPU的预先配置与使用者的模型相差甚远。例如:加法器配置15个,乘法器配置15个。但实际使用的时候,乘法器使用量是15个,但是加法器只需要2个。这就浪费了13个加法器的资源。而FPGA是以查找表和触发器子单元,组合成任意运算单元。

但是换种角度来看FPGA本身就是一种浪费。

当然ASIC是能效最高的,但目前,都在早期阶段,算法变化各异。想搞一款通用的ASIC适配多种场景,还是有很多路需要走的。但是,在通信领域,FPGA曾经也是风靡一时,但是随着ASIC的不断发展和蚕食,FPGA的份额和市场空间已经岌岌可危。如果深度学习能够迅速发展,有可能这个过程会比通信领域过程更短。

人机大战落幕后的两个月,谷歌硬件工程师 Norm Jouppi 才公开了其加速硬件的存在。在博客中,他解释道,谷歌给数据中心装备这些加速器卡已经有超过一年的时间。虽然谷歌对技术细节严格保密,但已透露它们专为谷歌开源项目 TensorFlow 而优化;它采取了:ASIC。

谷歌发布了人工智能芯片:Tensor Processing Unit,这是ASIC

据知情人士说,TPU已经在谷歌的数据中心运行了一年时间,由于谷歌严守TPU的秘密,所以TPU一直不为外界所知。这位知情人士说,从目前的运行效果来看,TPU每瓦能耗的学习效果和效率都比传统的CPU、GPU高出一个数量级,达到了摩尔定律预言的七年后的CPU的运行效果。这位知情人士不无煽情的说,请忘掉CPU、GPU、FPGA吧。

如此看来,在深度学习方面,TPU可以兼具桌面机与嵌入式设备的功能,也就是低能耗高速度。

据报道,TPU之所以具有良好的机器学习能力,是因为这种芯片具有比较宽的容错性,这就意味着,达到与通用芯片相同的学习效果,TPU不需要通用芯片那样多的晶体管,不需要通用芯片上那样多的程序操作步骤,也就是说,相同数量的晶体管,在TPU上能做更多的学习工作。

谷歌研发TPU并非要取代CPU或者FPGA,谷歌认为,TPU是介于CPU和ASIC (application-specific integrated circuit:应用集成电路)之间的芯片。ASIC用于专门的任务,比如去除噪声的电路,播放视频的电路,但是ASIC明显的短板是不可更改任务。通用CPU可以通过编程来适应各种任务,但是效率能耗比就不如ASIC。一如前边所言,在机器学习方面,TPU兼具了CPU与ASIC的特点,可编程,高效率,低能耗。

最后说说,异构处理器:

什么是异构多核处理器?简单地说异构多核处理器指的是在CPU里集成了 CPU与【其他模块】一起同步工作,【也就是说 一块cpu 里不单有 CPU运算模块 还有其他运算模块 例如 GPU,FPGA,DSP等等。

AMD,Nvidia以及赛灵思公司都在进行异构多核处理器的研发

这是AMD的异构多核处理器

AMD在异构多核处理器发展方面是不遗余力,早在2012年就成立了“异构系统架构基金会”(HSA Foundation),首批会员是AMD、 ARM、Imagination Technologies、 联发科和德州仪器(TI)是“异构系统架构基金会”的创始成员。

瞧瞧,英特尔的老对手ARM和AMD都在里面呢

HSA联盟发展了两年也有一些新成员加入,但是总的来说对英特尔威胁不大,直到 ,直到,赛灵思推了zynq的时候。

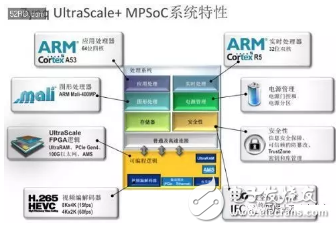

看看它的内部结构:

1、四核A53处理器 CPU

2、一个GPU Mali-400MP

3、一个Cortex-R5 CPU

4、电源管理单元,AMS单元

5、H.265(HEVC)视频编解码器

6、安全模块

7、UltraScale FPGA 单元;

这其实就是一款异构处理器,如前所述,它是一款ASIC就级的异构处理器!而且是64位,采用16nm FinFET工艺的处理器!而且是采用FPGA实现硬加速的处理器!但是这个ARM是不是偏弱了一点?做深度学习还是欠把火后。

Intel收购Altera,应该最终的目的也是要在异构处理器上面做出更多的文章吧。X86+FPGA,看起来好像很美。但是X86和FPGA结合就更符合模型么?目前也没有应用,更没有看到成熟的芯片推出。两个巨无霸的整合,可以说是用脚趾头都能想到很多的困难。Intel这口也许吃得太大了,吞得很痛苦。不是每个公司都有很强大执行力的,历史包袱在所难免。

-

对FPGA与ASIC/GPU NN实现进行定性的比较2023-02-08 0

-

GPU深度学习应用案例2024-10-27 403

-

到底什么是ASIC和FPGA?2024-01-23 0

-

FPGA在深度学习应用中或将取代GPU2024-03-21 0

-

FPGA做深度学习能走多远?2024-09-27 0

-

FPGA 超越 GPU,问鼎下一代深度学习主引擎2017-04-27 0

-

【详解】FPGA:深度学习的未来?2018-08-13 0

-

什么是深度学习?使用FPGA进行深度学习的好处?2023-02-17 0

-

相比GPU和GPP,FPGA是深度学习的未来?2016-07-28 7482

-

ASIC和FPGA设计优势和流程比较2017-11-25 4621

-

FPGA、ASIC将在机器学习领域崛起2018-01-06 5083

-

GPU和GPP相比谁才是深度学习的未来2019-10-18 1494

-

FPGA在深度学习领域的未来会有怎样的发展2019-10-22 1077

-

GPU 引领的深度学习2023-01-04 732

-

自动驾驶主流架构方案对比:GPU、FPGA、ASIC2023-02-14 3289

全部0条评论

快来发表一下你的评论吧 !