易灵思钛金系列加密方案-V1

描述

硬件设计要求

在之前的版本中,加密是通过VCC_AUX来供电的。在新的版本中已经通过单独的VQPS管脚来供电来实现。

对于Ti35/Ti60F225,VQPS供电管脚是G6,对于Ti35/Ti60F100S3F2,VQPS供电管脚是A5,这两个脚在之前的版本中都直接接地的。所以对于新设置的硬件或者改版的硬件,如果要使用加密功能就需要注意。

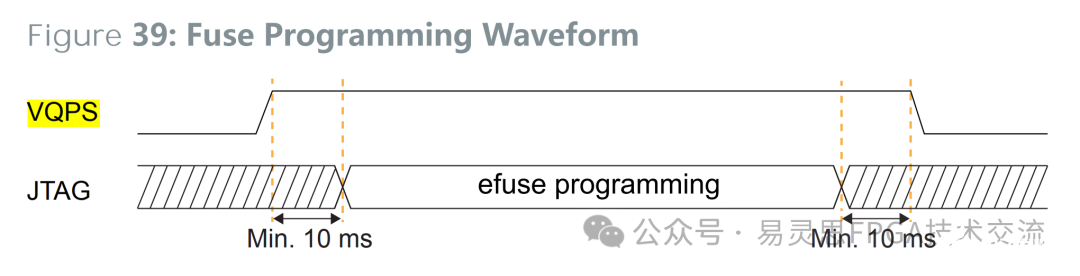

如果需要烧写密钥,可以单独给VQPS供1.8V的电源,VQPS的供电波形如下。可以考虑把VQPS拉到一个排针上或者座子上,烧写密钥时就给VQPS供电1.8V,烧写完成之后再拉低即可。

如果不需要烧写密钥只要把VQPS管脚拉低即可以。

易灵思的钛金系列支持加密特性,包括使用AES-GCM-256算法的比特流加密知识产权保护和使用RSA-4096算法的非对称比特流认证。这两种方式既可以单独使用,也可以同时使用,下面来详细了解下。

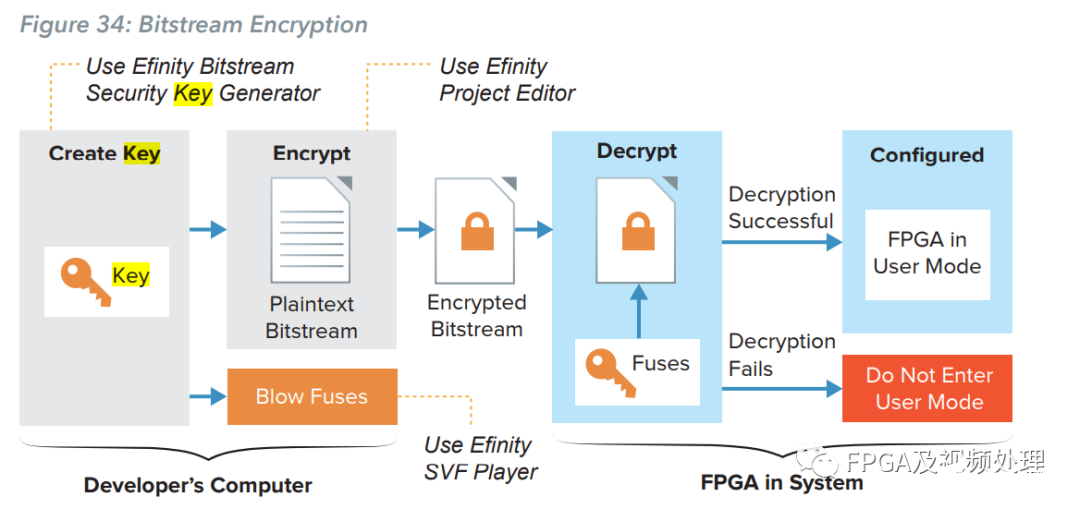

1)、对称比特流加密

使用256位的密钥和AES-CGM-256加密算法。

(1)生成密钥,

(2)用生成的密钥加密比特流(通过bin文件);

(3)把生成的密钥存储到FPGA的熔丝中,即下图中的Blow Fuses工具,密钥在svf文件中。

(4)在FPGA配置过程,FPGA通过内部的AES-GCM-256引擎和密钥解密加密的数据流。

需要补充的是FPGA通过Blow Fuses工具烧写了熔丝之后,也是可以配置不加密比特流的。

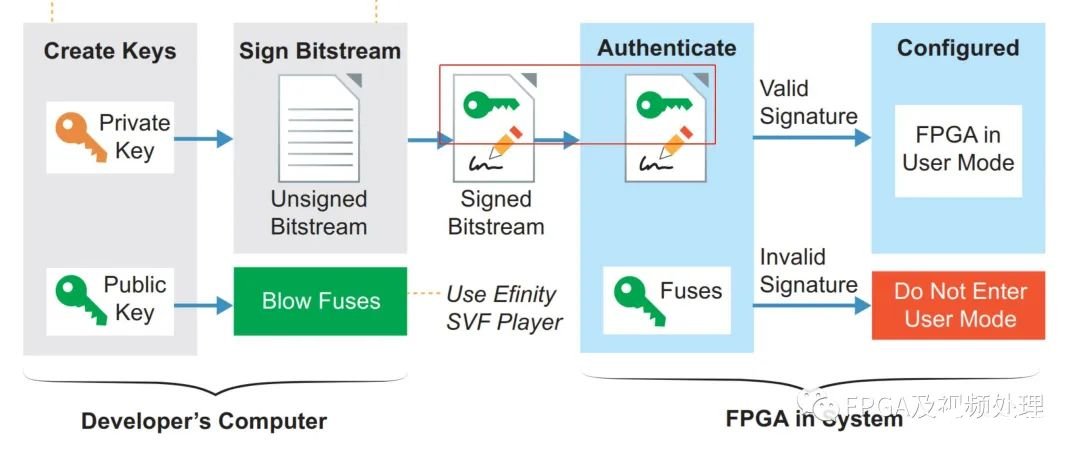

2)、比特流认证

对于比特流认证,需要使用公钥和私钥对及RSA-4096算法。

(1)生成公钥和私钥;

(2)用私钥对数据流签名,私钥存储在.pem文件中。

(3)将公钥的哈希值存储到FPGA内部的熔丝中,即下图中的Blow Fuses工具。,公钥在svf文件中。

(4)在配置过程中,FPGA通过公钥对比特流进行签名验证;如果签名有效,FPGA就知道位流来自可信的源,并且没有被第三方修改过则进入用户模式;否则停止配置;

(5)私钥要保存好。

需要补充的是FPGA通过Blow Fuses工具烧写了熔丝之后,必须要用.pem文件对比特流进行签名。

3)、JTAG阻断

钛金系列FPGA还支持通过烧断熔丝的方式阻断JTAG功能。阻断之后JTAG只能执行读取ID和器件状态和使能旁路模式;因为JTAG阻断之后就没有办法再操作JTAG,所以要确保在最后一步使用。

四、软件操作

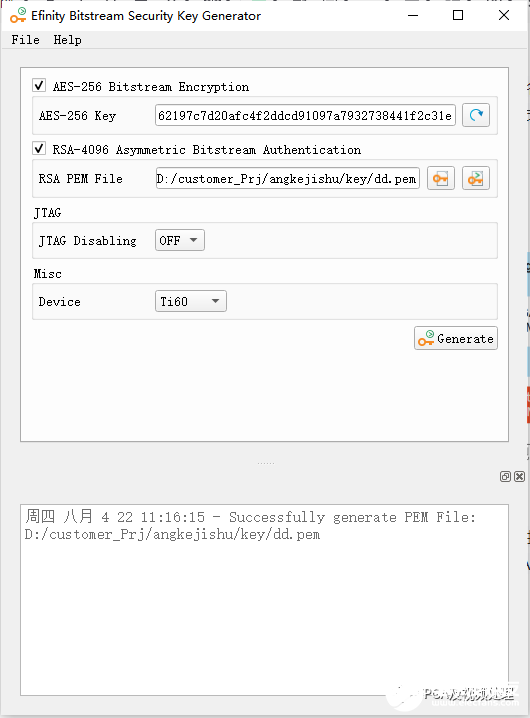

在Efinity菜单Tool- >Open Key Generator打开密钥生成器。

(1)ASE-256 Key用于生成ASE 256位的密钥文件,可以随机生成,也支持手动输入,文件后缀为.bin。

(2)生成RSA-4096的私钥文件,后缀为.pem。支持手动添加文件也支持自动生成。

(3)指定是否阻断JTAG.

(4)点击Generate生成相应的文档。会生成以.bin,.pem和.svf为后缀的三个文件。

数值要保存

烧写熔丝。

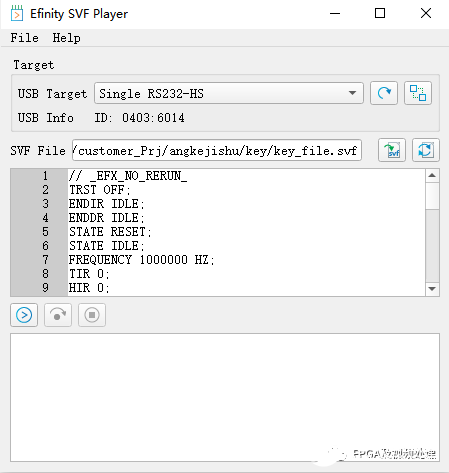

在Efinity菜单Tool- >Open JTAG SVF Player。

添加svf文件。svf文件中包含JTAG命令和密钥信息。

(1)读取JTAG IDCODE与.svf内的ID进行比对,确认是否为目标型号PFGA。

(2)对于AES加密,发送8个32位的key;

(3)对于RAS认证,发送12个32位的Key;

(4)发送熔断JTAG熔丝的指令;

(1)RAS密钥熔断熔丝后,FPGA只能接受通过正确的私钥签名的比特流文件。

(2)AES-256密钥熔丝后,FPGA只能接受未加密文件或者通过正确的密钥加密的比特流文件。

注意烧写后复位CRESET_N才会生效。

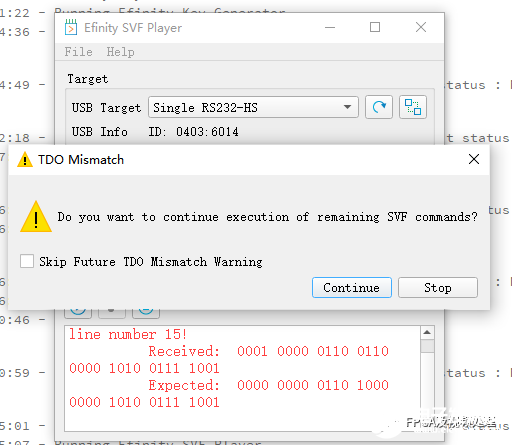

已经被熔断的熔丝再次熔断时,或者FPGA的型号与密钥生成器中的型号不对应时会发送TDO Mismatch。如下图。

在Project Editor中把上面生成的生成加密文件根据需要添加起来,重新生成比特流即可,不需要重新编译。

如果只用AES-256,则不需要勾选Bitstream Authentication.

5)熔丝的熔断顺序

对于AES-256、RSA和JTAG熔丝熔断顺序要求是:可以同时熔断AES-256和RSA的熔丝和熔断JTAG熔丝;但在不同时熔断的情况下,只能把JTAG熔丝熔断操作放在最后。对于AES-256和RSA熔丝熔断顺序不做要求。

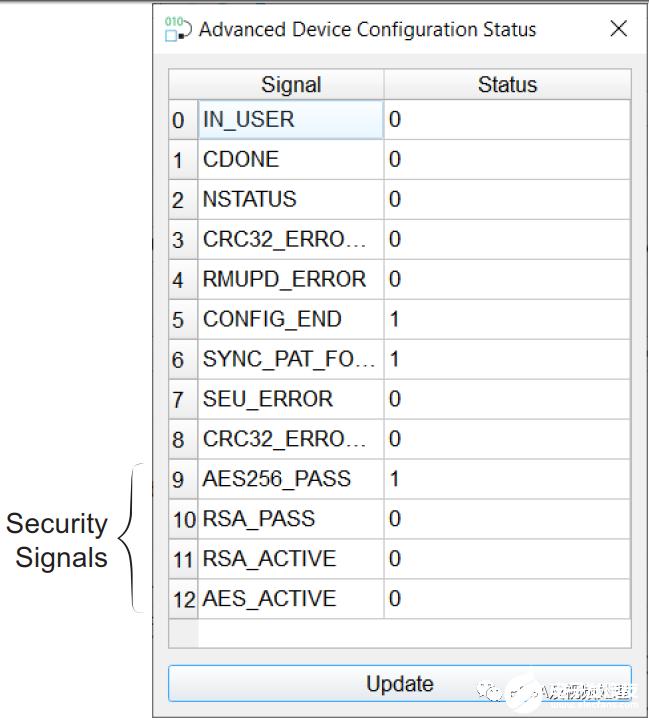

6)验证加密选项。

通过Programmer工具的Advanced Device Configuration Status中的RSA_ACTIVE和AES_ACTIVE可以判断是否使能了RSA和AES,当为1时表示使能。

补充说明:

(1)加密时不能使用数据流压缩功能。

(2)加密功能必须要接REF_RES_3A电阻

-

易灵思2026技术研讨会圆满举办,16nm 钛金系列重塑FPGA效能边界2026-04-20 127

-

易灵思16nm FPGA助力汽车市场发展 天玑智慧监管解决方案亮相推进会2022-03-07 1783

-

高价回收赛灵思系列IC2021-04-06 1112

-

8848钛金手机宣布关停加密通话功能2020-12-14 2345

-

Xilinx赛灵思方案2019-01-21 2615

全部0条评论

快来发表一下你的评论吧 !