TLVR降压器中的电流纹波和瞬态性能

描述

跨电感电压调节器(TLVR)在多相DC-DC应用中颇受欢迎,这些应用为CPU、GPU和ASIC等低压大电流负载供电,这一趋势主要基于该技术出色的瞬态性能。TLVR还支持灵活的设计和布局,但有几个缺点。本文阐述了TLVR设计选择如何影响性能参数,并讨论了相关权衡。

TLVR降压器中的电流纹波和瞬态

对于许多高电流应用而言,多相降压转换器的任何改进都有意义。瞬态性能改进尤其值得关注,因为许多CPU、GPU和ASIC现在都有非常严格的瞬态规格,而高效率对于节能和热性能也至关重要。

电感中的电流纹波是影响设计选择的重要参数:它影响效率和输出电压纹波,并间接关系到瞬态性能、解决方案尺寸和其他性能指标。另一个关键特性是瞬态条件下的电流摆率,这是瞬态性能的基本限制因素。通常,电流纹波(以及效率)和瞬态性能(直接影响输出电容大小等因素)导致设计决策需要权衡。

采用分立电感(DL)的传统多相降压转换器如图1a所示。为了实现较理想的波形交错,假定所有相位之间都具有适当的相移。一种替代方案是用耦合电感(CL)代替DL,如图1b所示。另一种替代方案如图1c所示,称为TLVR,其中调谐电感 Lc 会影响 电流纹波和瞬态性能。TLVR方法的原理是向分立电感添加次级绕组,并通过次级绕组的电气连接来链接相位。这种设计思路类似于耦合电感:对所有链接相位之间的交流波形进行平均,以在特定瞬态摆率下获得更好的电流纹波,但TLVR的有效耦合电感是有限的,因为必须考虑全部相电流。TLVR的缺点是TLVR变压器不能传送电流的直流部分,因此直流电不会像在磁耦合电感中那样在相位之间抵消掉。本文将重点介绍TLVR 的更多细节和特定权衡;由于论文篇幅限制,这些内容未包含在之前的研究中。

图1. 多相降压转换器,分别采用(a)分立电感(DL)、(b)耦合电感(CL)和(c) TLVR

TLVR中纹波和电流摆率的第一个数学模型及方程可能已出现在相关文献中。虽然这是一个非常有用的数学模型,适用于任何电路条件(任何占空比 D = Vo/VIN 或多个相位 Nph等),但它有一些局限性。例如,低 Lc 值(图1c中的调谐电感)会导致误差增加,当 Lc = 0 时,误差变得无穷大,等等。低 Lc 值的极端情况比 Lc = 开路的极端情况更重要,因为使用TLVR的主要原因是改善瞬态性能,这意味着 Lc 值相当低。

此外还给出了更准确的TLVR推导,通过指定适当的Vx状态,推导出的方程可以得出稳态(对于电流纹波)或瞬态下的电流摆率。该推导是针对更准确的等效TLVR原理图(图2)进行的。此模型与任何极端情况下的仿真都具有极好的相关性,但稳态下的电流摆率仅对 1/Nph 范围有效。后者是可以接受的,因为已经证明,恰好在 1/Nph 区域,TLVR具有相对于DL基线的最大电流纹波增量,并且当Nph 足够高时,其接近DL纹波。

图2. TLVR模型

通常,TLVR值在数据手册中的显示方式与分立电感DL相同,从中可推导出TLVR。图2中的模型假设TLVR总值或自感被分成两部分:一个是通常较小的 Lk ,其余部分实际上成为TLVR变压器的互感 Lm = TLVR-Lk (方程1)。

基于图2中的模型,TLVR中的电流摆率可用方程2表示,其中Lk 是主绕组和辅助绕组之间的TLVR漏感。Vx1 电压分配给目标相位而所有其他 Vx 节点均假定具有相同电压 (VIN 或0)。相应的节点电压 Vy1 如方程3所示。强制 Vx1 = Vx a,并将这些电压指定为 VIN (斜坡上 升)或0(斜坡下降),便可使用方程2直接计算TLVR中的最大瞬态摆率。此外,方程2中的电流摆率可用于方程4中的稳态纹波计算,其中 Vx1 = VIN ,所有其他开关节点均为 Vx = 0。不过,方程4仅对 1/Nph有效,因为它假设全部导通时间 D/Fs内具有单一且相同的摆率。

如文献所述,品质因数(FOM)是反映系统性能的一个良好指标,最大化FOM通常是实现理想权衡的正确方向。但请注意,高FOM本身并不能确保特定应用规格中的每个参数都得到满足,高FOM仅是良好设计的一个指标。FOM的定义如方程5所示,这对于1/Nph 范围是合适的,我们可以用方程6来表示TLVR FOM。

为了进行比较,我们将使用CL方程(此处未显示),但重点关注TLVR性能和权衡。我们还将使用陷波耦合电感(NCL)结构作为基准,与尺寸和大小兼容的特定TLVR = 150 nH解决方案进行比较。

TLVR权衡

图3显示了基于12 V至1.8 V 6相设计的关键TLVR性能参数与调谐电感 Lc 的关系(电流纹波的(Fs = 300 )。TLVR = 150 nH是给定尺寸下勉强满足 Isat/ph 规格的最大可能值,因此它能充分有效地减小TLVR纹波并提高效率。此外还绘制出DL = 150 nH,作为TLVR = 150 nH的基线,以及 NCL = 6× 25 nH (Lm = 375 nH)参数以供比较。图3中所有TLVR曲线上都突出显示了实际设计点 Lc = 120 nH。

内容中需要考虑TLVR参数的变化:图3显示了(a) FOM,(b)电流瞬态摆率和(c)电流纹波与 Lc 的关系,水平刻度相同。请注意,随着Lc增加,所有TLVR曲线都渐近地接近DL性能。TLVR的FOM随着 Lc 值的降低而提高,因为瞬态摆率大幅提高,但代价是电流纹波进一步增加(DL基线的纹波已经相当大),参见图3c。将具有隔 离功能的次级绕组添加到初始DL时,铁氧体会减少,但TLVR FOM 绘图未考虑这一点。正如预期的那样,TLVR纹波始终大于DL基线。

图3. TLVR权衡与 Lc的关系:(a) FOM,(b) 电流摆率(向上),(c) 电流纹波。其中突出显示了实际设计点 Lc = 120 nH 。12 V至1.8 V,6相,Fs = 300 kHz。

图4显示了FOM、瞬态摆率和电流纹波与TLVR值(实际上是 Lm)的关系。值得注意的是,在绘制数学曲线时,TLVR的 Isat 规格是每相的全部 Isat(在测试解决方案中,对于TLVR = 150 nH,(Isat= 65 A ),而对于NCL的Lm,Isat 明显较低(对于必须承受相间电流不平衡的 Lm = 375nH,保守Isat = 25 A)。因此,在相同给定尺寸的测试解决方案中,高于150 nH的TLVR曲线和高于375 nH的NCL曲线仅有理论意义(需要更大的尺寸来扩展这些值)。由于TLVR和CL的电气模型相似,并且与Lm 的函数关系的相关曲线可能彼此接近,因此关键的一点是,对于TLVR和CL,给定空间中互感受到的限制大不相同。这为同一特定体积中的TLVR和NCL提供了一个现实的比较角度。

图4. TLVR权衡与TLVR值(Lm)的关系:(a) FOM,(b) 电流摆率(向上),(c) 电流 纹波。Lc = 120 nH, ,标出了给定尺寸下TLVR = 150 nH和 Lm = 375 nH (对于NCL)的最大值。12 V至1.8 V,6相 Fs = 300 kHz。

正如预期的那样,对于TLVR和NCL, Lm增加都会导致耦合系数和 FOM变大,如图4a所示。瞬态摆率一般由NCL中的漏感 Lk和TLVR中 的调谐电感 Lc 定义,而不是由 Lm定义,因此图4b中的曲线大部分 是平坦的。然而,当TLVR值(有效 Lm)变得过小时,并联 Lc 实际 上会短路,瞬态摆率迅速增加。

图4c证实,对于TLVR和NCL,增加 Lm 非常有利于减小电流纹波(但 Lm增加不会降低瞬态性能,参见图4b)。TLVR和NCL的电流纹波与 Lm的关系曲线非常相似,这是因为二者的电气模型相似,但 Lm 值的限制因素却截然不同。当然,大部分差异来自于给定尺寸下Lm所需的Lsat额定值,因此NCL的电流纹波比相关TLVR小得多。

实验结果

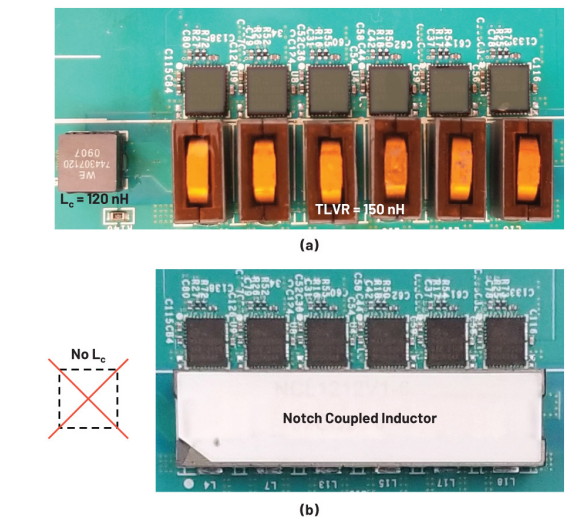

NCL设计为适合相同的TLVR尺寸,并且还匹配TLVR解决方案的所有其他外部尺寸。图5显示了同一电路板上的两个测试解决方案(NCL不需要 Lc)。

正如根据摆率值所预期的那样,TLVR和NCL都是非常快的解决方案(图3b和图4b)。我们特意验证了瞬态性能相同的情况,即使将 Fs 降低至300 kHz,仍然不会导致相位相互耦合的6相解决方案中出现反馈带宽限制。

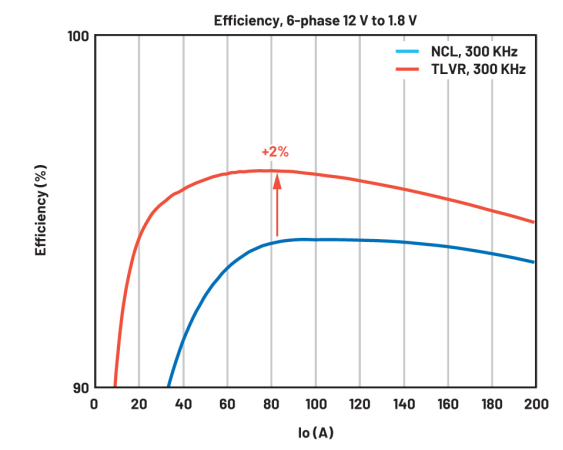

由于NCL的FOM明显高于TLVR(图3a),因此匹配瞬态性能导致NCL的电流纹波只有TLVR的大约1/2.6。图6显示了相应的效率比较结果,其中TLVR性能受到大电流纹波峰峰值的挑战。

由于CL(尤其是NCL)的漏感通常远低于TLVR值,因此预计CL和NCL的每相电流能力也高得多:TLVR = 150 nH示例中 Isat = 65 A (每相),而相同体积中的NCL = 6× 25 nH显示 Isat > 300 A(每相)。

图5. 同一电路板上的解决方案:(a) TLVR和(b) NCL

图6. 同一电路板上6相12 V至1.8 V解决方案的效率与Io的关系:(a) TLVR和(b) NCL

结论

TLVR的FOM一般约为2,从这个角度来看,它相对于FOM = 1的分立电感基线有所改进。其优势在于,与电流纹波增加相比,TLVR改善瞬态性能的速度更快。然而,TLVR只能改善瞬态,同时会产生一些弊端。例如,由于相位之间的链接以及较低的有效磁化电感和 Lc,TLVR电流纹波总是高于相同值DL情况的电流纹波。这会对效率产生不利影响,特别是考虑到添加具有高压隔离功能的次级绕组时铁氧体横截面会减小。本文未考虑铁氧体损失 所导致的额外电感值损失(假设Isat 与原始DL相同)。串联的次级TLVR绕组也会造成潜在的高压问题,并且通常会导致磁元件的成本增加。

TLVR的瞬态电流摆率通常由 Lc设置,但如果 Lm 足够低:那么 Lm 实际上会使 Lc短路,使得瞬态性能更快,但这会产生非常大的电 流纹波,导致效率受损。

般来说,TLVR的行为类似于耦合电感,但TLVR的全电流额定值会限制有效 Lm ,使其表现明显不佳。在相同的体积下,由于 Lm通常要高出几倍,因此CL或NCL可以实现高得多的FOM和性能。因此,在所考虑的例子中,NCL显示出高得多的效率,同时瞬态 性能相比TLVR也有所改善,但却不存在TLVR方法的成本影响或高压问题。

NCL与TLVR相比,每相 Isat电流能力显著提高,这是一个额外的好处(上例中差异大于4.5倍)。

-

基于变压器的稳压器,具有灵活的TLVR结构,可实现极快的动态响应2023-02-23 7043

-

为稳压器引入TLVR结构,实现极快的动态响应2023-10-25 2983

-

跨电感电压调节器(TLVR)的瞬态行为2024-01-24 7575

-

Bourns 全新 TLVR 电感器,提供极大的电流能力, 满足当今数据驱动的应用效能需求2024-05-16 1418

-

设计同步降压转换器时需考虑输入和输出电容的参数2017-04-18 3147

-

如何选择输出段元件最大化DC-DC同步降压转换器性能2018-09-30 1518

-

使用多相降压转换器的优势2018-11-26 2420

-

同步降压转换器设计中输入和输出电容参数的考虑2019-03-06 2538

-

DC/DC同步降压控制器的电流共享和负载瞬态性能2019-08-27 2960

-

一文详解降压转换器的电流纹波系数2022-04-20 11976

-

基于变压器的稳压器采用灵活的TLVR结构,实现极快的动态响应2023-06-13 1740

-

基于稳压器采用灵活TLVR结构实现极快的动态响应2023-06-14 2340

-

纹波电流是交流还是直流的2024-08-29 3429

-

瞬态响应与纹波——迟滞控制器中使用的纹波注入技术分析2024-10-09 594

-

高效、超低静态电流、超低输出纹波降压稳压器DA9232数据手册2025-04-08 1005

全部0条评论

快来发表一下你的评论吧 !