芯片制造中的钝化层工艺简述

描述

集成电路的可靠性与内部半导体器件表面的性质有密切的关系,目前大部分的集成电路采用塑料封装而非陶瓷封装,而塑料并不能很好地阻挡湿气和可移动离子。为了避免外界环境的杂质扩散进入集成电路内部对器件产生影响,必须在芯片制造的过程中淀积一层表面钝化保护膜。

由于Si3N4可以有效地阻挡水汽和可移动离子的扩散,制程工艺的最顶层是Si3N4,这层Si3N4称为钝化层,它的目的是保护芯片免受潮、划伤和粘污的影响。Si3N4是一种很好的绝缘介质,其结构致密、硬度大、介电强度高、化学稳定性好。Si3N4除了与HF和180°C以上的热磷酸有轻微作用外,几乎不与其他酸类反应。Si3N4对钠离子有很好的掩蔽作用,由于钠离子在 Si3N4中的固溶度大于在Si 和SiO2中的固溶度,所以它还有固定、提取钠离子的作用。

钠位于元素周期表中的I A 栏,最外层只有一个电子,钠很容易失去电子变成离子。钠离子非常小而且可以移动,钠离子很容易被 MOSFET栅氧化层的界面俘获,从而影响器件的电学特性。

1)淀积 PSG。通过HDP CVD 淀积第一层约8000A含磷的SiO2保护层。因为HDP CVD的特点是低温,它的台阶覆盖率非常好。该层SiO2保护层可以防止水汽渗透进来,加磷的主要目的是吸附杂质。

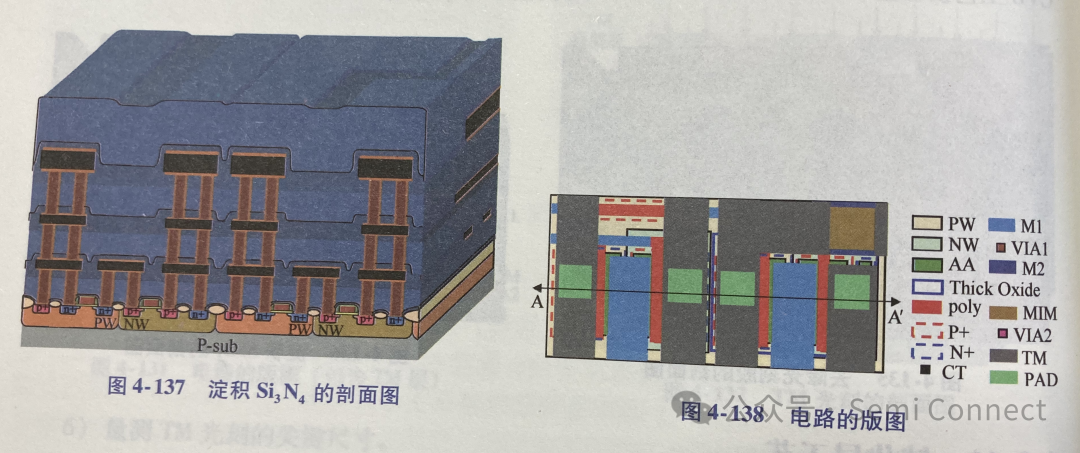

2) 淀积Si3N4。通过 PECVD淀积一层约12000A的Si3N4。利用硅烷(SiH4)、N2和NH3在400°C的温度下发生化学反应形成Si3N4淀积。Si3N4的硬度高和致密性好,它可以防止机械划伤的同时也防止水汽、钠金属离子渗人。图4-137所示为淀积Si3N4的剖面图。

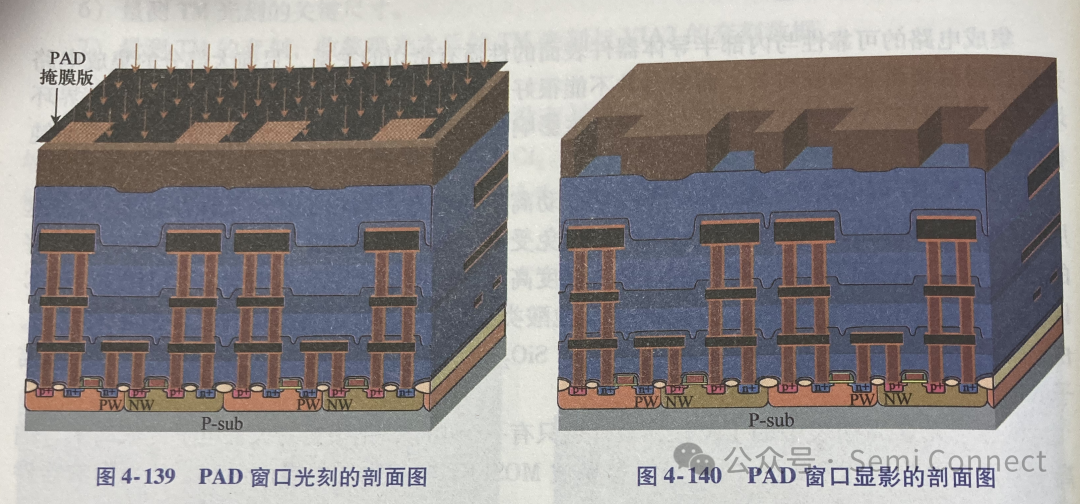

3) PAD 窗口光刻处理。通过微影技术将PAD窗口掩膜版上的图形转移到晶圆上,形成 PAD窗口光刻胶图案,非PAD窗口区域上保留光刻胶。TM 作为PAD窗口光刻曝光对准。图4-138所示为电路的版图,与图4-131比较,它多一层PAD,工艺的剖面图是沿AA'方向。图4-139所示 PAD窗口光刻的剖面图。图4-140所示力 PAD 窗口显影的剖面图。

4)量测PAD窗口的套刻,收集曝光之后的PAD 窗口光刻与TM 的套刻数据。

5)检查显影后曝光的图形。

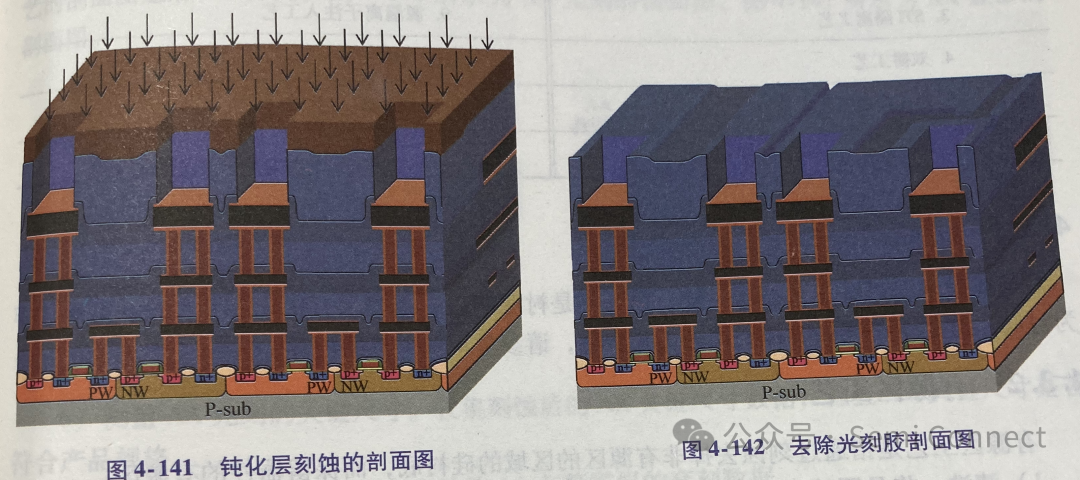

6)PAD窗口刻蚀。利用干法刻蚀将没有被光刻胶覆盖的区域的钝化层去除,形成绑定的窗口,作为顶层金属接受测试的连接窗口,或者是封装线的连接窗口。保留有光刻胶区域的钝化层。刻蚀的气体是CHF3和CF4。刻蚀最终停在TiN上防止损伤顶层金属。终点侦查器会侦查到刻蚀氧化物的副产物锐减。图4-141所示为钝化层刻蚀的剖面图。

7)去除光刻胶。除了前面提到的干法刻蚀利用氧气形成等离子浆分解大部分光刻胶,还要通过湿法刻蚀利用有机溶剂进行清洗。图4-142 所示为去除光刻胶的剖面图。

8)退火和合金化。通过高温炉管,在400°C左右的高温环境中,通入H2和N2使金属再结晶,改善钝化层的结构使钝化层更致密,释放干法刻蚀残留的电子和释放金属的应力。

9)WAT测试。通过测试程序测试每片圆片上、下、左、右和中间五点的PCM的电性参数数据。检查它们是否符合产品规格,如果不符合规格,不能出货给客户。通过收集这些数据可以监控生产线上的情况。

10)出厂检查。FAB生产出厂的最后检查,生产人员通过显微镜的随机检查,是否有划伤。

-

氧化层制备在芯片制造中的重要作用2025-05-27 1280

-

芯片制造中的阻挡层沉积技术介绍2025-05-03 2855

-

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺2024-12-30 3211

-

芯片制造-半导体工艺制程实用教程2009-11-18 72218

-

GPP-玻璃钝化二极管2011-05-13 12119

-

板上芯片封装的焊接方法及工艺流程简述2012-08-20 2735

-

霍尔IC芯片的制造工艺介绍2016-10-26 6611

-

芯片制造全工艺流程解析2020-12-28 18988

-

芯片制造过程中铝层与钝化层之间存在分层现象吗?2022-07-12 13919

-

PCB制造工艺简述2009-05-16 788

-

PCB 制造工艺简述2016-06-15 893

-

采用标准的CMOS工艺和掩膜技术制造而成的NEMS传感器2017-10-19 8184

-

钝化层刻蚀对厚铝铝须缺陷影响的研究2018-03-06 7994

-

PCB 制造工艺简述.zip2022-12-30 414

-

集成电路制造中Bosch工艺的关键作用和流程步骤2025-12-26 182

全部0条评论

快来发表一下你的评论吧 !