TMS320C6678存储器访问性能 (下)

电子说

描述

1. DMA访问存储器的性能

EDMA3架构支持很多功能,可以实现高效的并行数据传输。本节讨论影响它性能的很多因素,如存储器类型,地址偏移等。

1.1 DMA传输的额外开销

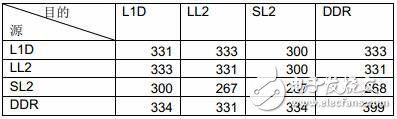

一般的传输时延被定义为EDMA被触发到真正的数据传输开始的时间。由于数据传输开始的时间无法用简单的方法测量,所以我们用最小数据单元的传输完成时间来代表DMA传输的时延或额外开销。根据不同源/目的地址的组合,这个值会有所不同。表4列出了在1GHz C6678 EVM(64-bit 1333MTS DDR)上测得的从EDMA触发(写ESR)最小数据传输(1 word)到EDMA 传输结束(读到IPR=1) 的平均的时钟周期数。

表4 EDMA CC0传输的额外开销

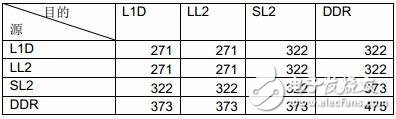

表5 EDMA CC1和EDMA CC2传输的额外开销

由于EDMA CC0 连接到离SL2 和DDR 比较近的内部总线交换网络,因此它访问SL2 和DDR 额外开销比较小。而EDMA CC1 和CC2 连接到离DSP 核的L1 和LL2 比较近的内部总线交换网络,所以它们访问L1 和LL2 的额外开销比较小。

IDMA 一般用来在LL2 内部拷贝数据,测试得到的IDMA 的平均额外开销是61 个时钟周期。

传输的额外开销是小数据量传输要考虑的重要因素。单个数据单元的传输时间完全由DMA 的额外开销决定。所以,对于小数据量的拷贝,我们需要在用DMA 和用DSP 核之间做权衡选择。

1.2 EDMA 10 个传输引擎的区别

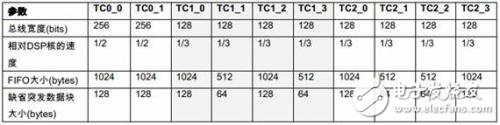

C6678 上包含10 个EDMA3 TC (Transfer Controller) 。这10 个传输引擎并不完全相同。Table 6 总结了它们之间的区别。

表6 EDMA 传输引擎之间的区别

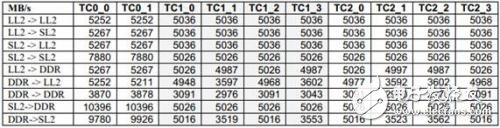

表7 比较了在1GHz C6678 EVM(64-bit 1333MTS DDR)上测得的各个EDMA TC 的最大吞吐量。测试的参数是ACNT=1024,BCNT=128,AB_Sync(一次传完ACNTxBCNT)。

表7 1GHz C6678 上EDMA TC 吞吐量比较

对SL2 和DDR 之间的传输,TC0_0 和TC0_1 能达到的吞吐量是其它TC 的两倍。在本文其它部分,如果没有特殊说明,EDMA 性能数据都是在TC0_0 上测得的。

1.3 EDMA 带宽和传输灵活性的权衡

EDMA3 支持很多灵活的传输参数配置。多数配置情况下EDMA 可以充分利用存储器带宽;但在某些情况下,传输性能可能会有所下降。为了设计高效的系统,我们需要理解什么样的配置能够实现高效的传输,而某些情况下必须在灵活性和效率之间做权衡。

1.3.1 第一维大小 (ACNT) 的考虑(突发数据块大小)

为了充分利用传输引擎的带宽,传输尽量大的数据块是非常重要的。

为了充分利用128-bit 或256-bit 的总线,ACNT 应该是16 bytes 的整数倍;为了充分利用EDMA的突发数据块,ACNT 需要是64 bytes 的整数倍;为了充分利用EDMA FIFO,ACNT 应该至少是512 bytes。

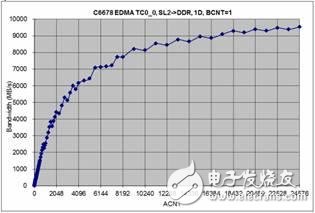

图7 画出了在1GHz C6678 EVM(64-bit 1333MTS DDR)上,从SL2 到DDR 传输1~24K bytes 数据时测得的吞吐量。

图7 ACNT 对EDMA 效率的影响

从测试结果可以看出,ACNT 越大,带宽的利用率越高。

1.3.2 二维传输的考虑(传输优化)

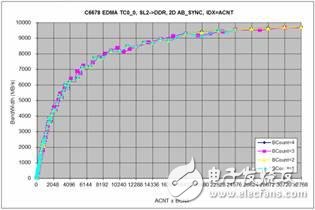

如果2D 传输 (AB_Sync)是线性的 (BIDX=ACNT),并且ACNT 是2 的幂次方,EDMA 会把这个2D 传输优化为1D 传输。我们在1GHz C6678 EVM(64-bit 1333MTS DDR)上测试了不同的ACNT 和BCNT 的组合;图 8是线性2D 传输的测试结果,它说明,不管BCNT 是多少,带宽由ACNTxBCNT 的乘积决定。

图8 线性 2D 传输

如果2D 传输不是线性的,带宽的利用率完全有ACNT 决定(参见图 7)。

- 相关推荐

- 热点推荐

- 存储器

- TMS320C6678

-

想建立一个TMS320C6678的工程,但是DEVICE选择的时候没有TMS320C6678的选项,能指点一下吗?2018-06-19 2052

-

请问SM320C6678与TMS320C6678的区别有哪些?2018-07-24 3731

-

TMS320C6678 连接CMOS摄像头的接口,请问是将摄像头连接到TMS320C6678的哪个端口?2018-08-03 3099

-

请问tms320c6678在CPCI板卡上如何设计2018-12-28 2575

-

TMS320C6678处理器的性能怎么样?2021-04-19 3177

-

TI TMS320C6678是什么?有何功能2021-12-30 2080

-

TMS320C6678的相关资料推荐2022-01-03 1780

-

TI推出适合高性能计算的8核DSP产品TMS320C6678/TMS320TCI66092011-11-22 3627

-

TMS320C6678视频编解码实现2016-01-20 1715

-

TMS320C6678的用于多核软件开发套件 (MCSDK) K的安装资料2017-10-19 1203

-

TMS320C6678处理器的VLFFT演示探讨与研究2018-01-31 5322

-

TMS320C6678存储器访问性能详细中文资料2018-04-26 2199

-

TMS320C6678 多核定点和浮点数字信号处理器2018-11-02 3454

-

TI TMS320C6678 DSP多核通信开发说明手册2022-01-06 2443

-

基于TMS320C6678的八核DSP雷达信号分选电路2023-11-06 438

全部0条评论

快来发表一下你的评论吧 !