安森美1200V EliteSiC M3e平台让平面碳化硅性能拉满

描述

本文转自电力电子网。

最近,行业内玩家8英寸碳化硅量产如火如荼的进行中,安森美(onsemi)也计划于今年晚些时候对8英寸碳化硅晶圆进行认证,并于2025年投入生产。而在栅极结构方面,平面结构和沟槽结构的争论仍在继续。两者各有其优势和劣势,选择哪种结构取决于具体的应用场景和需求,同时还要兼顾成本效益。前不久安森美推出的采用行业标准TO-247-4L封装的1200V EliteSiC M3e平台,可以说是平面结构的登顶之作,再次刷新了高耗电应用的能效。

在PCIM Asia Shenzhen 2024上,安森美电源方案事业群资深产品专家Mrinal Das博士接受媒体专访时表示,碳化硅对于电源创新应用的重要性不言而喻。入行30年,他亲眼见证了碳化硅材料的发展历程。针对当前碳化硅行业的一些热点以及市场趋势,他结合技术创新分享了自己的观点,内容涵盖IDM(垂直整合制造)模式、碳化硅平面与沟槽纷争,以及FoM(品质因数)差异的权衡等。

01此IDM非彼IDM

从硅碳化物的生产流程可以看出,从碳化硅粉末放入长晶炉,到最终产品电动汽车,整个过程包括多个步骤,如高温晶体生长、碳化硅晶锭、晶体切割、晶体抛光、晶圆制备、封装、测试和质量控制等。这些步骤确保了高质量的产品能够满足客户的需求。

安森美的“智能电源”由SiC和Si功率驱动,在全球市场位居第二位。面向未来,公司设定了25%市场份额,在市场增长趋缓之时,安森美仍有望在 2024 年实现超过碳化硅市场 2 倍的增长。Mrinal Das博士表示,安森美充分考虑了供应链的稳定与灵活性。他明确指出:“安森美具备强大的供应链垂直整合能力,这意味着我们在很大程度上能够自给自足地供应碳化硅衬底,满足内部生产需求。”

他也坦言,作为一家负责任的企业,安森美深知风险管理与多元化供应策略的重要性。因此,尽管我们拥有强大的内部供应能力,但仍“留有余量”,保留了与第三方供应商的合作渠道,以确保在市场需求发生未预见波动时,能够迅速调整并满足市场要求,降低整体生产风险。

其总体思路是,在碳化硅衬底供应上既依赖于自身强大的内部制造能力,也保持着与第三方供应商的灵活合作,以确保供应链的稳定性和韧性,为公司的长远发展奠定坚实基础。

Mrinal Das博士还深入解析了IDM模式在安森美运营中的优势与挑战,并阐述了安森美如何有效应对这些挑战,以实现持续成功。

他指出,安森美在6英寸晶圆制造领域已建立起强大的产量和产能基础,这是其市场优势之一。更重要的是,安森美通过坚定的承诺和对市场需求的高度敏感性而与众不同。基于市场需求的决策,可确保从6英寸到8英寸的过渡平稳且高效;选择对客户和自身最有价值的平台,有助于保持定价合理和供应稳定。这种保守而稳健的策略可以在市场中形成差异化竞争优势。

此外,安森美之所以相对成功,还得益于采取的“棕地扩建”策略。在全球范围内,安森美拥有多个晶圆厂,只通过少量投资即可转化为碳化硅生产能力。这种灵活性使其能够迅速响应市场需求,调整晶圆厂的使用分配。相比之下,没有现有晶圆厂基础的公司则需要进行大量的“绿地投资”,从头开始建设生产线,这不仅成本高昂,而且时间周期长。

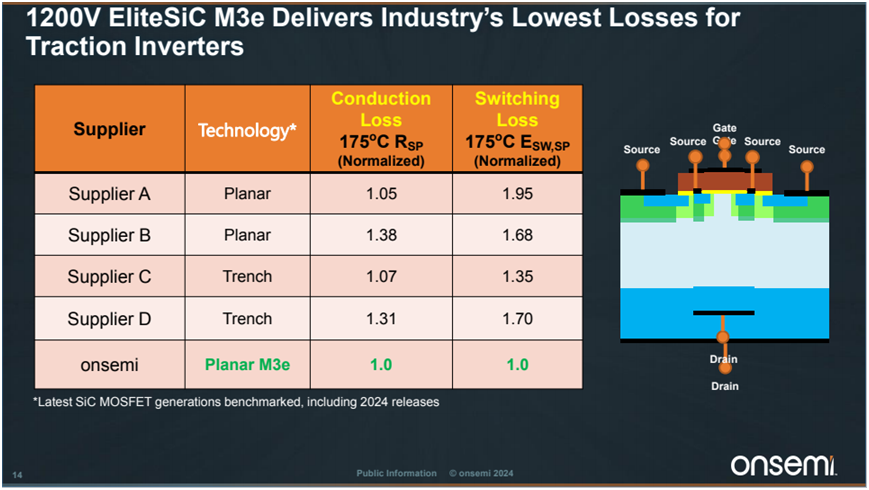

02让平面碳化硅性能拉满

安森美新推出的EliteSiC M3e技术平台以其1200V、11mΩ MOSFET裸片为核心,凭借行业领先的优值,在更高开关频率与电压下展现出卓越的性能,有效降低了功率转换损耗。其独特的平面拓扑经过现场验证,以独特方式降低了导通损耗和开关损耗,为电力电子行业树立了质量与可靠性的新标杆。

与前几代产品相比,M3e平台不仅将电气化应用的传导损耗减少了30%,开关损耗降低了50%,还以业界最低的具有短路能力的比导通电阻(RSP)赋能牵引逆变器市场。值得一提的是,M3e以更低的每千瓦成本提升了下一代电气系统的性能和可靠性,同时减少了无源元件和热管理成本,为用户带来前所未有的成本效益。

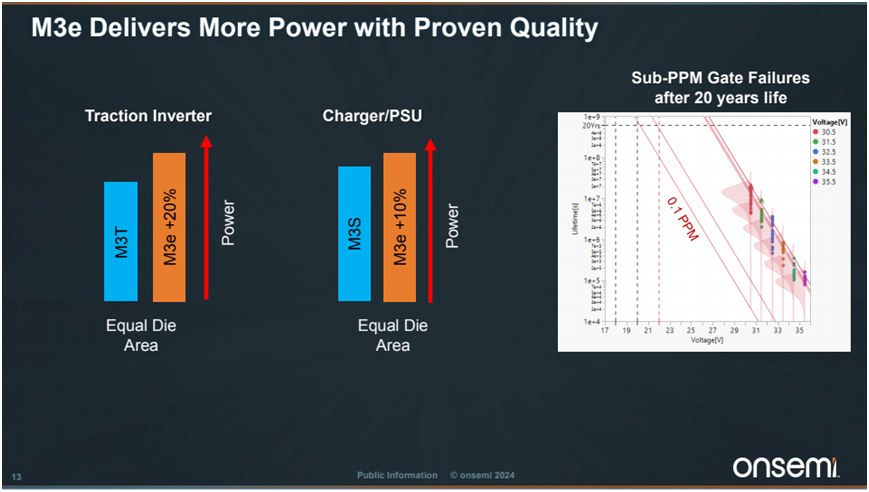

据介绍,采用安森美先进的分立和功率模块封装,1200V M3e裸片与之前的EliteSiC技术(M3T)相比,能够提供更大的相电流,使同等尺寸主驱逆变器的输出功率提升约20%,而在充电器和PSU(电脑电源)中,功率提高了10%。这意味着,在输出功率不变的情况下,新设计所需的碳化硅材料可以相应减少,成本也更低,且能实现更小、更轻、更可靠的系统设计。

在质量保证方面,M3e 20年寿命后的栅极故障低于PPM,因此能够让客户的产品在市场中脱颖而出。

Mrinal Das博士指出,在当前1200V碳化硅器件竞争激烈的市场环境下,许多厂商都在努力降低导通损耗和开关损耗。然而,对于最终用户而言,他们更看重的是实际结果和性能提升。目前的方案,要么是在固定的裸片数量的情况下去提升功率水平,要么是在指定的功率水平之上来减少裸片数量。

M3e顺应了市场趋势,其核心目标是实现最佳的导通损耗和开关损耗。它通过裸片层面的优化,显著降低了整体导通电阻,从而提高了系统开关效率,提升了整体性能表现。同时,通过采用更少裸片的并联设计,简化了系统结构,提高了系统的可用性和稳定性。

Mrinal Das博士介绍说,同样是平面结构,M3e采用了明显不同的结构,可以确保该平台的坚固性和稳定性,使其成为关键电气化应用的首选技术。M3e业界最低的损耗主要归功于其独特的晶胞(Unit Cell)设计和内部创新。

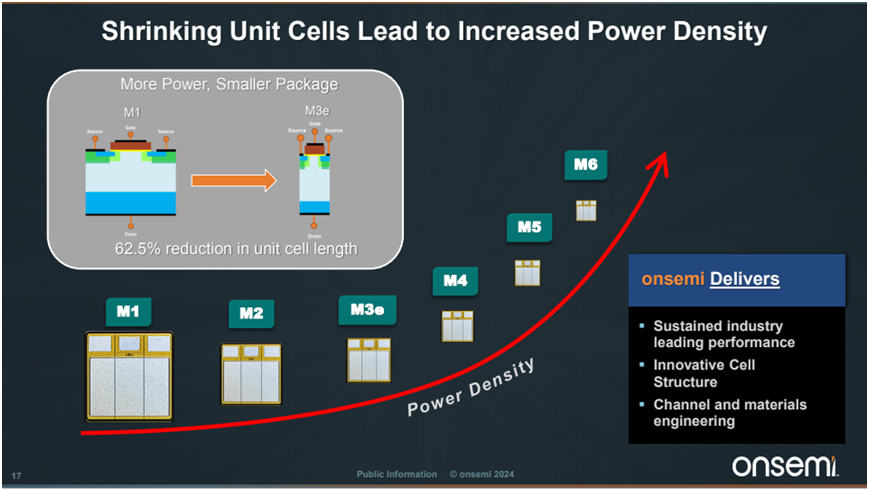

他解释说,晶胞在功率MOSFET设计中非常关键,它是整个芯片上不断复制的微型MOSFET的基本长度,包括两个导电通道。事实上,尽可能缩小晶胞就可以增加功率密度。晶胞体积越小,每个芯片上可以放置的MOSFET就越多,而这些MOSFET是并联的,所以整体的器件的电阻就会下降,晶胞本身的电阻也会下降。这两种效应组合起来,就能够进一步降低整个导通电阻,这是M3e导通损耗达到业界最低水平的主要原因。

从M1到M3e,晶胞的长度减少了62.5%,从而实现了更大的功率和更小的封装,功率密度也在不断提升。未来,这一过程将继续演进,为市场提供行业领先的可持续性能、创新的晶胞结构以及渠道与材料工程。

另外,每个器件内部的开关损耗主要由电容决定,而主要的电容是栅极到漏极的电容。在M3e晶胞结构上进行的内部创新,使得栅极到漏极的电容更低,从而降低了整体的开关损耗。

那么,安森美是怎么把晶胞做到很小的?Mrinal Das博士回应道,安森美通过投资先进的晶圆厂工具和技术,不断拓展现有生产设备的能力,确保能够实现微型和微观功能的精确制造。这一策略使得安森美能够成功地将MOSFET的晶胞体积做得非常小,最大化利用了每一个芯片空间,提高了功率MOSFET的性能,并实现了大规模批量化生产。这种对技术创新的持续投入和追求,是安森美在行业中保持领先地位的关键因素之一。

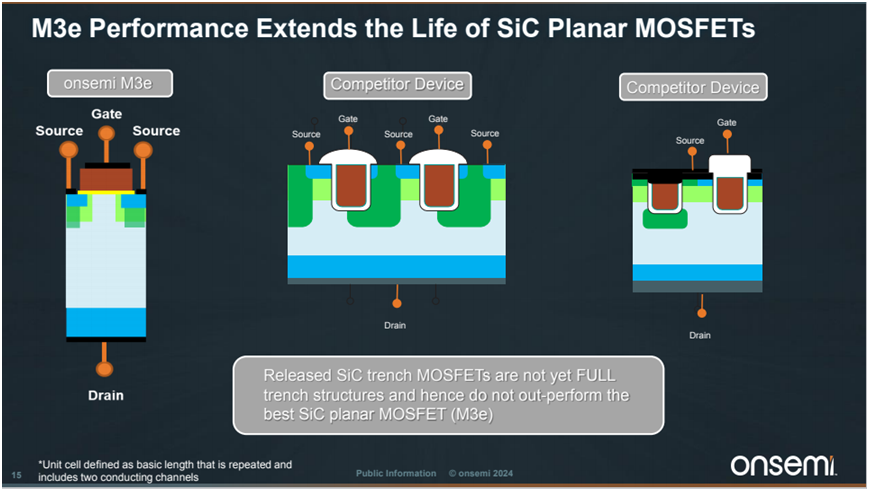

03平面结构仍优于沟槽结构

虽然沟槽拓扑的技术难度比较大,但一般来讲它更能够节省碳化硅材料,进而带来成本效益。不过,安森美认为,目前沟槽的MOSFET还不是全沟槽结构,还难以体现沟槽结构的优势。其中一些结构采用多个源极和栅极,有的则只有一个源极和一个栅极,并没有达到最佳性能。

Mrinal Das博士对比了平面拓扑结构与沟槽拓扑结构,详细阐述了安森美在MOSFET拓扑结构选择上的考量。他指出,平面拓扑结构的主要优势在于栅极氧化层的可靠性。栅极氧化层是平面拓扑MOSFET中最关键且最薄弱的环节。经过40年的研发和超过15年的市场验证,平面拓扑结构在质量和可靠性方面已经得到了充分证明。

在讨论碳化硅与硅材料在电力电子器件中的显著差异时,他深入阐述了电场强度、栅极氧化物保护以及沟槽技术的复杂性。首先,相比传统硅材料,碳化硅材料在电场强度上具有显著优势,其峰值电场强度可达到每厘米3MV(200-300kV/cm),是传统硅材料的10倍以上。这一特性使得碳化硅在高压、高功率应用中具有更高的效率和更小的体积,但同时也带来了新的技术挑战。

在沟槽器件设计中,栅极氧化层的位置至关重要。在平面结构中,栅极氧化物位于低电场区,相对安全。而在沟槽结构中,栅极氧化物暴露在高电场区,要求必须采取特殊措施来保护其免受高电场的影响,以防止栅极氧化层失效。这种保护在碳化硅器件中尤为困难,因为碳化硅的栅极保护机制与硅不同,无法直接借鉴硅材料的经验。

此外,栅极氧化物在碳化硅沟槽技术中具有独特性。与传统的硅平面结构不同,碳化硅沟槽结构在侧壁上交替堆叠硅和碳层,这种结构使得栅极氧化物表面引入了碳元素,从而改变了氧化物的性质。这种全新的氧化物不仅与平面结构中的氧化物不同,也与传统硅功率器件中的氧化物大相径庭。因此,沟槽技术在碳化硅器件中的推广遇到了诸多延误,因为所有的研究——包括制造性、可靠性和现场性能——都需要从头开始,无法直接利用硅器件的成熟技术。

他强调,在碳化硅器件中采用沟槽技术所面临的两大技术挑战:一是如何在高电场环境下有效保护栅极氧化层,因为栅极氧化层一旦暴露在磁场或电场中,很早就会出现失效的情况,其寿命会大大缩短。

二是如何应对沟槽结构中全新氧化物带来的制造、可靠性和性能问题。这些挑战要求在研发过程中投入更多的时间和精力,以积累必要的经验,推动碳化硅沟槽技术的进一步发展。

对于M3e这样的平面体结构MOSFET,Mrinal Das博士自信地表示,其性能甚至优于当前的沟槽器件。而沟槽结构在碳化硅面积利用方面并未展现出显著优势,尚未超越平面拓扑结构。

他预测,未来更多供应商可能还会选择平面拓扑结构,除非沟槽结构在性能上能够全面超越。“只有当沟槽技术的产品性能能够全面超越平面拓扑结构时,我们才会考虑切换到沟槽技术。这表明我们在技术研发上持谨慎态度,注重产品的长期可靠性和性能表现。”他强调。

他还提到,市场上其他竞争对手的沟槽技术产品之所以性能不如M3e,主要原因是这些产品并未采用全沟槽技术。通过对采用的技术、导通损耗和开关损耗的对比,可以看到采用平面结构的M3e均优于其他供应商的产品,包括2024年发布的产品。

在他看来,M3e标志着平面结构MOSFET性能的顶峰。如果要在未来的产品中实现更高的性能突破,的确要转向沟槽技术,但前提是这种技术需要实现百分之百的沟槽利用率,以充分发挥碳化硅的潜力。

因此,安森美目前正全力以赴地应对新的挑战,解决新的栅极氧化物的保护问题,同时实现百分之百的沟槽利用率。

04FoM因应用场景而异

在探讨碳化硅材料在不同应用场景下的性能优化时,Mrinal Das博士说,安森美凭借其深厚的技术积累和敏锐的市场洞察,成功地在多个领域实现了卓越的性能表现。无论是硬开关、软开关,还是高频、低频环境,安森美都能通过精准的技术调整和产品优化,确保每一款SiC MOSFET都能在各个使用场景中表现出色。

1200V EliteSiC M3e实现了牵引逆变器业界最低的损耗,安森美充分利用了碳化硅材料低开关损耗的特性,通过精细调控导通电阻(Rds)和栅极到漏极的电荷(Qgd),有效降低了器件在开关过程中的能量损失,使牵引逆变器的整体效率显著提升。特别是在高功率密度和高效率要求的场合,这种优化显得尤为重要。

车载充电器高频应用场景则面临更为复杂的挑战,不仅需要处理高频率的开关操作,还需要在硬开关和软开关两种模式下实现高效转换。为此,安森美采用了创新的图腾柱(Totem Pole)结构,并进一步优化了Rsp(导通损耗与硬开关损耗的比例)和栅极驱动器损耗。通过精确计算总栅极电荷,能够准确预测并降低栅极驱动器电路中的能量损失,从而确保车载充电器在不同工作频率下都能保持高效稳定的性能。

安森美深知不同应用场景下FoM的差异。在M3e等产品的研发过程中,安森美不仅关注单一的性能指标,更注重整体性能的最优化。通过跟踪和参考Rds、Qgd、Rsp等关键参数,能够确保新技术在开发过程中始终围绕用户需求和市场趋势进行迭代和优化。这种以用户需求为导向的技术开发策略,使安森美的SiC MOSFET在多个应用领域都展现出了卓越的性能和广泛的应用前景。

05碳化硅为未来电源创新赋能

Mrinal Das博士告诉记者,安森美也在利用摩尔定律思维加速碳化硅技术的迭代。其每一代碳化硅技术都会优化单元结构,在更小的面积上高效传输更大的电流,从而提高功率密度;同时结合自有的先进封装技术,最大限度提升性能并减小封装尺寸。这些计划于2030年前推出的多款高性能新品,将进一步应对全球能源需求的激增。

他强调,碳化硅在功率密度与效率上的卓越表现,使其成为电动汽车、电网等关键领域的理想选择,并预示其在未来新兴应用场景中的广阔潜力。

“只有凭借深厚的功率半导体技术积累,不断突破技术瓶颈,确保设计与制造的全面掌控,才能加速新一代碳化硅产品的市场化进程。”他相信,未来的下一代碳化硅技术在工业领域的采用和发展将会由这样的公司来引领。

-

安森美1200V碳化硅MOSFET:NTH4L013N120M3S的特性与应用分析2025-12-04 904

-

安森美推出基于碳化硅的智能功率模块2025-03-19 1426

-

安森美加速碳化硅创新,助力推进电气化转型2024-07-22 547

-

安森美1200V碳化硅MOSFET M3S系列设计注意事项和使用技巧2024-03-28 2819

-

安森美发布了第二代1200V碳化硅 (SiC) MOSFET—M3S2024-03-26 4138

-

安森美与博格华纳扩大碳化硅战略合作,协议总价值超10亿美元2023-07-19 1369

-

安森美推出最新一代1200 V EliteSiC 碳化硅(SiC)M3S器件2023-05-25 897

-

安森美和极氪签署碳化硅功率器件长期供应协议2023-05-11 1136

-

功率模块中的完整碳化硅性能怎么样?2023-02-20 9388

-

新品发布 | EliteSiC碳化硅系列方案带来领先业界的高能效2023-01-05 1009

-

650V/1200V碳化硅肖特基二极管如何选型2020-09-24 2788

-

1200V/10A碳化硅肖特基二极管2020-03-13 2263

-

基本半导体发布高可靠性1200V碳化硅MOSFET2019-01-17 11025

全部0条评论

快来发表一下你的评论吧 !