浅谈Silicon Photonics芯片

工艺/制造

描述

Silicon Photonics芯片吸引着公司和研究人员的主要原因是成本低,功耗低,其中Si是导光的良好材料。随着CMOS晶体管尺寸逐渐减小,光学器件却无法继续缩减,成了研究人员极其关注的一个研究方向。

其实,从上个世纪八九十年代开始,谈“摩尔定律”色变的各位先行者就开始探索半导体芯片的继任者,企图在硅芯片发展到物理极限时取而代之。笔者还记得当初上学时,老师告诉我们CMOS工艺发展到十几纳米左右就会到物理极限。结果现在7nm的芯片都造出来了,代替CMOS工艺的成熟技术还没有大规模应用。

这里,我们就介绍一下一种传说中在“More than Moore”中的技术。Silicon Photonics。

早在1969年,贝尔实验室的S.E.Miller首次提出了集成光学的概念。随着微电子集成电路的发展,1972年,S.Somekh和A.Yarive提出了在同一半导体衬底上集成光学器件和电器件的设想。上世纪90年代,随着硅基集成电路尺寸逐渐减小,其特征尺寸已进入光通讯波长范围。另外,Si和SiO2材料之间的折射率差别较大,(Si大约3.45,SiO2大约1.44),容易发生全反射,这也有利于减小光集成器件尺寸,提高光芯片的密度。然而,从另一方面来说,在CMOS晶体管尺寸已经缩小到10nm左右的今天,由于光学衍射效应,集成光学器件的尺寸无法继续缩小,这也在一方面限制了硅光芯片的发展。因此,目前所说的Photonic Integrated Circuits (PIC),都是指在片上集成光连接和光电转换器件,再转换成电学信号用CMOS集成电路进行处理。而不再是如最初提出时一般,用光学器件来完全取代晶体管。

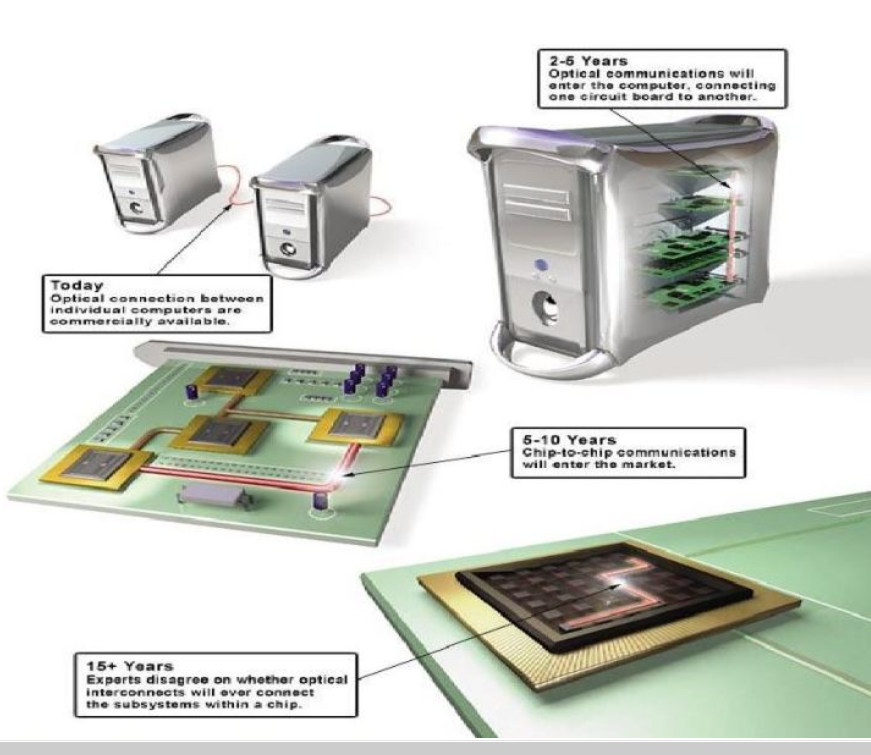

正如上图所示,现在我们也只是发展到光纤到户,许多data center会用到光纤的板级互连。但最下面的芯片级通讯,现在各大公司和科研院所已经有了demo的chip,100G的模块已经基本成熟,但距离市场级的全面应用还尚有很大的距离。(PS:上面那篇文章发表于2002年,现在15年过去了,距离该作者的预言尚未完成一半,不知道该是庆幸还是悲伤。。。)

其实,说了这么多,Silicon Photonics能够让许多公司和研究人员对此趋之若鹜的主要原因就在于成本低,功耗低,而且Si是导光的良好材料。由于SOI工艺的发展,一般的SOI上Si的光波导的损耗已经可控制在2、3dB/cm。但是,现在还有一些缺陷限制了它的广泛使用:

如何光电互连:即光源Laser和Photodetector。Si材料本身是间接带隙,因此现在所有光源都必须添加其他材料进行制作,比如III-V或Ge,这意味着无法在与标准CMOS SOI工艺上制作全部的光学器件。这也同时引入了一系列的成本问题。

如何控制光:是指控制波长的偏差。由于光学器件是与尺寸,厚度,doping等工艺参数息息相关。比如根据测试结果可知,Grating coupler的poly silicon厚度偏移10%,coupling的波长会移动50nm左右。再比如片上的Photonic Modulator,很多还尚且需要Heater来进行调节。这也给系统的复杂度和成本带来了挑战。

如何集成:随着CMOS晶体管尺寸逐渐减小,而光学器件由于波长和衍射的限制却无法继续缩减,这也是比较有趣的一点。此外,在光芯片和电芯片之间的package也是一个值得研究的方向。

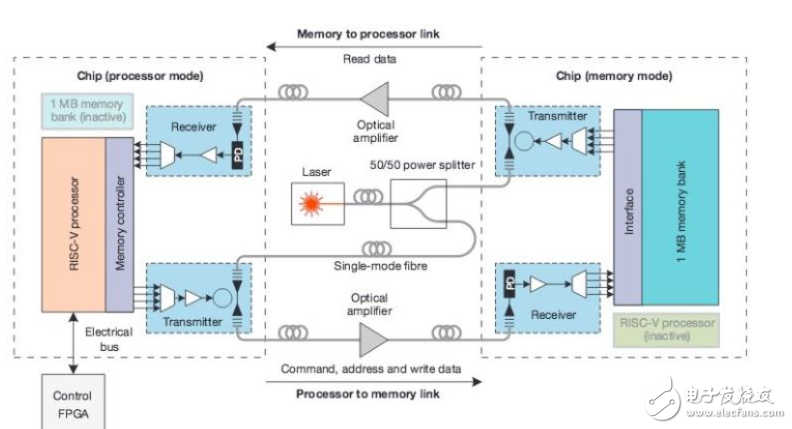

下面举一个SiPh Communication芯片的例子:

Source: C. Sun, et al. “Single-chip microprocessor that communicates directly using light”, Nature, 2015.

该文章公布了一个可以称之为Microprocessor的系统,理论上传输速度550Gb/s。有兴趣的同学可以去找来看一下(PS:其实笔者不清楚为什么它的传输波长不在业界通用的1550nm或1310nm)。对于这种所谓的光通讯,其实笔者觉得可以这样来简易理解:我们把它分成光和电两部分来看。电信号的处理部分,其实就是Serdes加上Digital Processing;而光学部分的功能,说白了就是先用电信号把光信号进行调制,发送出去后送到接收端的Photodetector,再转化成电信号。只不过每一步都有一些特别的模块用来调节。

总之,希望能通过这篇简单的介绍,能够让大家对Silicon Photonics有一个大体的了解。倘若有同学比较感兴趣,期待多多交流,共同进步。

-

C8051单片机,Silicon labs 产品2011-11-19 2603

-

silicon node2013-04-02 4983

-

手机硬件知识浅谈2013-05-15 33469

-

cameralink 传输 silicon microdisplay设置2015-12-23 4290

-

Silicon Image数字视频芯片SiI9616使用2016-04-27 3230

-

OMAPL138 Silicon Revision问题2018-06-21 1395

-

ON Photonics West的安森美半导体2018-10-11 3023

-

Silicon IDE如何安装?2020-11-06 1923

-

请问Silicon Labs时钟芯片Si5332如何更改时钟输出频率?2023-10-28 851

-

Silicon Labs单芯片EDGE收发器容易使用2006-03-13 905

-

ADI收购Vescent Photonics公司激光波束转向技术2016-11-18 1461

-

Convergent-photonics中文宣传册2017-01-14 851

-

浅谈国产视频转换芯片大全概述如下;2022-12-30 16282

-

浅谈PHY芯片UTP接口直连(不使用变压器)的设计2024-03-07 806

-

Silicon PIN 二极管、封装和可键合芯片 skyworksinc2025-07-14 89

全部0条评论

快来发表一下你的评论吧 !