高速信号的频率点和衰减值

描述

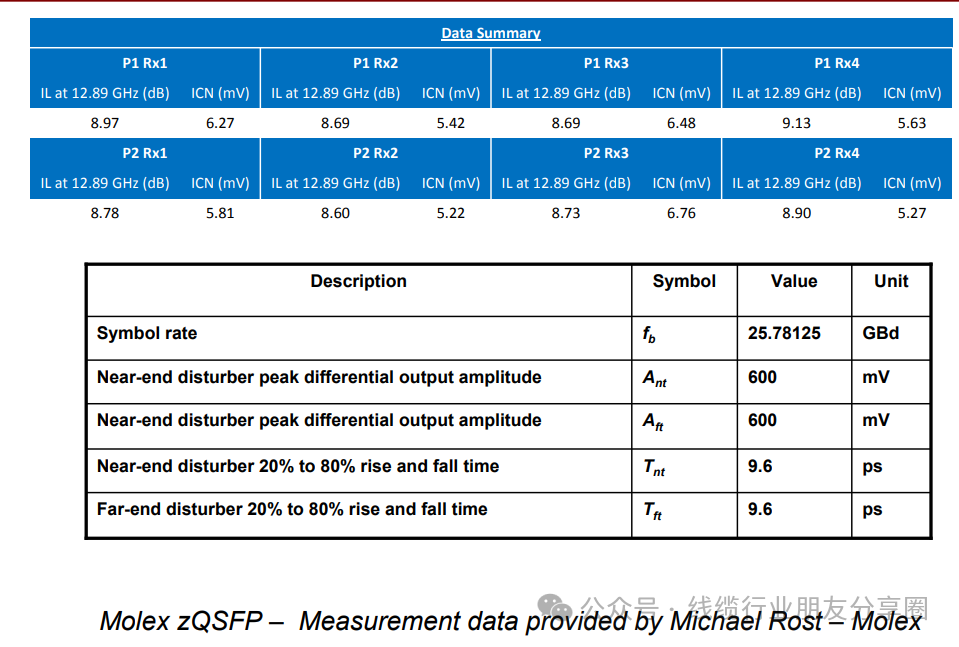

高速信号损耗我们的研发工程师经常就说一个频率点和对应的衰减值,16G看到5.6dB;或者你们把铜丝加大,看能不能干到5.1dB,按照这两个规格分别报价和出样品,很多初入高速线缆行业的工程师听到是云里雾里,什么鬼玩意,当我们将25Gbps信号速率升级到如今的56Gbps信号速率时,由于PAM4(Pulse Amplitude Modulation)信号制式的引入(IEEE 802.3BS小组),以太网Serdes链路上传输的信号基频点也仅仅是从12.89GHz上移到13.28GHz(关键频点),今天我们就讨论下这个,具体要看哪个频点的问题,为什么高速讯号看频点,频点和衰减值都是什么玩意,今天一起找找资料学习了解下.

高频参数的科普

我们经常说25G的线缆,测试频点在12.89G,从理论上来讲这两个不是一个东东,25G是说这对差分信号的传输速率,单位是bps,也就是我们常说的比特率。而协议上测试频率12.89G指的是频率,单位是Hz。25G信号的bps和12.89G的Hz之间有什么关系呢?要看编码类型,要看码型,NRZ是一半,PAM4是四分之一,以此类推。因为频率指的是完成一个信号周期,比特率是每个电平都会计算。 如果是双边沿采样,数据传输速率是通道带宽的2倍,如果是单边沿采样,那数据传输速率就是通道带宽。备注:数据传输速率是数字量概念,通道带宽通常是模拟概念

信号频率和传输速率的换算公式:

速率=频率*每个周期中传输的比特数具体公式为:速率=频率*log2(传输的符号数)其中,频率单位为赫兹(Hz),速率单位为比特每秒(bps),log2表示以2为底的对数。例如,设信号频率为10kHz,每个周期中传输的比特数为2,则速率为:速率=10*2=20kbps。又例如,设信号速率为100Mbps,传输的符号数为256,则频率为:频率=100M/log2(256)=12.5MHz。

通道带宽: 简单讲就是我们修的高速公路,如果一车道就是一个带宽,如果几车道,就乘以相对应的车道,得出来就是可以跑的带宽,专业的书本上一般都这么写,信道可以不失真地传输信号的频率范围,为不同应用而设计的传输媒体具有不同的信道质量,所支持的带宽有所不同,信道容量:信道在单位时间内可以传输的最大信号量,表示信道的传输能力,信道容量有时也表示为单位时间内可传输的二进制位的位数(称信道的数据传输速率,位速率),以位/秒(b/s)形式予以表示,简记为bps;举例说明:

PCIe是串行总线,PCIe1.0的线上比特传输速率为2.5Gb/s,物理层使用8/10编码,即8比特的数据,实际在物理线路上是需要传输10比特的,因此:PCIe1.0 x 1的带宽=(2.5Gb/s )/ 10bit =250MB/s

这是单条Lane的带宽,有几条Lane,那么整个带宽就是250MB乘以Lane的数目。PCIe2.0的线上比特传输速率在PCIe1.0的基础上翻了一倍,为5Gb/s,物理层同样使用8/10编码,所以:PCIe2.0 x 1的带宽=(5Gb/s )/ 10bit = 500MB/s。同样,有多少条Lane,带宽就是500MB/s乘以Lane的数目。PCIe3.0的线上比特传输速率没有在PCIe2.0的基础上翻倍,不是10Gb/s,而是8Gb/s,但物理层使用的是128/130编码进行数据传输,所以:PCIe3.0 x 1的带宽=(8Gb/s)/ 8bit = 1GB/s。同样,有多少条Lane,带宽就是1GB/s乘以Lane的数目。由于采用了128/130编码,128比特的数据,只额外增加了2bit的开销,有效数据传输比率增大,虽然线上比特传输率没有翻倍,但有效数据带宽还是在PCIe2.0的基础上做到翻倍。这里值得一提的是,上面算出的数据带宽已经考虑到8/10或者128/130编码,因此,大家在算带宽的时候,没有必要再考虑线上编码的问题了。和SATA单通道不同,PCIe连接可以通过增加通道数扩展带宽,弹性十足。通道数越多,速度越快。不过,通道数越多,成本越高,占用更多空间,还有就是更耗电。因此,使用多少通道,应该在性能和其他因素之间进行一个综合考虑.

速率 :开车在高速公路上跑,跑多快因素很多,主要有车道设计是否合理,一个设计跑300码的玛莎拉蒂跑车,你去我们乡下的马路跑也没毛线用,本身车子的质量也很关键,线材的导体和特性设计等都会直接影响,专业书本在介绍的时候,一般这么写,信道在单位时间内可以传输的最大比特数,信道容量和信道带宽具有正比的关系:带宽越大,容量越大,理论计算4M宽带的公式是:4*1024/8 = 512K/s ,也就是说理论情况下4M宽带网速下载速度最高可以达到512k/s, 基本上是这。

频率: 目前经常搞混的参数之一,RF系列的同轴线材中是最多引用频率,视频信号传输一般采用直接调制技术、以基带频率(约8MHz带宽)的形式,最常用的传输介质是同轴电缆,同轴电缆是专门设计用来传输视频信号的,其频率损失、图像失真、图像衰减的幅度都比较小,能很好的完成传送视频信号的任务,但是现在采用对绞线版本也可以解决音视频传输问题,故很多场合在成本问题上,会来考虑对绞线版本,对于差分对的传输线,传输速率或带宽(Mbps)=时钟频率(MHz)位宽通道数*每时钟传输数据组数(cycle),480Mbps=240MHz*1*1*2, 每个时钟周期传送2次数据(这跟编码方式有关USB为NRZI),也即当传输速率为480Mbps时,对应的时钟频率为240MHz,而且这个240MHz的时钟频率还是USB芯片里面晶振经过倍频得到的,实际USB晶振有12MHz,24MHz,48MHz等

PCIE信号,有很多TX和RX的高速链路,不知道大家有没有注意,其实还有一对100MHz的参考的时钟。在高速信号发送过程中,发送芯片里有一个叫PLL(锁相环)的模块,会采样100MHz的时钟后进行倍频,倍频到可以采样到高速信号的频率,然后时钟内嵌到数据通道中一起发送,到了接收端之后,又有一个新的模块叫CDR模块,中文名叫时钟恢复模块。它主要是负责从收到的数据信号中恢复出内嵌的时钟,并用恢复出来的时钟对数据信号进行采样识别。一般我们做这种高速信号仿真只会关注接收端的波形或者眼图,讯号在传输过程中由于受到内部结构稳定性和外部环境的影响,数据线会受到衰减,其从发射端的讯号在接收端就有失真的现象,接收信号就变得不那么完美了,这个是正常的现象。除了关心接收端信号之外,你们有看过接收端进行CDR模块恢复出来的时钟信号吗?把恢复出来的时钟信号和 接收端的高速信号放在一块看 ,在截取的这一串数据信号中,时钟信号通过上升和下降沿对数据信号进行采样。对于高速信号来说,每一位的“1”或者“0”的位宽的倒数就是我们的速率25Gbps。那问题来了,时钟信号的上升和下降沿都对数据进行采样,那么时钟频率是多少呢?

为什么只看关键频点

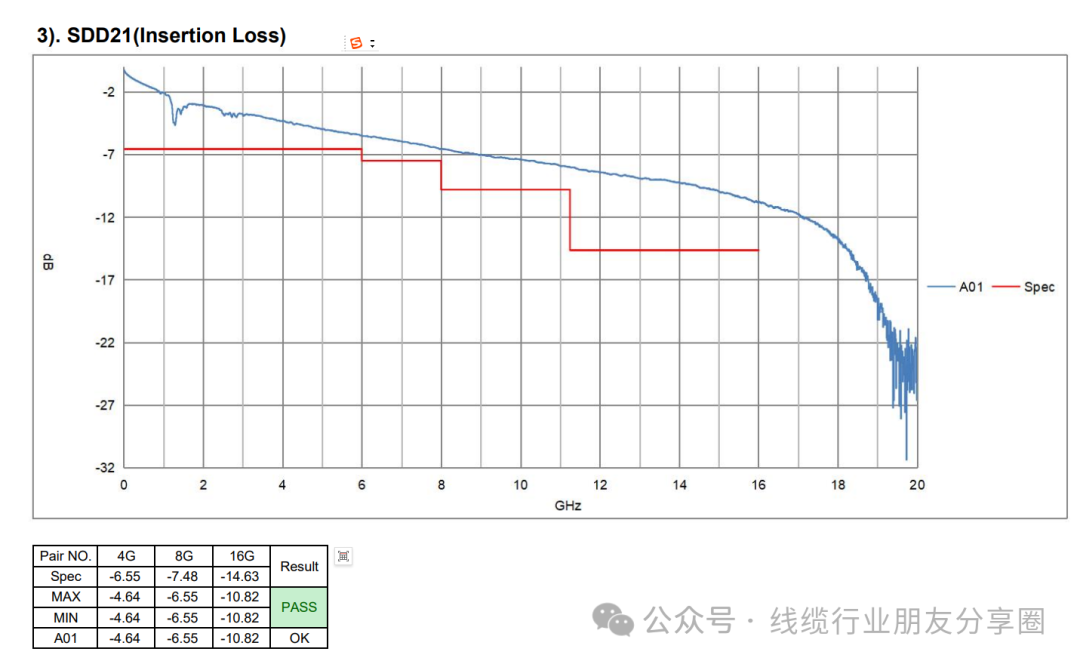

上面是比较理想情况下的channel的损耗参数,在16GHz是10.82dB的损耗,按照线性度来说32GHz处应该就是21.64dB了。那怎么证明我们是看16GHz处-10.82dB的损耗,而不是看32GHz处-21.64dB的损耗呢?我们看这个测试图形在16GHz位置还是-10.82dB,但是过了20GHz后,立马变成30dB的超大衰减,在20GHz处也是27dB。那如果20Gbps信号的损耗真的是要看到20GHz频点的话,27dB的衰减在眼图中估计就不成型咯。说明了20Gbps的损耗肯定就不是看20GHz频点了,另外12.5GHz频点之后的损耗对眼宽影响是巨大的( 1倍频之外主要影响上升沿 )。

上升沿边很重要

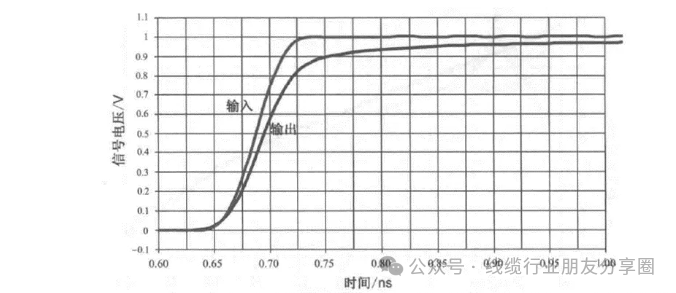

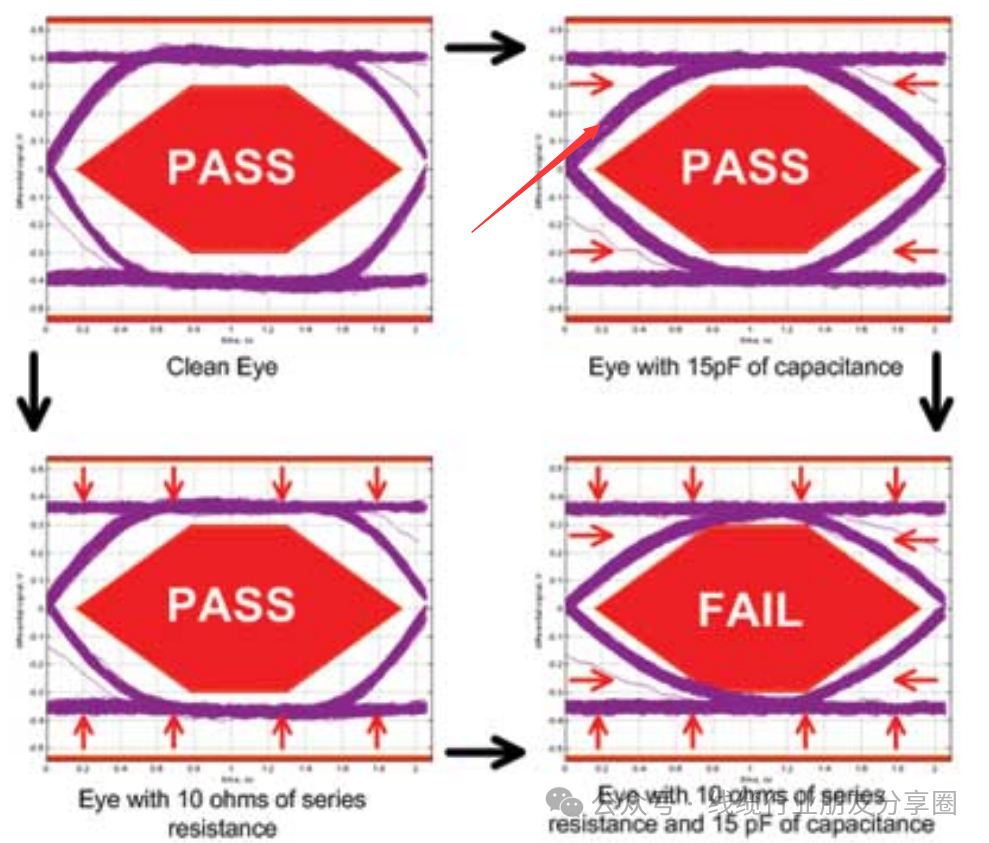

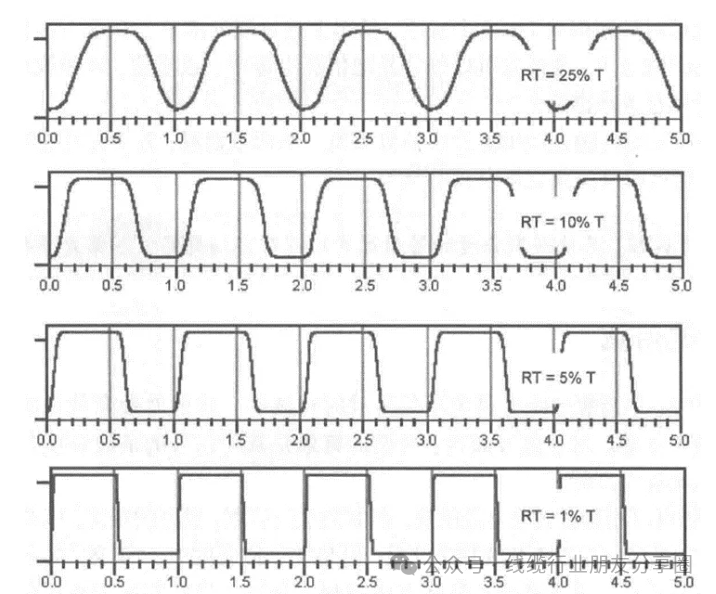

带宽取决于信号的边沿时间,而非信号频率(同样,定义传输线也是按照信号边沿时间和传输延时的比例关系,而非信号频率与传输延时的关系)。因此我们要树立起一个观念,在高速信号领域,信号边沿时间的重要性是要高于信号频率。只是在很多情况下,信号频率与信号边沿时间是息息相关的,即:信号频率越高则信号边沿时间越小。目前看第四个图形测试图形属于眼图边延平滑有触点导致不良.眼图常用知识介绍

互连带宽是对互连所能传输信号的最短边沿的度量,举个例子:假设互连带宽为1GHz,那么它所能传输的最快边沿RT=0.35/1GHz=350ps(本征边沿时间);如果边沿时间为350ps的信号进入互连,那么由如下公式输出边沿时间:

RT²out = RT²in + RT²interconnect

RTout =√(350ps²+350ps²) = 495ps。如果要使得互连对信号边沿时间的影响不超过10%,那么互连的本征上升沿要小于该信号上升沿的50%,也就是说:互连的带宽要大于信号带宽的2倍;为传输1GHz带宽的信号,互连带宽至少需要2GHz。

RTout =√(350ps²+175ps²) = 391ps。

此时互连带宽对信号边沿的影响是:391ps-350ps=41ps。大约为10%。

如上图所示,从原则上讲边沿时间和时钟的唯一约束是:边沿时间一定小于周期的50%。

-

光缆衰减多少算正常2025-08-04 21157

-

NR小基站使用AD9363,在TXATT从80设置到81,输出的信号会突然有10db衰减,为什么?2025-04-15 2906

-

用于无线电的衰减器选择指南2024-12-10 2011

-

高频信号衰减器的工作原理 如何测量衰减器的衰减值2024-12-09 4322

-

SN65DSI86输出信号支持多大的衰减值呢?2024-11-29 705

-

汽车数据线缆的衰减问题及测试方案2023-12-28 2045

-

RFTOP为用户定制大衰减值同轴固定衰减器2023-12-01 1830

-

信号衰减的原因和主要影响2023-07-10 14753

-

射频衰减器受频率影响大吗 射频衰减器原理 射频衰减器的类型及作用2023-05-03 3191

-

高速pcb电路设计中降低信号衰减方法2021-01-28 4416

-

光纤衰减器2017-11-09 3788

-

如何做到衰减网络对信号的衰减与信号的频率无关啊?2014-07-21 3083

-

多高的频率才算高速信号?2009-04-15 7612

全部0条评论

快来发表一下你的评论吧 !