8421码检测电路的设计方案

应用电子电路

956人已加入

描述

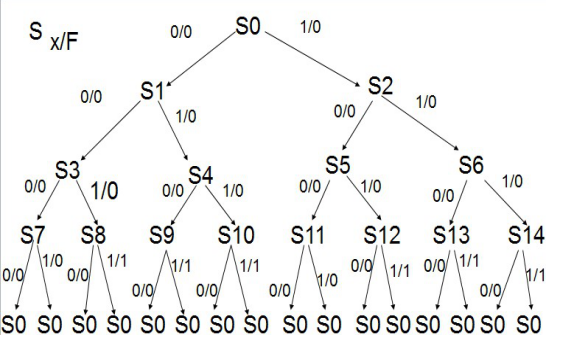

1、求原始状态转换图

设电路输入为X,电路输出为F,当输入为非法码时输出为1,否则输出为0。假设起始状态S0,从该状态开始根据输入是0还是1,将分别转换到两个不同的状态S1和S2,从S1和S2接收第二个码元,又根据是0还是1又各自转换到两个不同的新状态。然后再接收第三、第四码元。在接收第四个码元后,根据所接收的代码是否是非法码而确定其输出是否是1,并回到初始状态S0,准备接受新的一组码组。于是可以得到下面的原始状态转换图:

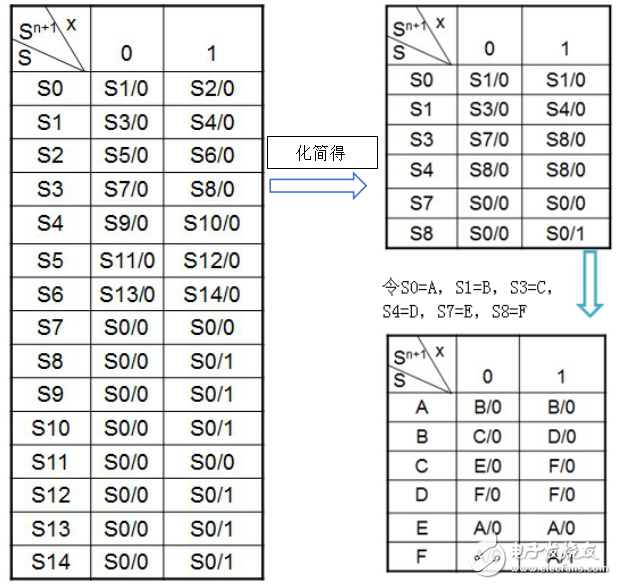

2、状态化简

如果两个状态,在相同的X输入下,其下一个状态与输出F均相同,那么就可以将这样的两个状态合并。通过这样的方法就可以实现状态的化简。

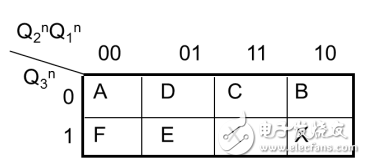

3、分配方案

即A=000、B=010、C=011、D=001、E=101、F=100

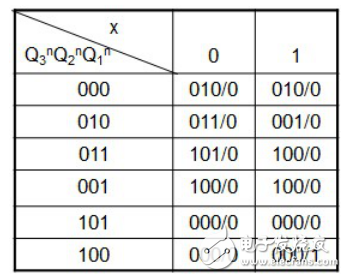

4、由状态转换表可得次态图

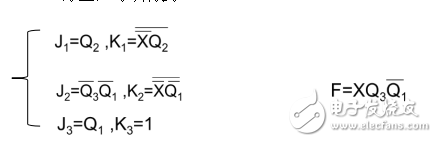

5、由次态图求各触发器的状态方程和驱动方程

综上,可以得到:

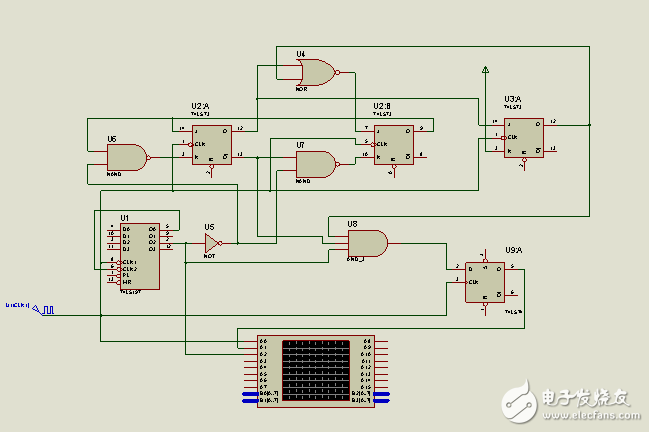

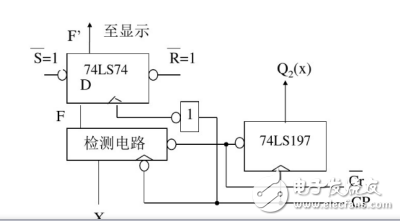

最终,使用proteus获得其逻辑图如下:

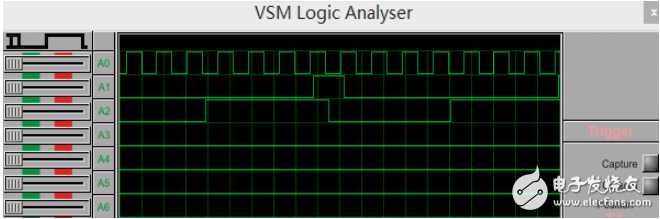

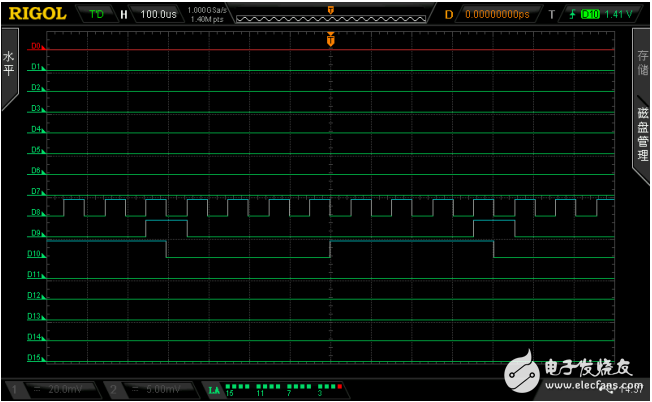

模拟之后的波形如下(自上到下依次为CP、F’、Qc):

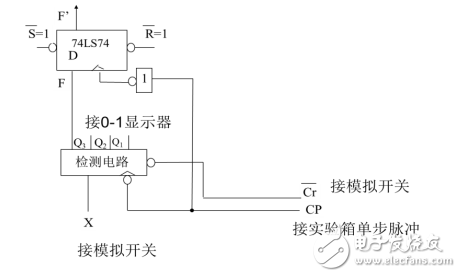

实验步骤

1、静态测试:

测试时注意:

(1)每次测试试都应该从初始状态开始即从A状态开始。

(2)码组的输入从低位开始如检测1011则输入顺序为1101。

(3)每输入一个码元即将X所连接的模拟开关放置相应的状态。再输入一个脉冲。故检测一组码元要四个脉冲。

(4)观察检测电路输出状态是否是按状态转换表变化。

在实际实验中,通过连接电路,逐一验证了该设计电路的正确性。

2、动态检测:

将74LS197的Qc与X相连接,时钟脉冲由CPA输入,QA连接CPB,由QA,QB,QC,和QD输出十六进制计数器。观察CP、F’和QC波形。

实验获得的波形如下图所示(D8,D9,D10分别为CP、F’、Qc):

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于电流传输器的检测电路设计方案2021-06-15 1214

-

外加电压检测复位电路设计方案2018-07-01 8154

-

8421码转换十进制程序2018-03-02 34965

-

精密光电检测电路设计方案2016-12-15 1074

-

读取8421拨码开关的值~~~2013-04-05 11895

-

可控硅过零检测调速控制电路设计方案2012-08-20 6768

-

什么是BCD码、8421码、余三码、格雷码2011-11-03 27780

-

错误检测与纠正电路的设计方案2010-03-05 1588

-

8421码同步十进制递增计数器2009-09-24 6876

-

二~十进制8421码一二~十进制2421码变换电路2009-04-10 5203

-

一种简单实用的测角码盘设计方案2006-03-24 1695

全部0条评论

快来发表一下你的评论吧 !