“一站式” PCB 设计 第一期:课程总览及 Allegro X Design Platform 24.1 新功能

描述

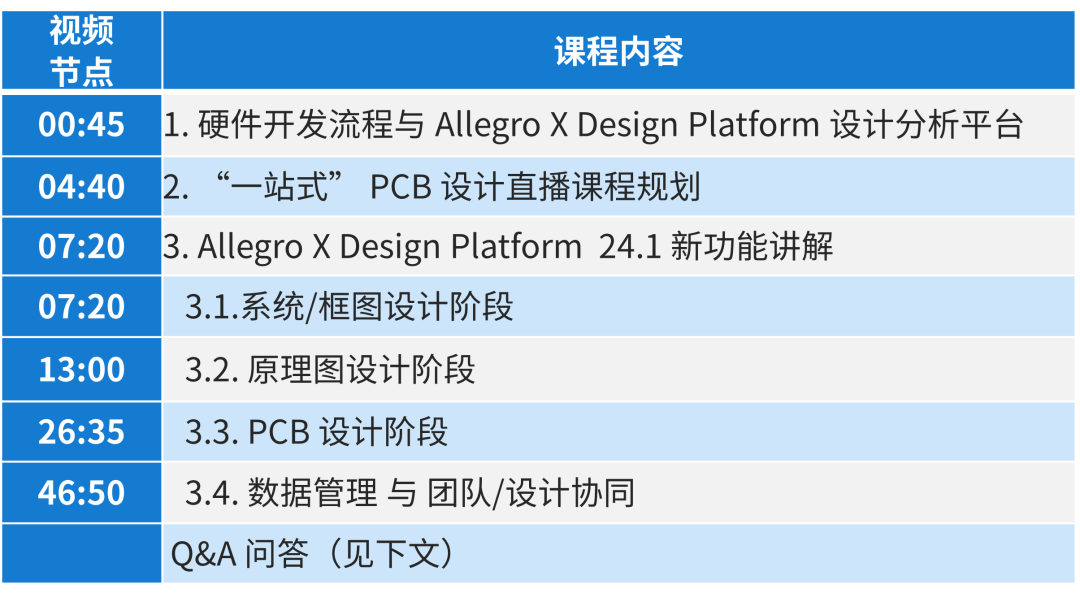

回放视频包含完整课程和demo演示;视频节点和课程内容如下表所示。

现场问答已精简、整理为文字版并收录在课件PPT中,方便大家快速查阅。

直播问答整理如下,供大家参考。

现场来不及提问、或错过直播的观众可以在后台留言提问,我们会转给相关技术人员进行解答。

也欢迎大家就培训本身的改进意见给我们留言,我们会根据大家的反馈调整今后的培训计划。

Q1

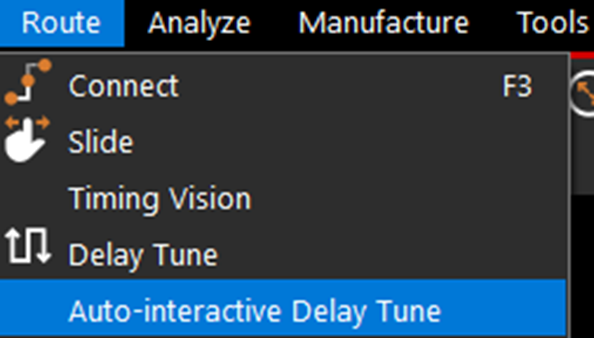

Allegro X PCB Designer 有自动绕等长功能吗?

答:Allegro X PCB Designer 支持自动绕等长。指令 Route -> Auto-interactive Delay Tune,如图所示:

Q2

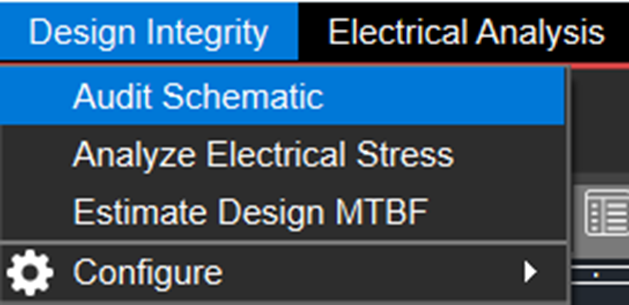

原理图互联怎么检查准确性?

答:Allegro X System Capture 的 Audit Schematic 功能可以检查原理图的连接。如图所示:

Q3

原理图窗口能直接打开 PCB 文件吗?

答:Allegro X System Capture 支持在原理图设计窗口中打开 PCB 文件。

Q4

网表是否还需要导入导出?

答:使用 Allegro X Design Platform,原理图完成设计后,可直接输出到 PCB 设计环境,用户在 PCB 环境中可直接开始设计。当然,也可以选择传统的方法:从原理图中导出网表,再新建 PCB,导入网表,启动设计。

Q5

精细化差分信号设计,有哪些措施,精细化到什么程度?

答:精细化设计差分信号常见的措施包括 P/N 信号等长,阻抗连续、不跨分割、相邻层挖空等等。具体的规则数值、精细化程度跟信号速率、板材选择、层叠方案等有关,需根据仿真结果来确定。

Q6

高频差分线控制等长,走哪种线更好,45度还是弧线?如何确定 P 和 N 之间的长度差?

答:如果高频信号的频率不是特别高,实际布线空间紧张,使用45度线来做等长可以满足要求。如果处理超高频信号,且实际布线空间不紧张时,弧线等长更有利于信号完整性;P/N 之间的长度误差值需根据实际情况来仿真确定,常见控制误差范围为 5mil-10mil。

Q7

Analysis Model Manager(AMM)支持模型赋予吗?

答:AMM 支持模型赋予,也可以导入外部模型库,还能创建模型。

Q8

有 3D 堆叠的 PCB 设计吗?

答:有,对产品小型化要求极高的项目可能会用这样的技术,将多层电路板在垂直方向上堆叠起来进行设计。

Q9

EMC 仿真方面,PCB 设计上如何考虑?

答:从布局方面来看,不同功能的电路需分区设计,比如数字电路、模拟电路、电源等;从布线方面来看,用专门的 GND 层来确保接地良好、差分信号等长、避免锐角转向等;从整板来看, 使用相应的屏蔽方案亦有助于 EMC。

10

多人共同设计一个 PCB,只连局域网内服务器就可以吗?

答:是的,只连局域网内服务器就可以。

11

TCL 语言,脚本语言 SIKLL 是否有淡出的趋势?

答:TCL 和 SKILL 没有淡出趋势。TCL 在 EDA 领域依旧被广泛使用(编写自动化测试脚本、实现工具之间的交互等)。SKILL 主要用于全流程的定制化功能,比如:设计数据的提取和检查。

12

有系统的操作教程吗?

答:Allegro X 有系统的帮助文档,对每个指令都有详细的解释。另外,我们在 B站 也分享了很多操作视频,欢迎点击这里观看。

13

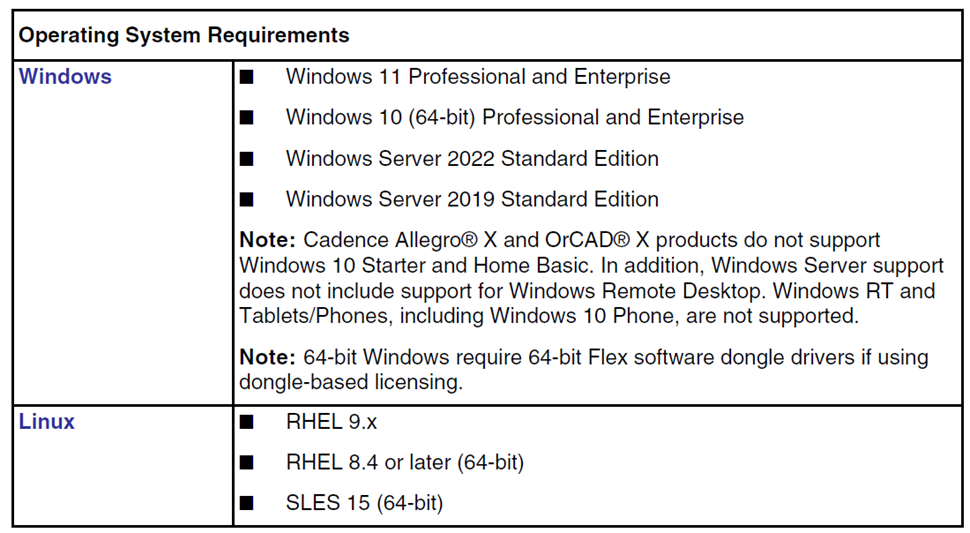

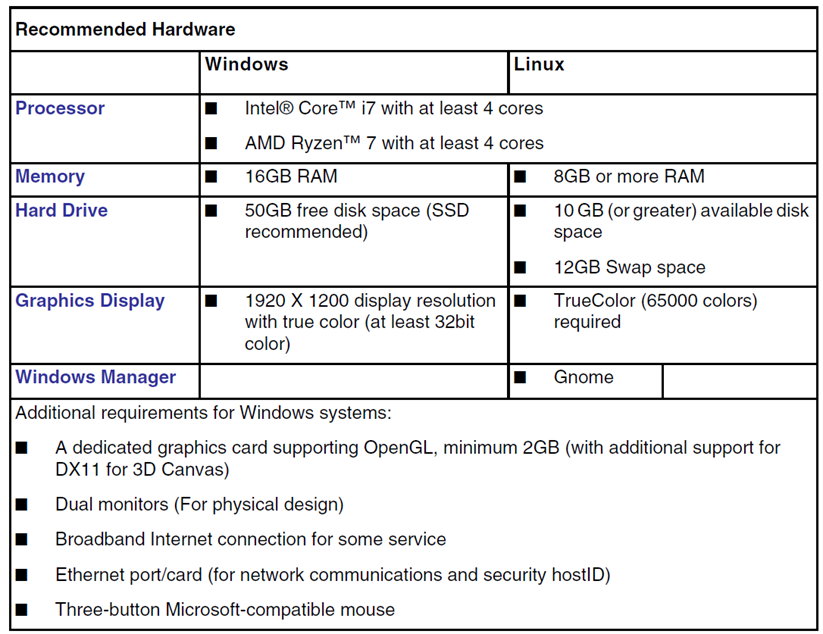

24.1 版本对电脑配置有什么要求吗?

答:24.1 版本的通用产品配置请见下图。

Allegro X Pulse、Allegro X Advanced Package Designer 和 3D Design Viewer 的配置需要结合用户需求,具体请询问 Cadence 销售团队或授权经销商。

-

网课回放 I “一站式” PCB 设计 · 25.1 第二期:高效高质量原理图设计2025-12-05 583

-

一站式PCBA加工全流程大揭秘!从设计到交付一站式搞定2025-06-11 1366

-

网课回放 I 升级版“一站式” PCB 设计第四期:规则设置2025-06-06 910

-

网课回放 I 升级版“一站式” PCB 设计第三期:原理图完整性及可靠性分析2025-05-10 775

-

2024年度网课 I “一站式” PCB 设计——基于 Allegro X Design Platform 24.1 最新版本2024-10-12 2615

-

为什么选择一站式PCBA加工?PCBA一站式服务的优势2024-01-03 1670

-

网课回放 I RK3588 实例课程第一期:项目总结和技术答疑2023-07-31 2172

-

RT-Thread 每日一练打卡学习第一期完结,第二期敬请期待2021-06-10 8609

-

请问你们第一期视频都是怎么学的?2019-09-24 2700

-

请问第一期视频需要掌握什么程度?2019-07-23 1801

-

动手玩转Arduino(第一期)2016-07-08 509

-

有没有PCB设计、PCB制版、PCB贴片提供一站式的专制化服务方案?2016-04-25 3761

-

Linux C编程一站式学习2012-08-09 7557

-

电子报2011年第一期2011-03-14 4605

全部0条评论

快来发表一下你的评论吧 !