双阱工艺的制造过程

描述

与亚微米工艺类似,双阱工艺是指形成NW和PW的工艺,NMOS 是制造在PW里的,PMOS是制造在NW里的。它的目的是形成PN 结隔离,使器件之间形成电性隔离,优化晶体管的电学特性。

1)清洗。利用酸槽清洗晶圆,得到清洁的表面。

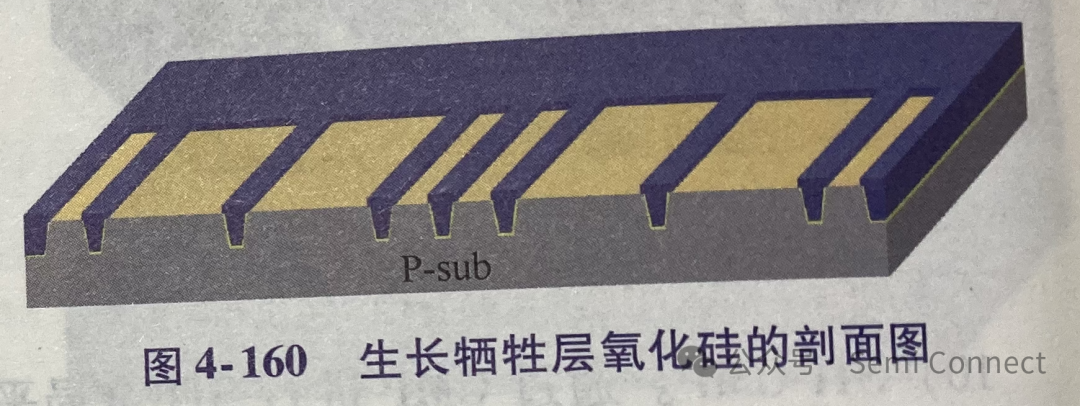

2) 生长牺牲层氧化硅。利用炉管热氧化生长一层二氧化硅薄膜,它是干氧氧化法。利用高纯度的氧气在900°C左右的温度下使硅氧化,形成厚度约200~300A的二氧化硅。牺牲层氧化硅可以防止离子注入隧道效应,隔离光刻胶与硅衬底,防止光刻胶接触污染硅衬底,也可以捕获硅表面的缺陷。同时为了消除Si3N4对有源区表面的影响,改善表面状态,生长牺牲层氧化硅是必需的。如图4-160所示,是生长牺牲层氧化物的剖面图。

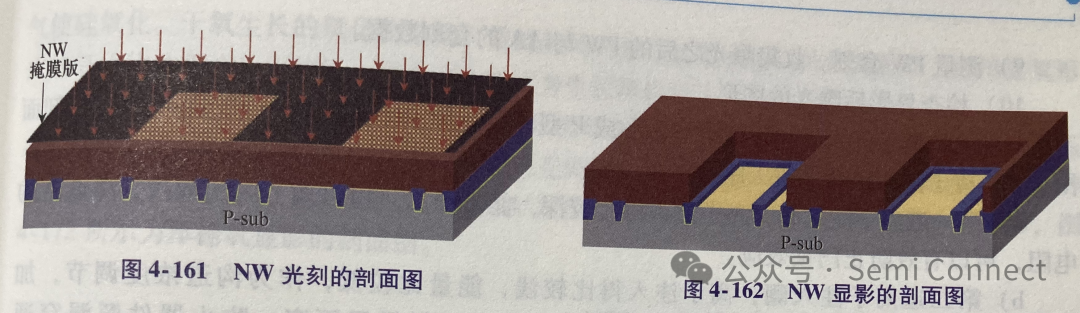

3)NW光刻处理。通过微影技术将 NW 掩膜版上的图形转移到晶圆上,形成NW的光刻胶图案,非NW 区域保留光刻胶。AA作为NW光刻曝光对准。如图4-5所示,是电路的版图,工艺的剖面图是沿AA’方向。图4-161 所示为 NW光刻的剖面图。图4-162 所示为NW显影的剖面图。

4)测量NW套刻,收集曝光之后的NW与 AA的套刻数据。

5)检查显影后曝光的图形。

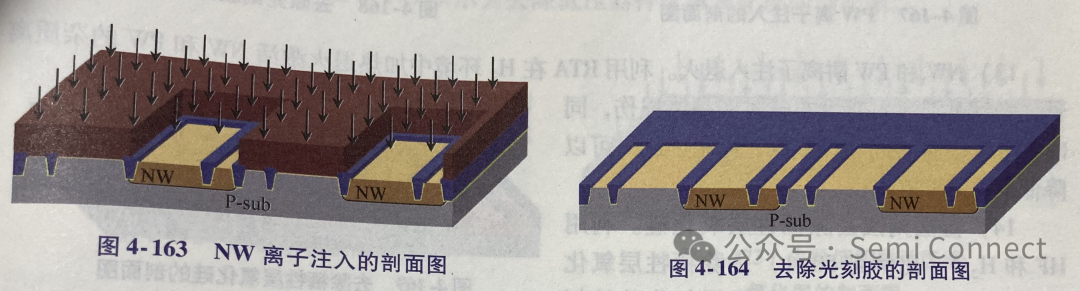

6)NW离子注入。利用离子注入形成n型的阱。图4-163所示NW离子注入的剖面图。NW 离子注入包括三道工序:

a)第一道离子注入磷,离子注入得比较深,能量很高,用以调节阱的浓度,降低阱的电阻,可以有效防止闩锁效应。

b)第二道离子注入磷,离子注入得比较浅,能量比较低,作为沟道浓度调节,加大LDD 以下局部阱的浓度,使器件工作时该位置的耗尽层更窄,防止器件源漏穿通漏电。

c)第三道离子注入砷,离子注入表面,能量很低,调节PMOS阈值电压Vt。

7)去光刻胶。利用干法刻蚀和湿法刻蚀去除光刻胶。图4-164 所示为去除光刻胶的剖面图。

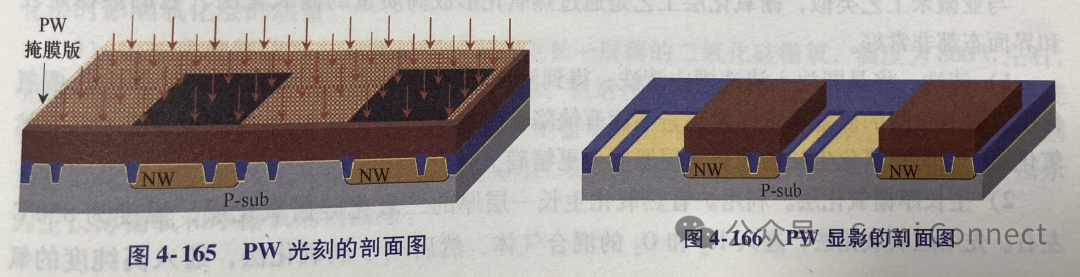

8)PW光刻处理。与NW光刻处理类似,通过微影技术将PW掩膜版上的图形转移到晶圆上,形成PW的光刻胶图案,非PW区域保留光刻胶。AA作为PW光刻曝光对准。图4-5所示为电路的版图,工艺的剖面图是沿 AA'方向,图4-165所示为PW光刻的剖面图,图4-166所示力PW 显影的剖面图。

9)测量PW套刻。收集曝光之后的PW与 AA的套刻数据。

10)检查显影后曝光的图形。

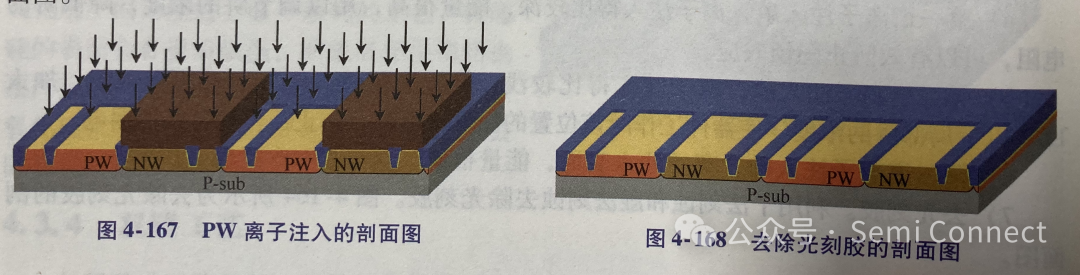

11)PW离子注入。利用离子注入形成P型的阱。图4-167所示为PW 离子注入的剖面图。PW 离子注入包括三道工序:

a)第一道离子注入硼,离子注入得比较深,能量很高,用以调节阱的浓度,降低阱的电阻,可以有效防止闩锁效应。

b)第二道离子注入硼,离子注入得比较浅,能量比较低,作为沟道浓度调节,加大LDD以下局部阱的浓度,使器件工作时该位置的耗尽层更窄,防止器件源漏穿通漏电。

c)第三道离子注入BF2,离子注入表面,能量很低,调节 NMOS 阈值电压Vt。

12) 去光刻胶。利用干法刻蚀和湿法刻蚀去除光刻胶。图4-168所示去除光刻胶的剖面图。

13)NW和PW阱离子注入退火。利用 RTA 在H2环境中加热退火激活 NW和PW的杂质离子,修复离子注入造成的硅衬底晶格损伤,同时会造成杂质的进一步扩散,快速热退火可以降低杂质的扩散。

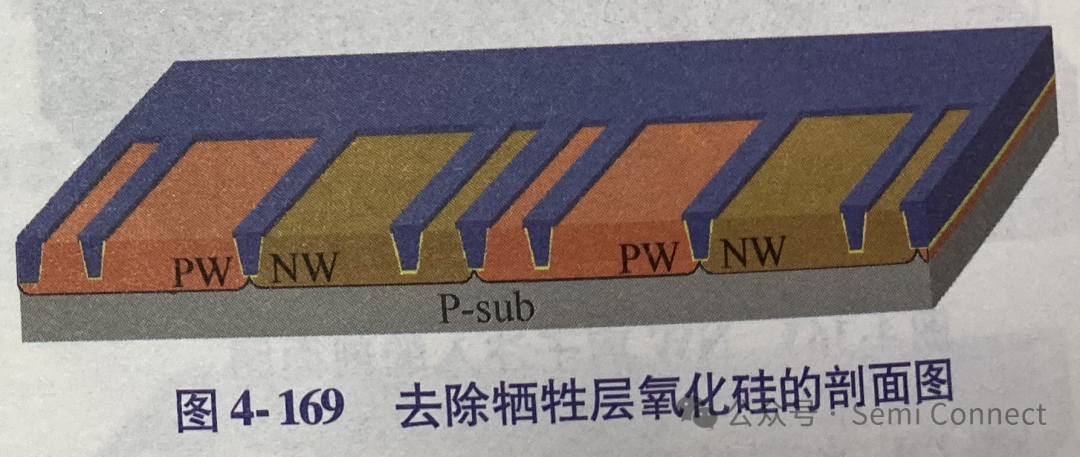

14)湿法刻蚀去除牺牲层氧化硅。利用HIF 和H2O(比例是50:1)去除牺牲层氧化硅。图4-169所示为去除牺牲层氧化硅的剖面图。

-

半导体芯片制造中倒掺杂阱工艺的特点与优势2025-01-03 2509

-

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺2024-12-30 3359

-

【「大话芯片制造」阅读体验】+芯片制造过程工艺面面观2024-12-16 1120

-

Bosch刻蚀工艺的制造过程2024-10-31 4815

-

半导体制造工艺 - 晶圆制造的过程2024-03-29 6175

-

堆叠式DRAM单元STI和阱区形成工艺介绍2023-09-04 7008

-

模块工艺——双阱工艺(Twin-well or Dual-Well)2022-11-14 17920

-

《炬丰科技-半导体工艺》IC制造工艺2021-07-08 4739

-

如何使用深阱工艺提高LDMOS的抗击穿能力2020-09-25 1628

-

单片机晶圆制造工艺及设备详解2018-10-15 7156

-

浅谈晶圆制造工艺过程2018-04-16 15361

-

机械加工厂制造工艺过程中热处理工序位置2018-04-02 1988

-

13um应变补偿多量子阱SLD台面制作工艺的研究2009-10-06 3844

全部0条评论

快来发表一下你的评论吧 !