PCI-E TLP学习笔记(2)

描述

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

今天给大侠带来PCI-Express transaction Layer specification(处理层协议),本次PCIE TLP 学习经验分享分为三篇,今天带来第二篇,i/o,memory,configuration,message request、completetion(Memory Request Package、I/O Request 包、Configuration Request包、Message、Completion Rules(应答机制)),话不多说,上货。

三、I/O,Memory,Configuration,Message Request、Completetion

memory、i/o、configuration request包头除了基本的域之外还包括:Transaction ID即requester ID、Tag、Last DW BE、1st DW BE,放在第二个DW中。以下分别介绍这三种不同的请求包。

1. Memory Request Package

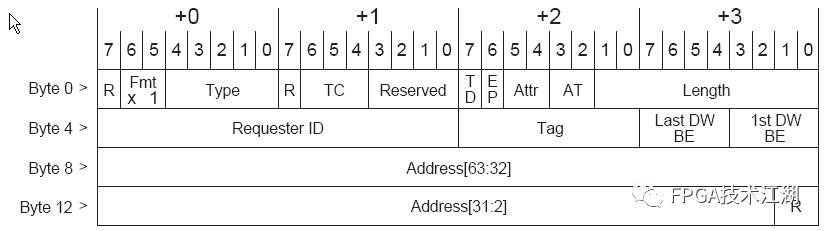

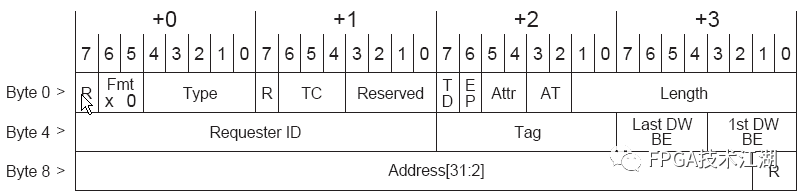

采用直接地址寻址,有64bit地址和32bit地址两种,其中读请求包的Length域不应大于Max_Read_Request_Size寄存器设置的值。请求器件不会示例一个所访问的memory空间超过4KB的read request包。以下是两种不同地址长度的memory request 包。

64位地址的包格式

32位地址的包格式

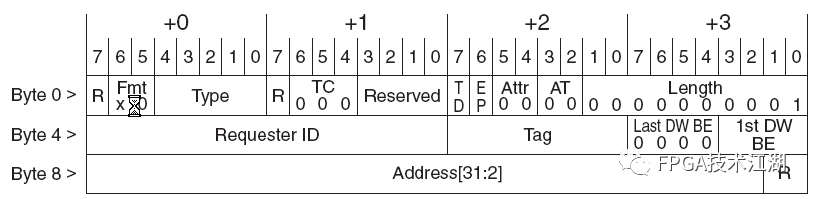

2. I/O Request 包

I/O request 包只有32位地址寻址。有如下限制:

TC[2:0] must be 000b

Attr[1:0] must be 00b

AT[1:0] must be 00b

Length[9:0] must be 00 0000 0001b

Last DW BE[3:0] must be 0000b

格式如下:

可见每次只传送一个DW数据。

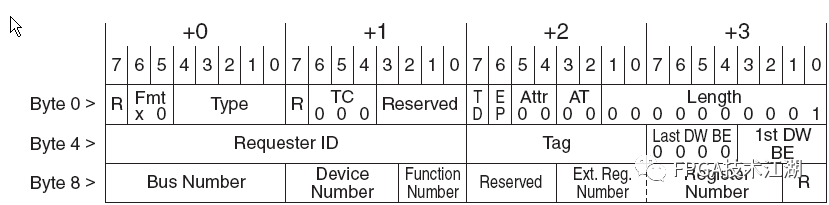

3. Configuration Request包

configuration request包采用ID寻址方式,包头(Tlp Header长度是3DW)。有如下规定:

TC[2:0] must be 000b

Attr[1:0] must be 00b

AT[1:0] must be 00b

[9:0] must be 00 0000 0001b

Last DW BE[3:0] must be 0000b

包格式:

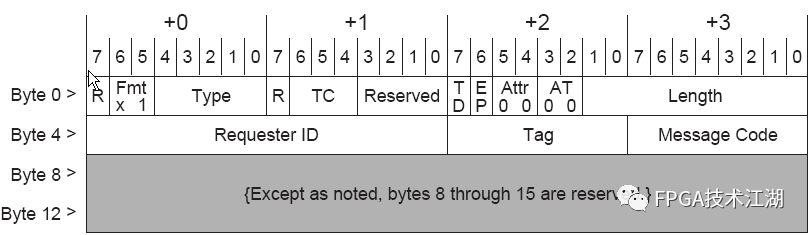

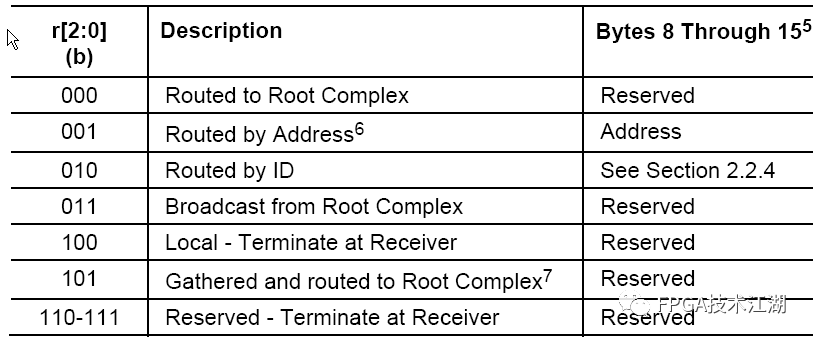

4. Message 包

Message包分为:

INTx Interrupt Signaling INTx中断信息包

Power Management 电源管理机能。

Error Signaling错误信息包

Locked Transaction Support 锁住交易的支持

Slot Power Limit Support插槽电源限制的支持

Vendor-Defined Messages制造商自行定义信息

所有的Message包都用Msg编码,即不包括数据负荷的Message包,除了Vendor_Defined Messages和Set_Slot_Power_Limit Message包,Message包有以下限制:

The Message Code field must be fully decoded (Message aliasing is not permitted).

Except as noted, the Attr[1:0] field is reserved.保留Attr域。

AT[1:0] must be 00b.

Except as noted, bytes 8 through 15 are reserved.保留包头部分的bytes8到byte15.

Message Requests are posted and do not require Completion。Message包不需要返回响应包。

Message Requests follow the same ordering rules as Memory Write Requests。

寻址方式:隐含寻址,由Type域中的r[2:0]决定,即Type域的最后三位。具体寻址映射如下:

r[2:0]是010时,寻址方式就是ID寻址。

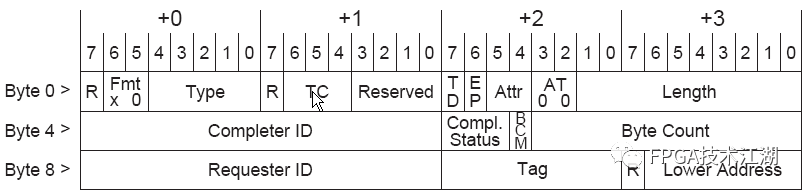

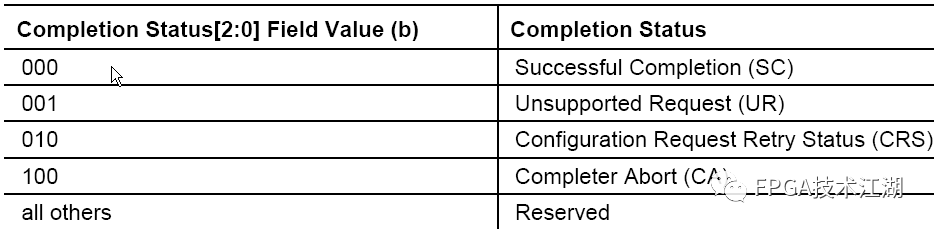

5. Completion Rules(应答机制)

completion包用ID寻址方式,寻址使用的ID就是request提供的requester ID。除了那些正常的域以外,还包括:

Completer ID[15:0] – Identifies the Completer – described in detail below

Completion Status[2:0] – Indicates the status for a Completion

BCM – Byte Count Modified

Byte Count[11:0] – The remaining byte count for Request

Tag[7:0] – in combination with the Requester ID field, corresponds to the Transaction ID

Lower Address[6:0] – lower byte address for starting byte of Completion

compl.Status位有如下含义:

第二篇就到这里,明天开启第三篇,将会带来请求和应答处理机制(Request Handling Rules、Completion Handling)、virtual channel(vc)Mechanism虚拟通道机制(TC/VC映射、Flow Control)、Data Integrity数据完整性等详解,愿大侠持续关注,一切安好,告辞。

-

PCI-E TLP学习笔记(1)2024-11-06 4347

-

pci-e插槽的规格有哪些 各个版本的pci-e的规范区别2023-08-05 17062

-

什么是PCI PCI-X PCI-E?2021-10-25 1858

-

PCI PCI-X PCI-E介绍 精选资料分享2021-07-29 1912

-

连欣PCI模块连接器PCI-E 52PIN原理图2021-07-08 2216

-

M.2和PCI-E接口固态硬盘的区别是什么2020-07-28 13866

-

浅谈显卡PCI/AGP/PCI-E接口的区别2017-11-03 10777

-

解决台式机PCI-E 1X不够难题 :乐扩PCI-E 1X转2口PCI-E 1X扩展卡2017-10-19 7216

-

pci-e布线规范2016-07-14 5041

-

在FPGA上设计PCI-e Gen2.0和PCI-e Gen3.0有什么不同2016-03-03 9825

-

PCI-e总线FPGA开发板资料说明2011-04-14 2140

-

PCI-E 的PADS封转2011-03-30 2822

-

南桥PCI-E通道数2009-12-26 753

-

PCI-E接口定义 引脚定义图 PCI-E针脚定义图2008-04-27 85784

全部0条评论

快来发表一下你的评论吧 !