PCI-E TLP学习笔记(3)

描述

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

今天给大侠带来PCI-Express transaction Layer specification(处理层协议),本次PCIE TLP 学习经验分享分为三篇,今天带来第三篇,也就是最后一篇,请求和应答处理机制(Request Handling Rules、Completion Handling)、virtual channel(vc)Mechanism虚拟通道机制(TC/VC映射、Flow Control)、Data Integrity数据完整性等内容,话不多说,上货。

四、 请求和应答处理机制

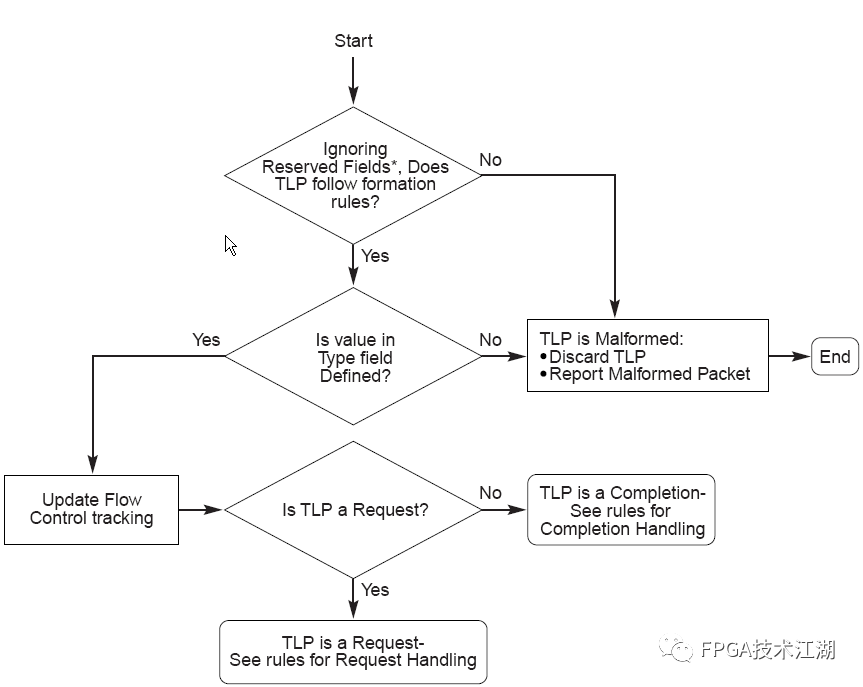

处理机制就是对接收到的经Data Link Layer进行数据完整性验证的Tlp进行处理。无效的包将被抛弃,保留字(reserved)将被忽略。以下是处理流程:

对所有的包分request handling和completion handling,按不同的规范处理。

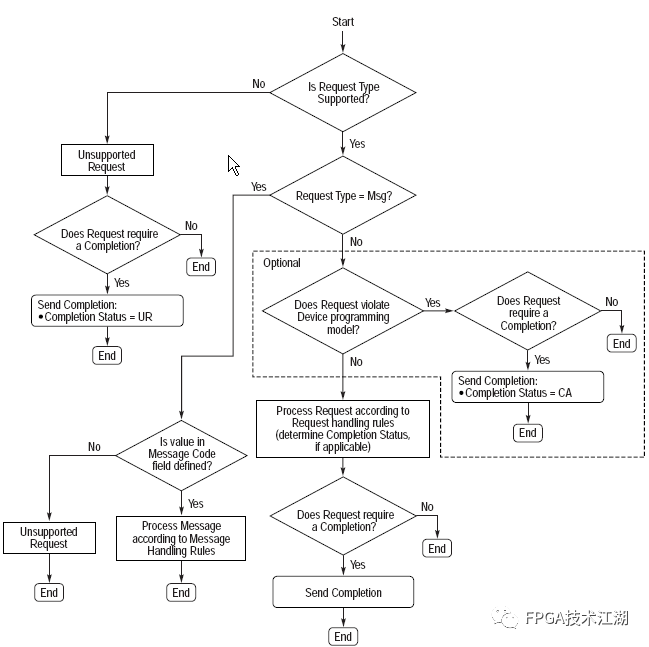

1. Request Handling Rules

如果请求是一个不支持的请求包,并且需要响应,则Completion Status=UR,即不支持的请求。如果请求包是一个Message 包则按Message包处理规则处理,否则对这个request进行处理。如果请求违反器件编程定义则给出ca响应,即响应器件放弃该请求,否则做出正确应答。

2. Completion Handling

如果接收到一个completion包的Transaction ID和requester的Transaction ID不一致则这个应答包是非预期包。合法的应答包将按Compl.Status域处理并提取有效数据负荷。

五、virtual channel(vc)Mechanism虚拟通道机制

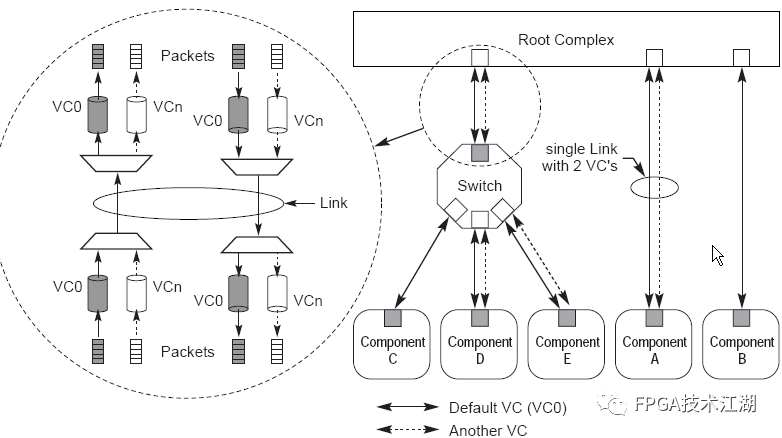

虚拟信道(virtual channel)在总线中提供用TC域来区分的虚拟信息通路,即某一传输通路,有不同的流程控制机制(Flow Control)。当某流程控制出现拥塞时,其他通路依然畅通。VC有自己的独立流控制,是实现Qos的秘诀。VC通道是解决拥塞的基础。

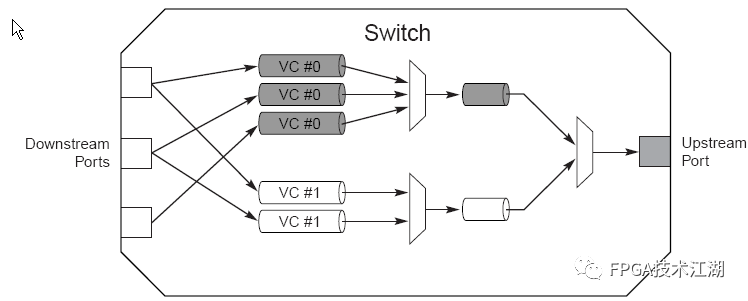

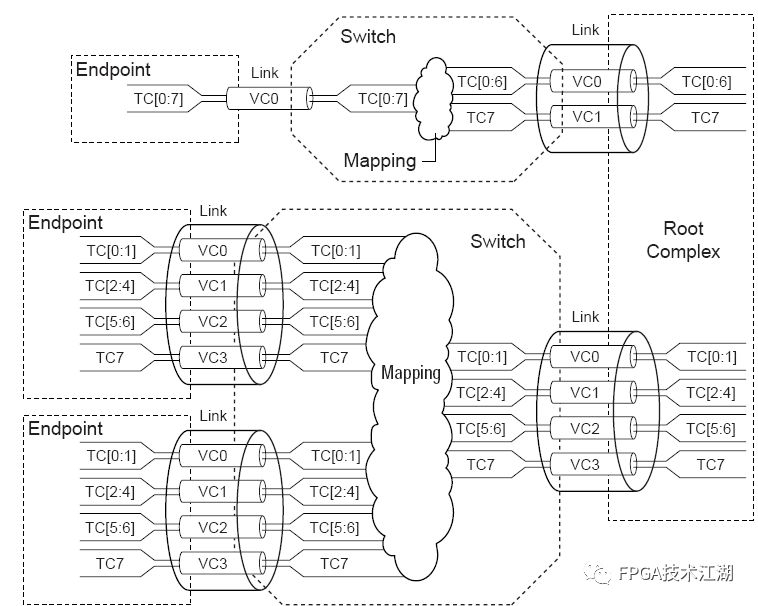

在Switch内部,VC通道机制如下:

1. TC/VC映射

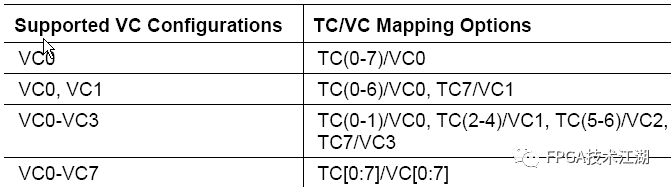

每个TLP包并不包含具体的VC信息,VC是由TC映射得到的。每个器件的TC/VC映射是不同的,TC0/VC0是固定的。具体TC、VC映射如下:

一个或多个TC映射到一个VC,同一个TC不能映射到不同的VC上,连接双方的映射机制一致。除了TC0外,其他的可以软件设置。链路两端的映射方案要一致,如图是一种映射方案。

具体的虚拟通道是由VC ID决定和识别的。

2. Flow Control

每个虚拟通道有独立的流程控制的缓冲空间。在收发双方,流程控制信息是用数据链路包(DLLP)打包发送的,其中的“VC ID“就是用来载送虚拟通道的识别。总的来说,流程控制是由数据交易层(Transaction Layer)搭配了数据链路层(Data Link Layer)来处理的,只是,处理层通常是针对接收到的TLP打包,生成TC,再由TC映射到VC。流程控制信息是FCP(Flow Control Package),即DLLP打包的一种。流程控制的信用单位是Credit,也就是接收器的缓冲空间是4DW。信用单位:就是接收端缓冲空间大小的基本单位。

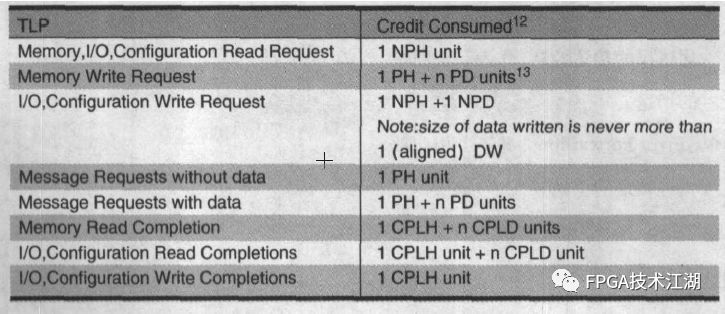

流程控制能分辨三种包:posted requests(p)、non-posted requests(Np)、completions(cpl)。还可以分辨三种包的包头Header和数据Data,可以这样说,每个虚拟通道(VC)对应的特定流程控制包含6种不同的流程控制信息:

1、PH=posted Request Header;

2、PD=posted request Data Payload;

3、NPH=non-posted request Header;

4、NPD=non-posted request Data Payload;

5、CPLH=completion Header;

6、CPLD=completion Data Payload。

各种包对应的流程控制如下表:

六、Data Integrity数据完整性

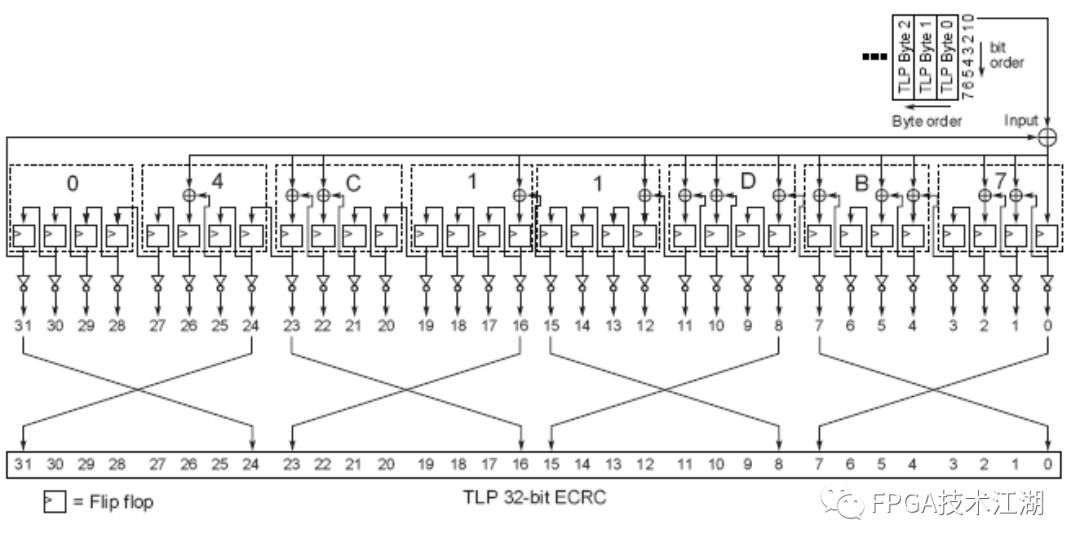

主要的数据完整性保证之一是Data Link Layer中的crc(lcrc)。为了确保数据端对端的可靠性在Transaction层的TLp Digest域还选择性的做一ECRC校验,ECRC的初值是FFFF FFFF,算法实现如下:

Transaction Layer specifications只是pcie总线规范的一层规范,主要处理数据包的传送管理,此外还有Data Link Layer规范和physical Layer规范。

此次分享到此结束,后面有时间还会给各位大侠分享关于PCIE的相关其他内容,愿大侠持续关注,一切安好,告辞。

-

PCI-E TLP学习笔记(1)2024-11-06 4223

-

pci-e插槽的规格有哪些 各个版本的pci-e的规范区别2023-08-05 16897

-

什么是PCI PCI-X PCI-E?2021-10-25 1833

-

PCI PCI-X PCI-E介绍 精选资料分享2021-07-29 1873

-

连欣PCI模块连接器PCI-E 52PIN原理图2021-07-08 2170

-

Intel的核显真的占用了CPU的4根PCI-E通道吗2019-11-23 6719

-

浅谈显卡PCI/AGP/PCI-E接口的区别2017-11-03 10624

-

解决台式机PCI-E 1X不够难题 :乐扩PCI-E 1X转2口PCI-E 1X扩展卡2017-10-19 7188

-

pci-e布线规范2016-07-14 4973

-

在FPGA上设计PCI-e Gen2.0和PCI-e Gen3.0有什么不同2016-03-03 9816

-

PCI-e总线FPGA开发板资料说明2011-04-14 2126

-

PCI-E 的PADS封转2011-03-30 2803

-

南桥PCI-E通道数2009-12-26 744

-

PCI-E接口定义 引脚定义图 PCI-E针脚定义图2008-04-27 85436

全部0条评论

快来发表一下你的评论吧 !