Air780EP硬件设计原理解析(第二部分)

电子说

描述

接下来,我们继续学习第二部分。

3.3 电源供电

3.3.1 模块电源工作特性

在模块应用设计中,电源设计是很重要的一部分。由于LTE射频工作时最大峰值电流高达1.5A,在最大发射功率时会有约700mA的持续工作电流,电源必须能够提供足够的电流,不然有可能会引起供电电压的跌落甚至模块直接掉电重启。

3.3.2 减小电压跌落

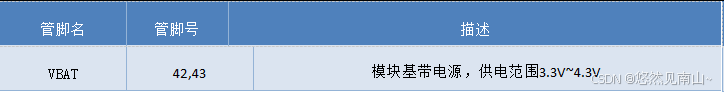

模块电源VBAT电压输入范围为3.3V~4.3V,但是模块在射频发射时通常会在VBAT电源上产生电源电压跌落现象,这是由于电源或者走线路径上的阻抗导致,一般难以避免。因此在设计上要特别注意模块的电源设计,在VBAT输入端,建议并联一个低ESR(ESR=0.7Ω)的100uF的钽电容,以及100nF、33pF、10pF滤波电容,VBAT输入端参考电路如图4所示。并且建议VBAT的PCB走线尽量短且足够宽,减小VBAT走线的等效阻抗,确保在最大发射功率时大电流下不会产生太大的电压跌落。建议VBAT走线宽度不少于1mm,并且走线越长,线宽越宽。

3.3.3 供电参考电路

电源设计对模块的供电至关重要,必须选择能够提供至少1A电流能力的电源。若输入电压跟模块的供电电压的压差小于2V,建议选择LDO作为供电电源。若输入输出之间存在的压差大于2V,则推荐使用开关电源转换器以提高电源转换效率。

LDO供电:

下图是5V供电的参考设计,采用了Micrel公司的LDO,型号为MIC29302WU。它的输出电压是4.16V,负载电流峰值到3A。为确保输出电源的稳定,建议在输出端预留一个稳压管,并且靠近模块VBAT管脚摆放。建议选择反向击穿电压为5.1V,耗散功率为1W以上的稳压管。

DC-DC 供电:

下图是 DC-DC 开关电源的参考设计,采用的是杰华特公司的 JW5033S 开关电源芯片,它的最大输出电流是 2A,输入电压范围 3.7V~18V。注意 C25 的选型要根据输入电压来选择合适的耐压值。

3.4 开关机

3.4.1 开机

*

在VBAT供电后,可以通过如下两种方式来触发Air780EP开机:

- 按键开机: PWKEY管脚通过轻触按键连接到地,按键按下1秒以上实现开机。

- 上电开机:将PWRKEY管脚直接短接到地,VBAT上电后就可以实现开机。

**PWRKEY **管脚开机

VBAT上电后,可以通过PWRKEY管脚启动模块,把PWRKEY管脚拉低1秒以上之后模块会进入开机流程,软件会检测VBAT管脚电压,若VBAT管脚电压大于软件设置的开机电压(3.3V),会继续开机动作直至系统开机

完成;否则,会停止执行开机动作,系统会关机,开机成功后PWRKEY管脚可以释放。可以通过检测VDD_EXT

管脚的电平来判别模块是否开机。推荐使用开集驱动电路来控制PWRKEY管脚。下图为参考电路:

另一种控制PWRKEY管脚的方法是直接使用一个按钮开关。按钮附近需放置一个TVS管用以ESD保护。下图为参考电路:

上电开机

将模块的PWRKEY 直接接地可以实现上电自动开机功能。需要注意,在上电开机模式下,将无法关机。

对于用电池供电的应用场景不建议用 PWRKEY 接地的上电自动开机方式。

3.4.2 关机

以下的方式可以关闭模块:

- 正常关机:使用PWRKEY管脚关机

- 正常关机:通过AT指令AT+CPOWD关机

**PWRKEY **管脚关机

PWRKEY 管脚拉低 1.5s 以上时间,模块会执行关机动作。

关机过程中,模块需要注销网络,注销时间与当前网络状态有关,经测定用时约2s~12s,因此建议延长

12s后再进行断电或重启,以确保在完全断电之前让软件保存好重要数据。时序图如下:

低电压自动关机

模块在运行状态时当 VBAT 管脚电压低于模块工作的最低工作电压时(默认设置 3.3V),软件会执行关机动作关闭模块,以防低电压状态下运行出现各种异常。

3.4.3 复位

RESET_N 引脚可用于使模块复位。 拉低RESET_N 引脚 100ms 以上可使模块复位。 RESET_N 信号对干扰比较敏感, 因此建议在模块接口板上的走线应尽量的短,且需包地处理。

参考电路:

注意:

- 复位功能建议仅在AT+CPOWD 和PWRKEY 关机失败后使用。

3.5 串口

模块提供了 4 个通用异步收发器:主串口 MAIN_UART、AUX_UART、DBG_UART、UART3。

3.5.1 MAIN_UART

表格 6:MAIN_UART 管脚定义

对于AT 开发方式,3.5.1. MAIN_UART 用来进行 AT 指令通讯。MAIN_UART 支持固定波特率, 不支持自适应波特率

在默认情况下,模块的硬件流控是关闭的。当客户需要硬件流控时,管脚 RTS,CTS 必须连接到客户端,AT命令 “AT+IFC=2,2” 可以用来打开硬件流控。AT 命令 “AT+IFC=0,0” 可以用来关闭流控。具体请参考《AirM2M 无线模块 AT 命令手册》。

MAIN_UART 在休眠状态下保持的功能,能够唤醒模块。

MAIN_UART 的特点如下:

- 包括数据线TXD和RXD,硬件流控控制线RTS和CTS。

- 8个数据位,无奇偶校验,一个停止位。

- 硬件流控默认关闭。

- 用以AT命令传送,数传等。

- 支持波特率如下:600,1200,2400,4800,14400,9600,19200,38400,57600,115200,230400,460800,921600bps

注意:

MAIN_UART 在开机过程中短时会输出固定调试信息

3.5.2 AUX_UART

表格 7:AUX_UART 管脚定义

AUX_UART为辅助串口,不支持AT指令交互,用于某些外设通信,如对接GNSS等。 AUX_UART休眠后会关闭,无法通过给AUX_UART发送数据进行唤醒。

3.5.3 DBG_UART

DBG_UART 用来软件调试时输出AP trace,建议预留测试点。 DBG_UART 在开机过程中短时会输出固定调试信息。

DBG_TX、DBG_RX 默认功能为系统底层日志口,进行模块硬件设计时,在剩余功能引脚充足的前提下,避免使用DBG_TX 和DBG_RX。

如果将此引脚复用为其他功能,则无法从 DBG_TX 和DBG_RX 抓取系统日志。

在某些场景下,如果模块出现异常,无法抓到问题日志,只能通过硬件改版,引出 DBG_TX、 DBG_RX,抓取日志再进行分析。

包括但不限于以下两种场景:

1、低功耗场景:

在低功耗场景下,USB 无法使用,只能通过 DBG_TX、DBG_RX 来抓取日志。

2、非低功耗场景:

模块接入USB 时,工作正常,未接入 USB 时,工作异常的情况,只能通过 DBG_TX、DBG_RX 来抓取日志。

3.5.4 UART3

不支持LCD 功能,可以再复用一组 UART3

3.5.5 串口连接方式

串口的连接方式较为灵活,如下是三种常用的连接方式。三线制的串口请参考如下的连接方式:

带流控的串口连接请参考如下电路连接,此连接方式可提高大数据量传输的可靠性,防止数据丢失。

3.5.6 串口电压转换

Air780EP 模块的串口电平为 1.8V 或 3.3V,通过 PIN100 IO_SEL 配置IO 口电平,能够满足大部分外设,主控的串口直接需求,但是如果要和 5V 或者以上的MCU 或其他串口外设通信,那就必须要加电平转换 电路:

电平转换参考电路如下:

注意

- 此电平转换电路不适用波特率高于460800 bps的应用。

- 由于休眠状态下VDD_EXT会掉电,因此如果在需要休眠的应用场景用VDD_EXT做串口电平转换上拉的话,会导致模块无法休眠的情况。因此在需要进入休眠的场景下,建议用AGPIO3进行上拉。

- D2 必须选用低导通压降的肖特基二极管。 肖特基二极管以及 NPN 三极管的推荐型号如下:

对于波特率高于 460800bps 的应用,可以通过外加电平转换芯片来实现电压转换,参考电路如下:

此电路采用的是电平转换芯片是TI 的TXS0108E, 8 位双向电压电平转换器,适用于漏极开路和推挽应用,最大支持速率:

推挽:110Mbps开漏:1.2Mbps

3.6 USB接口****

Air780EP 的USB 符合USB2.0 规范,支持高速(480Mbps)、全速(12Mbps)模式和低速(1.2Mbps)模式。USB 接口可用于AT 命令传送,数据传输,软件调试和软件升级。

表格 8:USB 管脚定义

USB接口参考设计电路如下:

图表 9:USB 接口参考设计

- USB 走线需要严格按照差分线控制,做到平行和等长;

- USB 走线的阻抗需要控制到差分 90 欧姆;

- 需要尽可能的减少USB 走线的stubs,减少信号反射;USB 信号的测试点最好直接放在走线上以减少stub;

- 尽可能的减少USB 走线的过孔数量;

- 在靠近USB 连接器或者测试点的地方添加 TVS 保护管,由于USB 的速率较高,需要注意TVS 管的选型,保证选用的 TVS 保护管的寄生电容小于 1pF

- VBUS 作为USB 插入唤醒作用,并不直接参与 USB 插入检测,非必须,在不需要 USB 插入唤醒的场景也可以不接**。**

3.7 USB下载模式****

Air780EP 模块进入USB 下载模式:

- 在开机之前,把USB_BOOT 上拉到VDD_EXT

3.8 I2C

Air780EP 可支持两路I2C 接口:

- 兼容Philips I2C 标准协议

- 支持Fast mode (400Kbps)和 Slow mode(100Kbps)

- 只支持 master 模式,不支持 slaver 模式

- 可通过软件来配置内部的上拉电阻,1.8K 或者 20K

- 理论上最多可支持 127 个从设备

I2C 的参考电路如下:

Air780EP 的I2C 接口电压是 1.8V/3.3V 可配置,通过PIN100 IO_SEL 配置IO 口电平,能够满足大部分外设的直接需求,但是如果要和 5V 或者以上电平的外设通信,那就必须要加电平转换电路:

上图推荐用 AGPIO3 上拉,在不需要模块进入休眠的场景或者允许休眠掉电的场景也可以用 VDD_EXT 上拉电平转换用的 NMOS 管必须选用结电容小于 50pF 的型号,推荐型号如下:

3.9 SIM卡接口****

Air780EP 支持 2 路 SIM 卡接口,支持 ETSI 和 IMT-2000 卡规范,支持 1.8V 和 3.0V USIM 卡。以满足双 SIM卡切换的需求。

3.9.1 SIM 接口

下表介绍了 SIM 接口的管脚定义。

表格 9:SIM 卡接口管脚定义

3.9.2 双 SIM 卡切换说明

Air780EP 支持双卡单待,同一时间只能使用其中一个 SIM 通道。可以通过相应的 AT 指令进行SIM 卡通道切换:或者选择自动切换功能,系统会根据外部网络信号强度进行自动切换(自动切换功能通常用于同时使用不同运营商SIM 卡的场景)。具体指令请参考《4G 模块AT 命令手册》

注意:

- 模块开机会默认检测 SIM1 通道,在SIM1 通道检测到SIM 卡不在位的情况下才会去检测SIM2 通道。

- USIM_DET 信号为 SIM 卡插拔检测管脚,上下边沿电平触发中断,触发系统进行SIM1 通道的卡在位检测。而SIM2 通道不支持SIM 卡插拔检测。

- 对于内置贴片SIM 卡的双卡应用场景,如网络摄像头(IPC)场景,建议将贴片 SIM 卡置于SIM2

通道,外置插拔SIM 卡座置于SIM1 通道,以实现优先使用外置插拔SIM 卡的效果。

3.9.3 SIM 接口参考电路

下图是 SIM 接口的参考电路,使用 6pin 的 SIM 卡座。

如果需要用到 sim 卡在位检测,推荐电路如下。

在SIM卡接口的电路设计中,为了确保SIM卡的良好的功能性能和不被损坏,在电路设计中建议遵循以下设计原则:

- SIM卡座与模块距离摆件不能太远,越近越好,尽量保证SIM卡信号线布线不超过20cm。

- SIM卡信号线布线远离RF线和VBAT电源线。

- 为了防止可能存在的USIM_CLK信号对USIM_DATA信号的串扰,两者布线不要太靠近,在两条走线之间增加地屏蔽。且对USIM_RST_N信号也需要地保护。

- 为了保证良好的ESD保护,建议加TVS管,并靠近SIM卡座摆放。选择的ESD器件寄生电容不大于50pF。在模块和SIM卡之间也可以串联22欧姆的电阻用以抑制杂散EMI,增强ESD防护。SIM卡的外围电路必须尽量靠近SIM卡座。

- 在需要模块进入休眠的场景SIM_DET禁止用VDD_EXT上拉,否则会造成无法休眠的问题。建议用AGPIO3上拉,或者用SIM_DET IO内部上拉的方式

3.10 ****LDO输出

注意:

- VDD_EXT 作为大部分IO 的内部供电,在模块进入休眠后会掉电关闭,以降低功耗。

VDD_EXT 在模块休眠期间,会随着模块底层频繁唤醒做网络交互以维持网络注册状态。客观上造成 VDD_EXT 在模块休眠期间输出周期不等的高脉冲,如果用 VDD_EXT 做某些 IO 如唤醒IO 管脚,或者 MAIN_UART 的上拉,就会造成频繁触发 IO 中断导致模块无法进入休眠。

- 在需要休眠的场景可以用AGPIO3 进行上拉。

3.11 功能管脚

******3.11.1 **MAIN_RI

表格 10:MAIN_RI 信号动作

如果模块用作主叫方,MAIN_RI 会保持高电平,收到 URC 信息或者短信时除外。而模块用作被叫方时,MAIN_RI 的时序如下所示:

3.11.2 MAIN_DTR

模块支持两种睡眠模式:

睡眠模式 1:发送 AT+CSCLK=1,通过 MAIN_DTR 管脚电平控制模块是否进入睡眠睡眠模式 2:发送 AT+CSCLK=2,模块在串口空闲一段时间后自动进入睡眠

3.11.3 状态指示灯

Air780EP 用一个管脚来指示开机状态,用两个管脚信号来指示网络的状态。如下两表分别描述了管脚定义和不同网络状态下的逻辑电平变化:

表格 11:网络指示管脚定义

指示灯参考电路如下图所示:

3.12 省电功能

根据系统需求,有两种方式可以使模块进入到低功耗的状态。对于AT版本使用“AT+CFUN”命令可以使模块进入最少功能状态。

3.12.1 最少功能模式 / 飞行模式

最少功能模式可以将模块功能减少到最小程度,此模式可以通过发送“AT+CFUN=”命令来设置。参数可以选择 0,1,4。

- 0:最少功能(关闭RF和SIM卡);

- 1:全功能(默认);

- 4:关闭RF发送和接收功能;

如果使用“AT+CFUN=0”将模块设置为最少功能模式,射频部分和 SIM 卡部分的功能将会关闭。而串口依然有效,但是与射频部分以及 SIM 卡部分相关的 AT 命令则不可用。

如果使用“AT+CFUN=4”设置模块,RF部分功能将会关闭,而串口依然有效。所有与RF部分相关的AT命令不可用。

模块通过“AT+CFUN=0”或者“AT+CFUN=4”设置以后,可以通过“AT+CFUN=1”命令设置返回到全功能状态。

3.12.2 睡眠模式(慢时钟模式)

串口应用

串口应用下支持两种睡眠模式:

- 睡眠模式 1:通过 MAIN_DTR 管脚电平控制模块是否进入睡眠

- 睡眠模式 2:模块在串口空闲一段时间后自动进入睡眠

睡眠模式 1

开启条件:

发送 AT 指令 AT+CSCLK=1

模块进入睡眠:

控制 MAIN_DTR 脚拉高,模块会进入睡眠模式 1

模块退出睡眠:

拉低 MAIN_DTR 脚 50ms 以上,模块会退出睡眠模式可以接受 AT 指令模块在睡眠模式 **1 **时的软件功能:

不响应 AT 指令,但是收到数据/短信/来电会有 URC 上报 HOST 睡眠时,模块收到数据 / 短信 / 来电如何唤醒 HOST : MAIN_RI 信号

睡眠模式 2

开启条件:

发送 AT 指令 AT+CSLCK=2

模块进入睡眠:

串口空闲超过 AT+WAKETIM 配置的时间(默认 5s),模块自动进入睡眠模式 2

模块退出睡眠:

串口连续发送 AT 直到模块回应时即退出睡眠模式 2

模块在睡眠模式 2 时的软件功能:

不响应 AT 指令,但是收到数据/短信/来电会有 URC 上报 HOST 睡眠时,模块收到数据 / 短信 / 来电如何唤醒 HOST : MAIN_RI 信

USB****应用

开启条件:

USB HOST 必须支持 USB suspend/resume

模块进入睡眠:

HOST 发起 USB suspend

模块退出睡眠:

HOST 发起 USB resume

HOST 睡眠时,模块收到数据 / 短信 / 来电如何唤醒 HOST :

MAIN_RI 信号

3.13 模式切换汇总

表格 13:模式切换汇总

接下来我们学习第三部分。

审核编辑 黄宇

-

Air780EP硬件设计原理解析(第一部分)2024-11-06 1524

-

Air780E/Air780EP/Air780EQ/Air201模块遇到死机问题如何分析2024-07-19 2037

-

救世主Ga N来啦!第二部分:测量2022-11-03 825

-

如何实现更高的系统效率——第二部分:高速栅极驱动器2022-11-02 737

-

超声波感应器会被用于何处?—— 第二部分2022-11-01 1023

-

有时你需要一点收获第二部分2021-04-19 833

-

AN-389: 使用Σ-Δ转换器—第二部分[中文版]2021-03-19 1071

-

如何使用 Nios II 处理器进行你中意的设计之第二部分教程2018-06-11 6180

-

2012年PSoC数模混合设计培训_第二部分2017-10-27 1106

-

中国NB-IOT产业联盟-第二部分问题清单-201608242017-01-11 1204

-

常用单片机实例与仿真_第二部分2015-11-10 641

-

AT91SAM9260使用手册第二部分2010-03-10 1413

-

实现免调整VCO1的IC (第二部分)2006-05-07 1232

全部0条评论

快来发表一下你的评论吧 !