3D-NAND浮栅晶体管的结构解析

描述

文章来源:半导体与物理

原文作者:jjfly686

本文介绍了3D-NAND浮栅晶体管结构。

传统平面NAND闪存技术的扩展性已达到极限。为了解决这一问题,3D-NAND闪存技术应运而生,通过在垂直方向上堆叠存储单元,大幅提升了存储密度。本文将简要介绍3D-NAND浮栅晶体管。

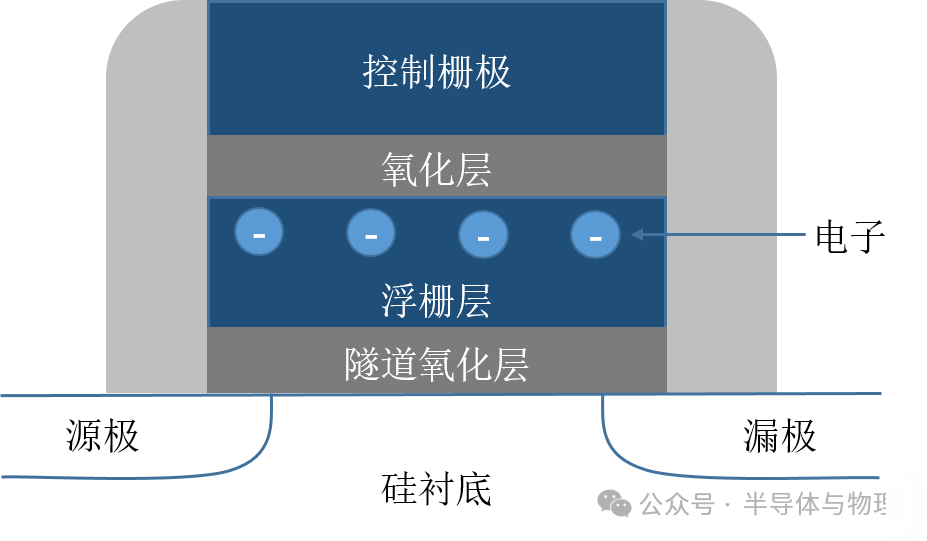

浮栅晶体管的工作原理

浮栅晶体管是闪存技术的核心组件,其基本原理是通过在浮栅中存储或释放电荷来改变晶体管的阈值电压,从而实现数据的写入和擦除。浮栅是一个隔离的导电层,通常由多晶硅制成,能够长时间保持电荷,确保数据的持久性。

(平面浮栅晶体管)

3D-NAND中的浮栅晶体管结构

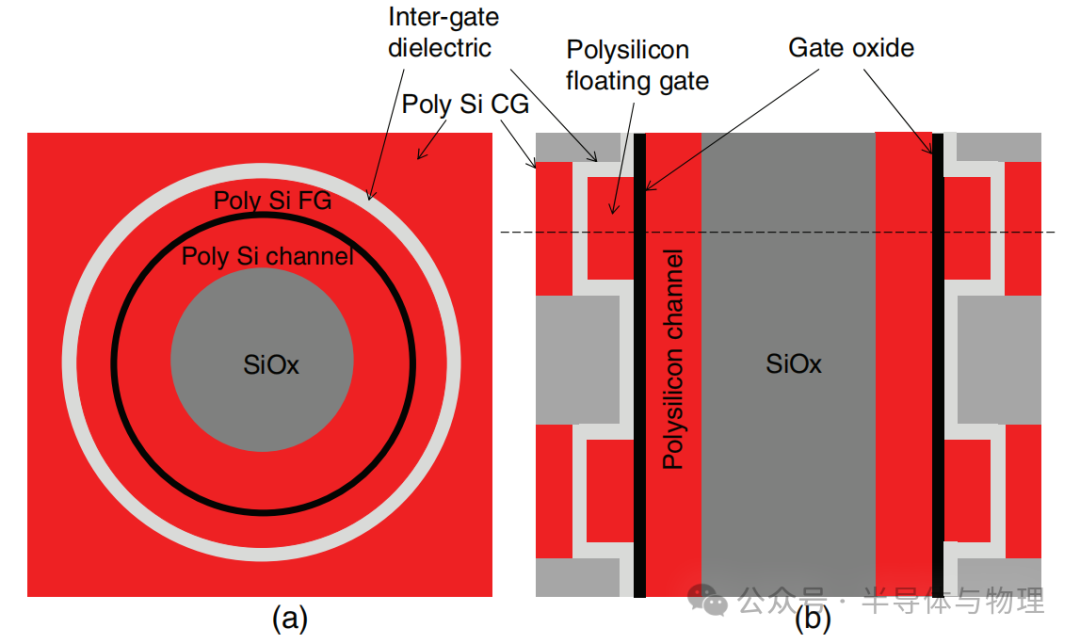

1.第一种材料结构

(a) 显示了3D-NAND单元的俯视图,其中包含一个多晶硅浮栅,该浮栅由氧化物-多晶硅-氧化物-氮化物(OPOP)堆栈组成。这种结构允许每个存储单元独立地存储电荷,从而表示不同的数据状态。

图(b) 是3D-NAND单元的侧视截面图,展示了多晶硅浮栅的具体位置。在这个结构中,浮栅位于控制栅和半导体多晶通道之间,并通过隧穿氧化层与衬底隔离。当向控制栅施加电压时,电子可以通过量子隧穿效应进入浮栅或从浮栅中逃逸,从而实现数据的写入和擦除。

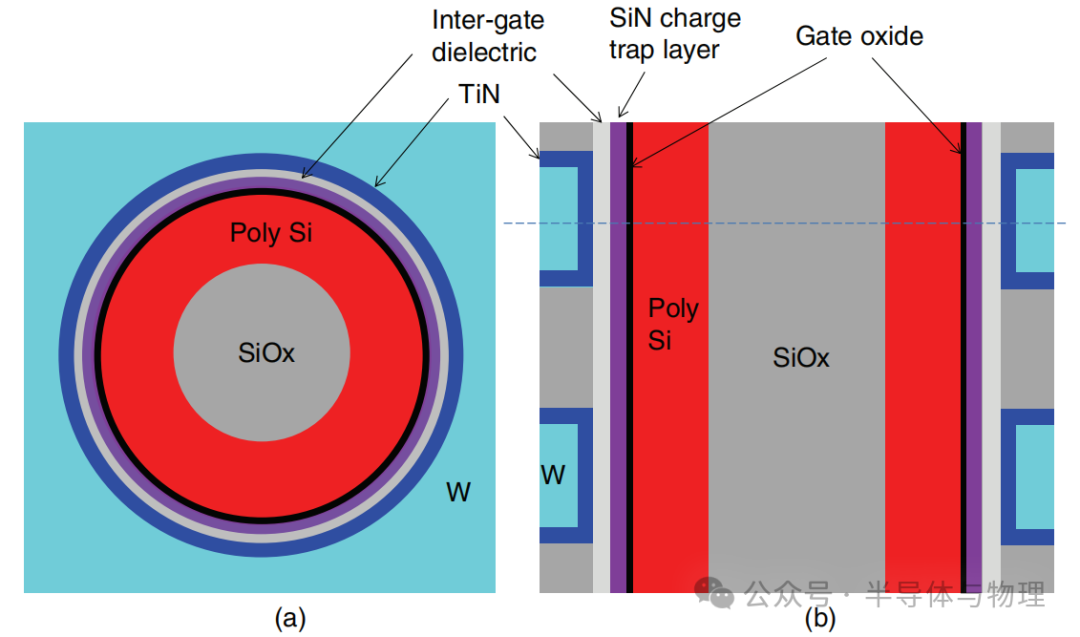

2.第二种材料结构

图2(a) 显示了3D-NAND单元的俯视截面图,其中包含一个氮化物材料电荷陷阱层,该层由氧化物-氮化物-氧化物-氮化物(ONON)堆栈组成。与多晶硅浮栅相比,氮化物电荷陷阱层具有更好的耐久性和数据保持能力,因为电荷不是直接存储在导体中,而是被陷阱在氮化物材料的缺陷中,这有助于减少数据丢失的风险。

图(b) 是3D-NAND单元的侧视截面图,展示了氮化物电荷陷阱层的具体位置。在这种结构中,电荷陷阱层位于控制栅和多晶硅之间,通过隧穿氧化层与衬底隔离。当向控制栅施加电压时,电子可以通过量子隧穿效应进入电荷陷阱层或从电荷陷阱层中逃逸,从而实现数据的写入和擦除。

-

什么是3d晶体管2012-08-08 3777

-

晶体管的结构特性2013-08-17 3817

-

IGBT绝缘栅双极晶体管的基本结构与特点2019-03-27 2433

-

IGBT绝缘栅双极晶体管2019-05-06 2167

-

绝缘栅双极晶体管(IGBT)2009-04-14 7467

-

绝缘栅双极晶体管IGBT2009-05-12 1836

-

绝缘栅双极晶体管原理、特点及参数2009-10-06 7150

-

绝缘栅双极晶体管2009-11-05 768

-

联栅晶体管(GAT)是什么意思?2010-03-05 3667

-

绝缘栅双极晶体管结构与工作原理解析2017-11-29 17292

-

Nand Flash结构及错误机制2022-02-08 568

-

NAND 闪存概述2022-02-10 915

-

详解三维NAND集成工艺(3D-NAND Integration Technology)2023-02-03 18278

-

浮栅晶体管的组成结构以及原理2024-11-24 5336

全部0条评论

快来发表一下你的评论吧 !