使用ECP5 FPGA解决网络边缘 智能、视觉和互连应用设计挑战

电子说

描述

莱迪思半导体白皮书

引言

随着传感器、低成本摄像头和显示屏在当今嵌入式设计中的使用量飞速增长,市场上出现了许多激动人心的全新智能和视觉应用。与此同时,嵌入式视觉应用的爆炸式发展也让设计工程师对处理资源需求有了一个新的认识。包含丰富数据的全新视频应用促使设计工程师重新考虑到底采用哪种器件,是专用应用处理器(AP)、ASIC还是ASSP?然而,在某些情况下,在现有应用处理器、ASIC或ASSP方面的大量软件投入以及全新器件的高启动成本已然成为上述应用更新迭代的阻碍。这一次,摆在眼前的问题推动设计工程师寻求一种协处理解决方案,不仅要能够为包含丰富数据的全新应用提供所需的额外功能,同时还要满足系统成本和功耗的严苛要求。

除此之外,市场上对于面向移动应用的低成本MIPI外设的广泛采用也催生了从未有过的互连挑战。设计工程师既希望利用最新一代MIPI摄像头和显示屏的量产成本优势,同时又希望能够保有在传统设备上的投入。那么在这种快速发展的大环境中,设计工程师该如何解决传感器、嵌入式显示屏和应用处理器之间不断涌现的接口不匹配问题呢?

设计工程师需要一种高度灵活的解决方案,能够实现高性能、“业内最佳”的协处理器,满足视觉和智能应用对于逻辑资源和高度并行计算能力的需求,同时增加对各类I/O标准和协议的互连支持。此外,这样的解决方案还应当具备高度可扩展的架构,并支持使用主流高数据速率的低成本外部DDR DRAM。最后,该解决方案还需要针对低功耗和低成本运算进行优化,并为设计工程师提供业界领先的超小尺寸封装。

在本文中,我们将为您介绍ECP5™和LatticeECP3™ FPGA如何为嵌入式设计实现协处理和互连解决方案,并重点探讨这些解决方案在工业、消费电子、汽车和机器学习领域的应用实例。

为视觉与智能应用实现高效的协处理解决方案

莱迪思半导体®推出的ECP5和LatticeECP3 FPGA系列可实现“业内最佳”的协处理器,并针对互连功能以及高性能和低功耗进行了优化。ECP5 FPGA系列提供业界最小尺寸封装(10x10 mm),并具备高达85K查找表(LUT),功能密度相比竞品高出近2倍,同时成本和功耗也大幅降低。ECP5 FPGA支持与ASIC、ASSP和应用处理器实现互连,并具备优化的I/O和体系架构。增强的嵌入式DSP块和高度并行的FPGA逻辑架构为计算密集型协处理功能提供了所需的高性能支持。ECP5 FPGA系列可提供高达4条SERDES互连通道,支持PCI Express(Gen1,Gen2)、以太网(1GbE,SGMII,XAUI)、CPRI、嵌入式显示端口( eDP)和JESD204B,每条通道速率为250 Mbps至5 Gbps。同时,器件上的可编程I/O还支持各类接口,包括DDR3、LPDDR3、LVCMOS、RGMII、XGMII、LVTTL、LVDS、Bus-LVDS、7:1 LVDS、LVPECL和MIPI D-PHY。

当协处理或互连应用需要超过85K LUT或超过4条SERDES通道时,设计工程师可以选择LatticeECP3 FPGA。LatticeECP3 FPGA系列可提供最高150K LUT和6.8 Mbit SRAM,封装尺寸小至10x10 mm。相比ECP5 FPGA系列,该产品系列最高支持16个3.125 Gbps SERDES通道。此外,该产品系列中的器件均支持800 Mbps DDR3和LVDS,并且能够提供超过500个可编程系统I/O缓冲器,支持以太网(通过RGMII和XGMII)以及大量额外的I/O接口,而嵌入式SERDES则支持PCIe、以太网(通过SGMII和XAUI)、HDMI、高速串行I/O(Serial Rapid I/O)、CPRI、JESD204A/B等。LatticeECP3 FPGA系列的功耗低至0.5 W。与ECP5 FPGA系列一样,使用LatticeECP3 FPGA的设计工程师可以使用高度并行的FPGA逻辑架构高效地执行计算密集型功能,并通过FPGA分担视觉和智能功能,如图像处理和分析任务以降低处理器工作负载,从而实现更低的功耗和更高的性能。

为工业应用实现视觉处理解决方案

在工业领域,基于ECP5 FPGA的协处理能够发挥重要作用,可用于降低视频摄像头、监控和机器视觉应用中应用处理器、ASIC或ASSP的计算负载。图1展示了一款典型的工业摄像头应用。在下方的图示中,FPGA位于图像传感器和以太网PHY之间。图像传感器将图像数据流传输到FPGA,然后FPGA基于H.264编码进行图像处理或图像压缩。FPGA的片上嵌入式RAM块(Embedded Block RAM, EBR)和DSP块实现高性能宽动态范围(WDR)和图像信号处理(ISP)功能。最后,FPGA将图像数据通过以太网进行传输。

图1:通过实现图像处理或压缩功能,ECP5 FPGA可降低工业摄像头应用中应用处理器的计算负载

除了进行图像处理和压缩之外,如果应用处理器接口的类型或数量与摄像头或传感器的不匹配,FPGA还可用于实现它们之间的视频桥接。为了满足工业应用对于灵活互连的需求,莱迪思推出了可编程ECP5 12K器件,能够连接到包括LVDS、MIPI和LPDDR3在内的常用接口。该器件能够以低成本提供LED控制器、机器视觉系统和工业电机控制等应用中预处理和后处理功能所需的逻辑、存储器和DSP资源。

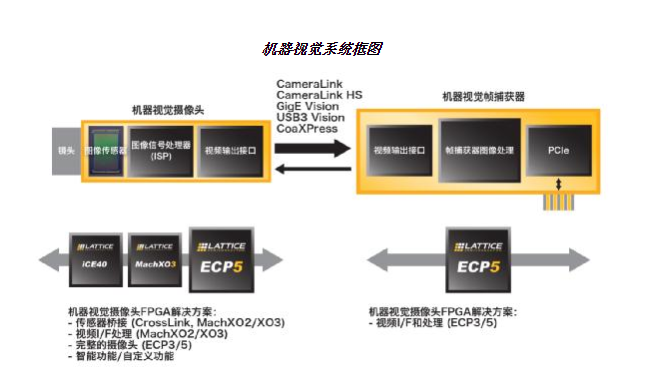

除了常见工业摄像头应用之外,机器视觉(工业领域里更专业的摄像头应用)也可受益于ECP5 FPGA提供的互连和协处理能力。图2中的框图展示了FPGA可在常见的工业机器视觉系统中发挥的多种作用。在摄像头应用领域,FPGA可用于实现传感器桥接、完整的摄像头ISP或定制功能来帮助系统设计工程师实现差异化的终端产品。对于图像采集卡而言,像ECP5一样的FPGA还可以解决视频接口问题和实现图像处理功能。

机器视觉系统框图

图2:在常见的工业机器视觉解决方案中,FPGA可用于实现各种接口桥接和处理功能

为智慧城市实现智能交通和监控摄像头应用

智能交通系统(ITS)包括交通流量监控、交通违章识别、智能停车和收费等应用,是智慧城市的重要组成部分。上述系统通常需要智能交通摄像头,用于准确检测车辆多个方面的信息,例如车牌,即使在恶劣的环境中也要在网络边缘进行视频分析,不用将原始视频流发送回云端进行处理。单独的应用处理器通常不能同时满足系统功耗和实时处理的要求。低功耗、小尺寸的ECP5 FPGA系列可用作应用处理器的协处理器,在网络边缘实现系统所需的高效实时处理功能。

除了上文中提到的ISP外,ECP5 FPGA还可以实现视频分析功能,进一步减轻应用处理器的计算密集型任务,从而降低系统功耗、实现更高的实时性能。FPGA可为智能摄像头应用实现目标侦测、图像处理和图像增强等解决方案。例如,侦测目标可以是监控摄像头实例中的人脸图像或是交通摄像头实例中的车牌。

图3:ECP5 FPGA为智能摄像头应用实现图像处理和视频分析功能框图,分担应用处理器的计算密集型任务

在图3所示的智能交通摄像头实例中,FPGA基于传感器捕获的图像数据检测到车辆牌照,即使在低光照或强背光条件下亦能执行图像增强以生成清晰图像 - 针对目标(车牌)和背景(图像中的剩余部分)使用不同的曝光设置,然后融合目标和背景图像以生成更清晰的图像。然后,FPGA生成的目标侦测结果输入到应用处理器运行的分析算法。使用ECP5 FPGA的并行处理器架构分担分析算法中计算密集程度最高的步骤,智能摄像头能够在保持低功耗的同时提高性能。

为移动系统实现沉浸式增强现实(AR)和虚拟现实(VR)应用

随着AR/VR市场需求不断增长,当前基于头戴式显示器(HMD)的系统面临着移动应用处理器运行内容时性能不足的问题。因此,要实现身临其境的AR/VR体验所需的基于视觉的位置追踪功能,对于处理器而言是颇具挑战性的。在这种情况下,ECP5 FPGA的高效并行处理架构非常适合用于实现基于立体摄像头和LED标记的位置跟踪解决方案。与应用处理器相比,FPGA能够提供低延迟、低功耗的图像处理支持。FPGA的可编程架构和I/O也使得系统设计工程师能够根据产品要求轻松选择来自不同厂商的图像传感器。

在“outside-in”的位置追踪解决方案中,立体摄像头被放置在房间内(在室内摄像头看用户),通过捕捉安装在用户头盔和手柄控制器上的LED标记来追踪用户的运动(诸如身体运动和手部运动),如下方图4所示。安装在三脚架上摄像头单元内部的FPGA基于立体摄像头捕获的数据来计算用户的位置、身体和手部动作,然后将数据通过无线方式发送到用户头盔中的移动应用处理器,最终通过AR/VR应用呈现现实世界与虚拟世界的互动。立体摄像头为运行在FPGA上的算法提供了深度感知支持,从而实现三坐标定位。

图4:使用立体摄像头(放置在房间内)的“outside-in”位置追踪解决方案,通过捕获安装在用户头盔和手柄控制器上的LED标记来跟踪用户的身体和手部动作

在“inside-out”的位置追踪解决方案中,安装在用户头盔上的立体摄像头(从用户所在位置通过“inside-out”的方式朝向室内环境)捕获安装在手柄控制器上的LED标记来跟踪用户手部动作,如图5所示。安装在用户头盔摄像头单元内的FPGA基于立体摄像头数据来计算用户的手部动作,然后将数据发送到头盔中的移动应用处理器,最终通过AR/VR应用呈现出来。

图5:使用立体摄像头(安装在用户头盔上)的“inside-out”位置追踪,通过捕获安装在手柄控制器上的LED标记来跟踪用户手部动作

虽然“outside-in”和“inside-out”这两种追踪解决方案都能实现沉浸式体验,但“outside-in”系统可以提供更卓越的沉浸感,因为它还可以通过头盔上的LED标记跟踪身体运动(如步行、跑步、蹲、跳等) ,将现实世界中的身体运动映射到虚拟世界中。

在这两个系统中,用户的运动信息需要以极低的延迟立刻呈现在虚拟世界中,实现最为逼真的用户体验。ECP5 FPGA的并行处理能力是实现低延迟传输的关键。此外,它的低功耗和小尺寸封装特性也是实现畅行无阻的移动体验的关键之所在。

为汽车ADAS系统实现协处理和桥接解决方案

汽车市场对视觉处理和互连解决方?6?7?6?7案的需求正在大幅增长。市场研究公司IC Insights的分析师预计,随着在新一代汽车设计中要求使用后置摄像头的新规定施行以及在汽车设计中引入摄像头以取代两侧后视镜、实现盲点检测和车道跟踪功能的发展趋势,CMOS图像传感器将在2015年至2020年间随着汽车领域中全新应用的兴起将以55%的复合年增长率实现增长。

在这个快速成长的市场中,汽车设计工程师所需的解决方案不仅要能够实现预处理和后处理功能,还要能够为高级驾驶辅助系统(ADAS)和信息娱乐应用构建优化的互连解决方?6?7?6?7案。随着汽车制造商开发的ADAS系统日趋复杂,设计工程师面临着两大挑战。第一个挑战是如何解决摄像头数量不断增长带来的接口问题?大多数现代处理器仅具备两个摄像头接口,而很多ADAS系统需要多达8个摄像头才能满足不断发展的自动驾驶技术要求。第二个挑战是设计工程师要如何基于来自上述摄像头的大量数据进行图像处理?

为了应对这些挑战,设计工程师需要一种能够提供协处理资源的解决方案,可将来自多个摄像头的多路视频流拼接在一起,或对来自多个摄像头的输入进行图像处理(如白平衡、鱼眼校正、除雾),然后将这些数据通过单个数据流传输到应用处理器。汽车设计工程师还需要能够灵活地操作仪表板、仪表盘以及后座信息娱乐系统的的多个显示屏,以及在传统接口和新的MIPI接口之间实现桥接。

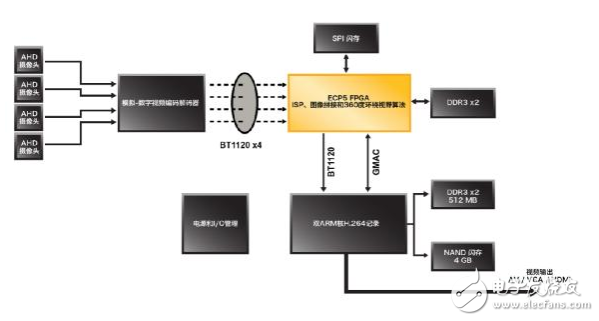

莱迪思汽车级ECP5 FPGA(AEC-Q100)可为这些应用提供用于加速图像处理流水线所需的并行处理能力,而大量的I/O则可用于连接到更大的摄像头阵列。能够反映这种趋势的一个实例就是现在越来越多的汽车都具备鸟瞰功能。一般来说,鸟瞰功能是指从汽车上方20英尺处向下看的实时视频图像。ADAS系统通过将来自4个或更多摄像头的数据拼接在一起实现宽视野(FoV)来实现上述功能。

一直以来,设计工程师都是使用单个处理器来处理来自单个摄像头的图像数据。现在,设计工程师可以使用单个ECP5 FPGA替代多个处理器,聚合来自多个摄像头的数据,并进行图像拼接、鱼眼去除、白平衡、HDR调整等操作以尽可能提高图像质量,然后将高质量图像发送到处理器进行下一个步骤。使用这种方法的设计工程师可以在获得更高性能的同时降低成本和功耗。

图6展示了莱迪思客户如何构建上文中提到的解决方案。该鸟瞰系统从安装在汽车四周的摄像头(前方、后方和两侧)捕获视频图像。ECP5 FPGA用于对视频数据继续进行处理和拼接以提供360度视野。在这种情况下,一片FPGA即可替代多个ARM处理器。该系统最终呈现的是清晰的1080p 60 fps视频。除ECP5 FPGA之外,该方案仅使用了一个低端ARM处理器用于初始校准和视频编码/记录功能。

图6:展示了开发工程师如何使用单个ECP5 FPGA实现从前需要使用多个ARM处理器的鸟瞰系统

图7:展示了ECP5 FPGA使用来自4个摄像头的图像输入实现的360度全景视野

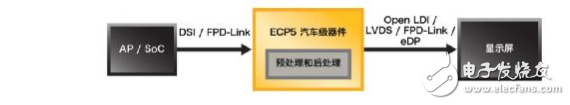

FPGA可在汽车设计中扮演的另一个重要角色是构建传统接口与越来越流行的MIPI摄像头和显示屏之间的低成本桥接解决方案。

图8:在车载信息娱乐系统中,ECP5 FPGA可用于预处理和后处理功能,并实现应用处理器和显示屏之间的视频桥接

例如,在图8的框图中,ECP5 FPGA位于应用处理器或SoC与一个或多个汽车显示屏之间,用于预处理和后处理功能,并实现DSI或FPD-Link接口应用处理器与Open LDI、LVDS、FPD-Link或eDP接口显示屏之间的桥接。FPGA还可用于多种其他信息娱乐应用,包括分别将单个视频输出到双后座显示屏,对图像进行裁剪和格式化以获得特定的视频分辨率。

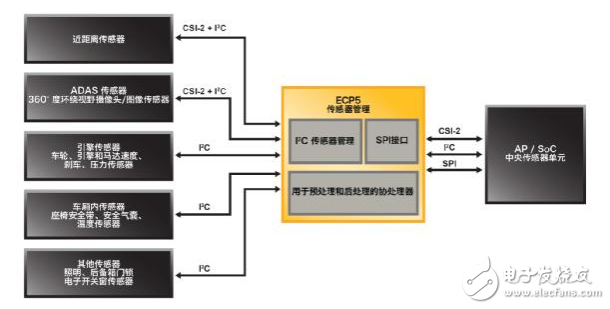

ECP5的丰富处理资源也为实现各种传感器桥接、聚合和协处理解决方案奠定了基础。如图9所示,ECP5 FPGA用于控制和聚合来自多种传感器数据的智能中心。通过对传感器数据进行预处理和后处理以及实现I2C管理功能和SPI接口,FPGA可以显著降低应用处理器的计算负载。

图9:ECP5 FPGA实现数据桥接和智能中心,用于控制和聚合多种类型的传感器

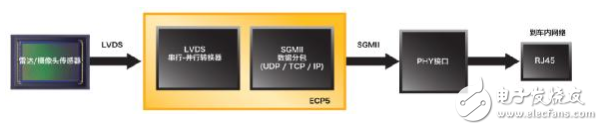

另一个桥接、聚合和协处理解决方案实例则使用莱迪思汽车级FPGA的3.2 Gbps SERDES功能聚合来自多个雷达或摄像头的数据,并通过BroadR-Reach或以太网等汽车内部网络?6?7?6?7传输。在图10中,来自多个传感器的数据通过LVDS接口传输到ECP5 FPGA,然后ECP5 FPGA对数据进行聚合和打包,通过基于SERDES的SGMII接口传输到汽车内部网络。

图10:汽车级ECP5 FPGA的LVDS和3.2 Gbps SERDES功能用于实现多个雷达或摄像头的桥接和聚合,并通过SGMII传输到车载网络

实现网络边缘机器学习应用

展望未来,移动相关解决方案的影响力将不断增长,它们将继续利用移动处理器和MIPI传感器和显示屏的应用支持和规模制造优势为网络边缘实现智能功能。市场上对于部署人工智能(AI)、神经网络和机器学习来实现上述目标的需求在不断增长。

在机器学习应用领域,用于进行图像识别的神经网络经过训练之后可以识别猫的图像,举个例子,通过向神经网络投喂数以千计的图像并分配输入图像的权重直至神经网络能够正确识别猫的图像。开发数据架构和分配权重可能需要数TB的数据和大量的计算资源。因此,基于深度学习技术的机器学习应用的训练步骤放在使用高端GPU和FPGA的数据中心,只有在数据中心海量的计算需求才能得以满足。

模型经过训练之后,它将被移植到网络边缘应用中的嵌入式系统,然后为图像识别或语音识别等应用实现推理功能。在网络边缘应用领域,设备必须通过计算更快速、更高效地做出决定。因此,设计工程师需要将神经网络在“训练”阶段学到的经验教训应用到新数据,进行“推理”得出结果。为了在网络边缘应用领域实现推理功能,理想的解决方案要能够提供计算效率高的平台,并且满足功耗、尺寸和成本的严苛要求。

当今业界和学界的都认为机器学习需要高度专业化的硬件加速解决方案。但是,相关要求也会根据任务的不同而发生变化。例如,训练和推理可能需要不同的硬件。致力于训练应用的硬件设计工程师通常使用32位浮点运算来进行精度非常高的计算。而另一方面,致力于网络边缘应用领域推理功能的硬件设计工程师对于灵活性的需求要大于精确度,以便获得更高的处理速度或更低的功耗。事实上,最近的研究表明,对于许多应用来说定点与浮点解决方案在推理精度方面几乎相同,而且前者功耗更低。

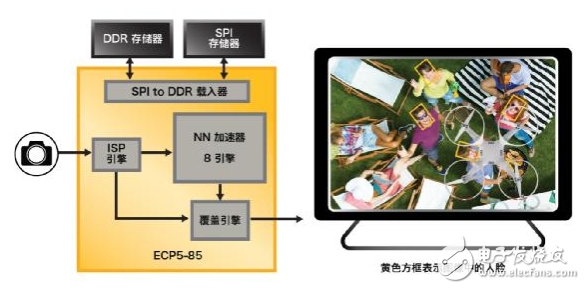

凭借丰富的嵌入式DSP资源、FPGA与生俱来的并行处理架构以及在功耗、尺寸和成本方面的显着领先优势,ECP5 FPGA是满足新兴AI市场上多元需求的理想选择。例如,ECP5 FPGA中的DSP能够以相比GPU浮点运算更低的功耗/MHz来进行定点运算。这些特性为功耗要求严苛的网络边缘智能解决方案开发者提供了极具吸引力的优势。图11展示了一个实例,其中ECP5 FPGA用于实现推理加速器,对来自摄像头的数据运行预先训练好的卷积神经网络(CNN)进行处理。运行在FPGA上的CNN引擎识别物体或人脸,并将结果发送到系统CPU,从而实现快速、低功耗的物体/面部识别功能。

图11:ECP5 FPGA为网络边缘智能应用实现卷积神经网络(CNN)加速器,从而实现物体/人脸识别功能

图12中的框图展示了实时人脸跟踪神经网络加速演示,在拥有85K LUT的ECP5-85 FPGA上运行时功耗仅为0.85 W。

图12:摄像头捕获的实时图像数据被输入到FPGA,FPGA确定人脸图像并输出结果,最后人脸图像在显示屏上高亮显示

基于FPGA实现的设计使得设计工程师能够灵活地实现向上或向下扩展,以满足终端系统中功耗与性能的平衡。在上面的实例中,基于更小尺寸的85K LUT FPGA的设计可以通过平衡性能和其他参数(例如降低帧速率、减小输入图像的帧大小或者减少用于神经网络的权重和激活值)来实现,从而进一步降低功耗。

此外,FPGA的可重新编程特性使得设计工程师能够满足快速变化的市场需求。随着算法的发展,用户可以通过软件轻松快速地更新硬件。这是GPU或ASIC无法企及的功能。

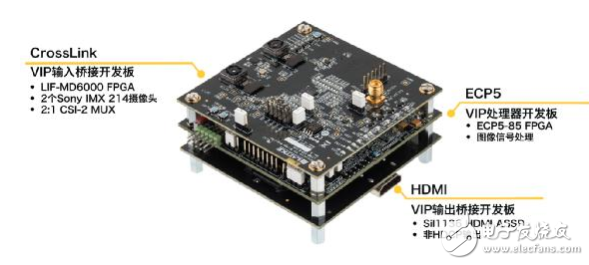

上述演示是基于嵌入式视觉开发套件(图13)实现的,该套件是莱迪思嵌入式视觉解决方案系列的一部分,为开发网络边缘嵌入式视觉解决方案提供了一个模块化平台。

图13:采用ECP5 FPGA、CrossLink FPGA和HDMI ASSP的莱迪思嵌入式视觉开发套件

总结

当今的设计工程师需要不断寻求新的途径来降低设计的成本、功耗和尺寸,同时为网络边缘应用领域实现更多智能功能。与此同时,他们要跟上网络边缘应用领域中新一代传感器和显示屏快速发展带来的性能和接口要求。莱迪思ECP5 FPGA系列能够为设计工程师提供两全其美的解决方案。ECP5 FPGA提供卓越的处理能力(高达85K LUT)和业界最小封装(10x10 mm),并带有SERDES,能够为设计工程师提供所需的协处理和互连资源。同时该产品系列的成本和功耗都比竞品更低,能够为开发工程师带来领先优势。

-

莱迪思ECP5系列FPGA续写“低功耗”神话2014-04-29 1595

-

开源Made with KiCad(134):Icepi Zero - 基于Lattice ECP5的便携FPGA开发板2025-07-14 3911

-

超低功耗FPGA解决方案助力机器学习2018-05-23 6776

-

基于ECP5 FPGA的网络边缘智能视觉和互连应用设计2019-07-18 1742

-

如何使用ECP5FPGA解决网络边缘应用设计挑战2020-10-21 1192

-

当AI遇到FPGA,会发生什么化学反应呢?2020-10-23 1650

-

莱迪思发ECP5 FPGA产品系列 适用于众多应用2014-04-16 1544

-

莱迪思新推ECP5 Versa开发套件 快速实现智能互连设计的原型开发2015-09-08 962

-

莱迪思半导体携手Mikroprojekt推出适用于网络边缘应用的先进系统开发平台2015-11-05 1007

-

莱迪思半导体为ECP5™ FPGA产品系列添加新成员2016-02-16 1029

-

Ximmerse VR/AR跟踪平台采用莱迪思的低功耗、小尺寸ECP5 FPGA2017-09-27 6122

-

莱迪思发布适用于宽带接入和视频等应用的ECP5 FPGA产品系列2018-02-11 3163

-

Lattice ECP5和ECP5-5G FPGA系列VIP处理器解决方案2018-04-06 13827

-

对Lattice ECP3/ECP5器件中的SerDes/PCS进行了简要的介绍2018-06-13 9388

-

基于全新ECP5-5G器件的IP和解决方案, 适用于工业和通信应用2018-07-31 1963

全部0条评论

快来发表一下你的评论吧 !