从电路的角度出发,提出了一种新的SOC跨时钟域同步电路设计的方法

电子说

描述

随着时间的推移,集成电路行业发展至今,已有类似如Intel这样先进的foundry,提出迈入10 nm制程的规划。高集成度的推行,也使芯片规模越来越大,功能越来越复杂,设计难度越来越高[1]。SOC的内部时钟的复杂化,导致跨时钟域的接口越来越多。针对这些异步信号的处理,国外的先驱们提出了很多建设性意见。但一般用到器件较多,考虑到成本因素,小规模IC将无法承受,并且如果输入脉冲高电平宽度低于最快时钟周期的话,一般无法适用。因此要想很好地解决这个问题,要处理好4个方面工作:一是如何简化电路;二是如何适应最小输入脉宽的问题;三是解决好亚稳态问题;四是要提高设计可靠性[2]。

1 处理跨时钟域信号的常用方法

实际使用时,往往会出现信号在频率不用的时钟域传递的情况,对于这种情况,一般用两种方法处理:结绳法、伴随有效控制信号法。当信号从一个时钟域进入另一个时钟域的时候,往往出现亚稳态问题[4]。亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。信号同步的目的是防止上一级亚稳态对下一级产生不良影响,采用信号同步的方法就要设计信号同步器。信号同步器主要有3种:电平同步器、边沿检测同步器、脉冲同步器[7-8]。但是这些常用方法本身存在缺点和不适应性。在解决实际问题中,需要根据具体情况,来设计具体的方案。

2 跨时钟域同步电路接口方法组成及工作原理

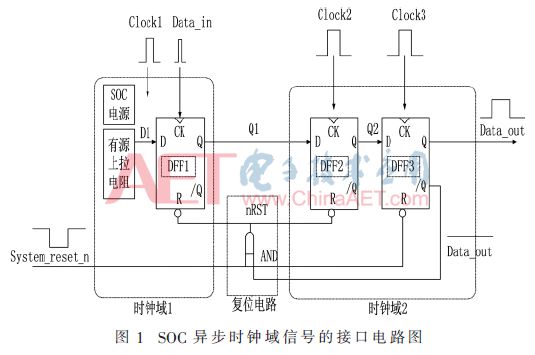

整个电路包括两个时钟域以及一个复位电路。时钟域1包含一个带有异步复位端的同步触发器。此触发器带有异步复位端R和同步时钟端CK,低电平产生复位,时钟上升沿开始锁存数据输入端D的状态。输出端有正相Q、反相/Q两种数据输出。时钟域2由两个同样的触发器组成,跟前面的一样由异步复位端R和同步时钟端CK,数据输入端D组成。输出端为正相Q、反相/Q两种,复位电路由一个与门组成,接收DFF3的反向/Q输出的数据,电路连接关系如图1所示。

3 跨时钟域同步电路的工作特征

在设计方案中,最大限度地保障了不漏信号。同时,时钟域1的输入脉冲信号宽度(高电平宽度)可以低于时钟域1的时钟单周期宽,电路正常工作,并且设计中脉冲宽度不再受限于时钟域1的时钟频率。第三,数据锁存器的数据输出端Q输出的脉冲信号宽度为时钟域2的时钟单周期宽,从而避免了误触发和多触发。

这种方法适用于输入信号类型为脉冲或电平,最终得到的结果为脉冲。如图2所示。

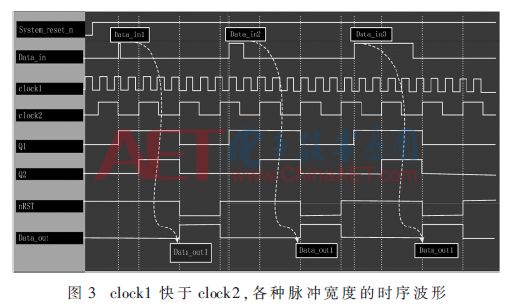

如图3所示,当clock1快于clock2时,图中Data_in1表示第一个输入脉冲,此脉冲由Data_in输入,脉冲宽度小于clock1的四分之一,同时,脉冲宽度小于系统最快时钟(clock1最快)的四分之一。Data_in1的上升沿到来的瞬间,Q1输出高电平“1”;Data_in1的上升沿之后,第一个clock2的上升沿到来瞬间,Q2输出高电平“1”;第二个clock2的上升沿到来瞬间,Data_out输出高电平“1”,与此同时,nRST生成复位信号,复位DFF1、DFF2,使Q1、Q2输出低;第三个clock2的上升沿到来瞬间,由于Q1、Q2早已变成低电平“0”,此时,“0”传递到Data_out,形成了一个clock2的周期宽度的脉冲Data_out1。

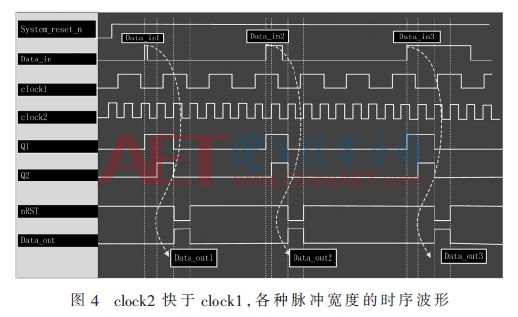

如图4所示,若clock2快于clock1时,图中Data_in1表示第一个输入脉冲,此脉冲由Data_in输入,脉冲宽度小于clock1的四分之一,同时,脉冲宽度小于系统最快时钟(clock2最快)的四分之一。

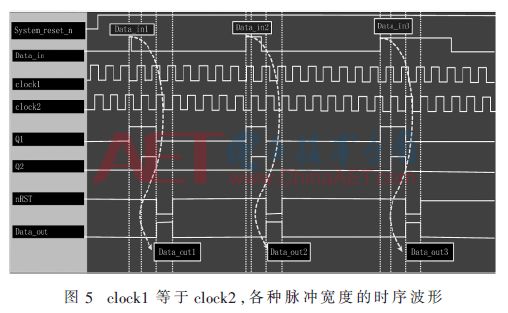

如图5所示,当clock2等于clock1时,图中Data_in1表示第一个输入脉冲,此脉冲由Data_in输入,脉冲宽度小于clock1的四分之一,同时,脉冲宽度小于系统最快时钟(clock2等于clock1)的四分之一。

4 仿真实验分析

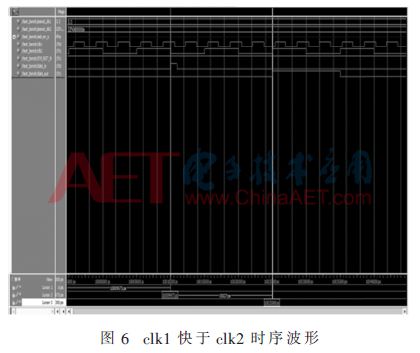

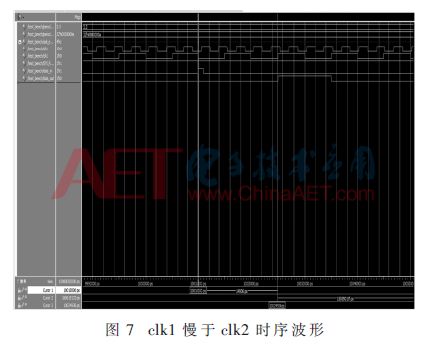

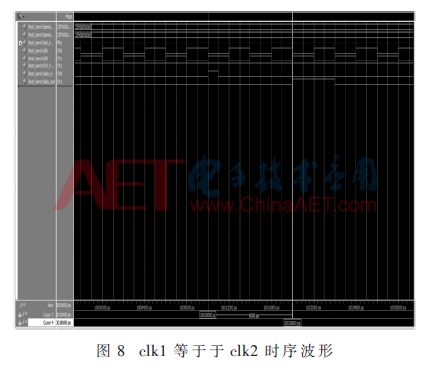

根据以上分析,通过Modelsim仿真分析得出以下时域图像可以验证上述特征,如图6~图8所示,快时钟为10 Hz,慢时钟为3.3 Hz,当时钟相等时为5 Hz。从仿真图像来看,亚稳态问题以及信号宽度受限于时钟宽度问题可以良好的解决。

5 应用与实测

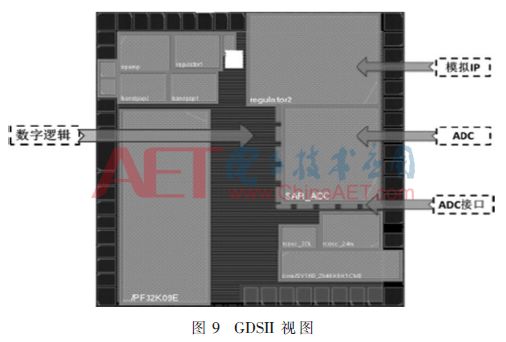

下方是基于和舰科技180 nm Pflash生产工艺设计实例。方案基于Faraday 0.18 ?滋m GII Library Standard Cell,图中灰色部分为模拟IP。下图中SAR_ADC的输出接口中,有一个脉冲信号的宽度等于系统时钟周期的一半。采用一般的手段,无法捕获这个脉冲,采用上文所述的电路则便高效地解决了这个问题。具体实现运行代码如下:

assign ADC_fine_rst = ADC_fine_sys || rst ;

%生成复位信号ADC_fine_rst,高有效,为使ADC_fine_sys和rst高电平产生复位,所以采用“逻辑或”运算。

always @(posedge drdy_dig or posedge ADC_fine_rst )

if (ADC_fine_rst)

ADC_fine <= 1'b0;

else

ADC_fine <= 1'b1;

%对应图1中的DFF1,drdy_dig为原始窄脉冲信号,若直接用系统时钟clk_system采样,将无法锁存。因此,此处drdy_dig接ADC_fine_reg的clk端。drdy_dig为ADC的IP电路输出信号,同步逻辑输出,有效压制毛刺,避免误触发。

always @(posedge clk_system or posedge ADC_fine_sys )

if (ADC_fine_sys)

ADC_fine_ff <= 1'b0;

else

begin

if (rst)

ADC_fine_ff <= 1'b0;

else

ADC_fine_ff <= ADC_fine;

end

%对应图1中的DFF2,此处rst的同步复位逻辑没有决定性意义,可以去除。

always @(posedge clk_system or posedge rst )

if (rst)

ADC_fine_sys <= 1'b0;

else

ADC_fine_sys <= ADC_fine_ff;

%对应图1中的DFF3,由原始drdy_dig信号,生成了ADC_fine_sys信号,从而实现跨时钟对接。

最后生成如图9所示的GDSII视图。按照生成GDSII视图制作如图10所示测试电路板。

经过MPW shuttle以及full MASK,采用天水华天的SOP20封装工艺,并设计板级测试系统,专项测试SAR_ADC结果如表1所示。ADC性能符合spec,排除测试环境的影响,信号捕获成功率等于100%,接口电路方案成功。

6 结论

从整体来看,该方法结构简单。其输入脉冲信号宽度可以低于本身的时钟单周期宽,使得设计中脉冲宽度不再受限于时钟频率;同时,时钟域1中输入脉冲信号宽度可以低于系统最快时钟单周期宽,进一步提高了采集的稳定性和适应性。时钟域2输出脉冲信号宽度为时钟域2的时钟单周期宽,从而避免了误触发,电路经过两级同步,这样很好地解决了亚稳态问题。总的来讲提高了采集的稳定性和适应性。

但是,这种处理方法对输入信号也有要求:输入毛刺宽度应小于DFF1(如图3)的最小时钟辨识度,否则将产生误触发。因此,这种方法的输入信号一般是SOC同步电路的输出信号,如输入为片外信号,一般要增加前置数字滤波电路。

-

从处理单bit跨时钟域信号同步问题来入手2023-06-27 2779

-

FPGA跨时钟域处理方法(一)2023-05-25 3234

-

跨时钟域电路设计总结2023-05-18 1598

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2694

-

FPGA跨时钟域处理简介2022-02-23 1203

-

介绍3种方法跨时钟域处理方法2021-09-18 23636

-

三种跨时钟域处理的方法2021-01-08 2350

-

如何将一种异步时钟域转换成同步时钟域2020-12-21 1762

-

探寻FPGA中三种跨时钟域处理方法2020-10-20 2397

-

跨时钟域为什么要双寄存器同步2020-08-20 3685

-

如何利用FPGA设计一个跨时钟域的同步策略?2018-09-01 6236

-

FPGA界最常用也最实用的3种跨时钟域处理的方法2017-11-15 14846

-

跨时钟域信号的几种同步方法研究2012-05-09 1354

全部0条评论

快来发表一下你的评论吧 !