MS1242/MS1243——24bit 高精度、低功耗模数转换器

电子说

描述

产品简述

MS1242/MS1243是一款高精度、宽动态范围、∆-Σ模数转

换芯片,其工作电压为2.7V至5.25V,可以达到24bit无失码转

换,有效精度可达21bit。MS1242/MS1243可以广泛使用在工

业控制、称重、液体/气体化学分析、血液分析、智能发送

器、便携式测量仪器等领域。

主要特点

⚫ 24位无失码、21位有效精度模数转换器

⚫ 集成50Hz、60Hz陷波滤波器

⚫ INL小于0.0015%

⚫ 可编程增益(1128)

⚫ 单周期建立时间

⚫ 可编程数据速率输出

⚫ 外接参考电压范围:0.1V5V

⚫ 集成校准功能

⚫ 兼容SPI总线接口

⚫ 低功耗

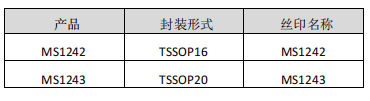

⚫ 4个模拟输入通道 (MS1242)

⚫ 8个模拟输入通道 (MS1243)

应用

◼工业过程控制

◼重量计

◼液体/气体化学分析

◼血液计

◼智能变换器

◼便携式设备

产品规格分类

管脚图

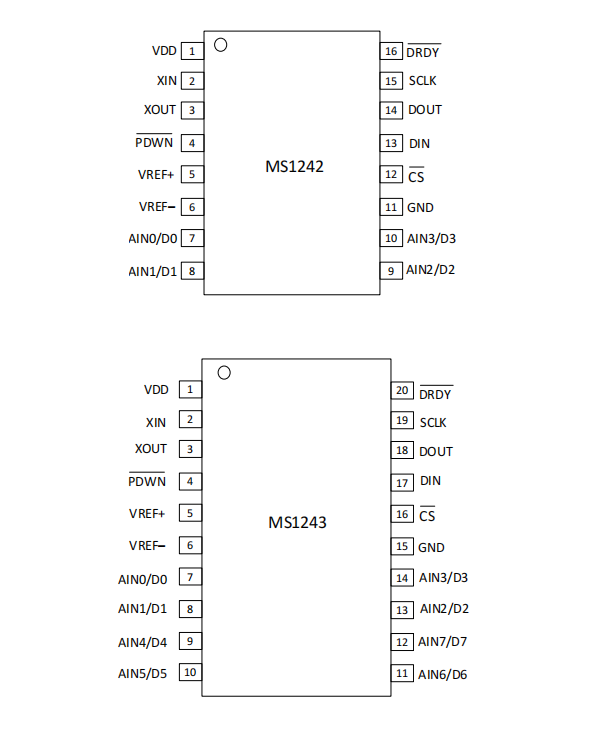

管脚说明

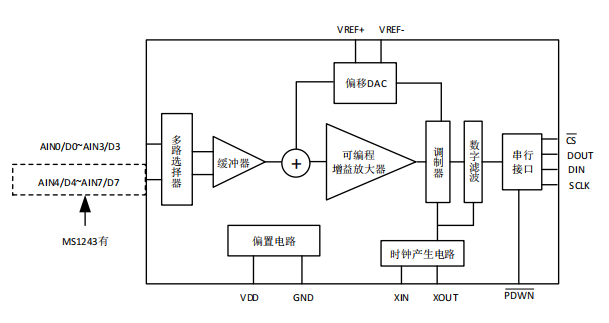

内部框图

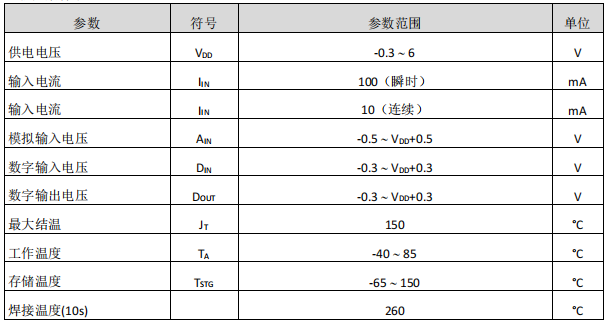

极限参数

芯片使用中,任何超过极限参数的应用方式会对器件造成永久的损坏,芯片长时间处于极限工作

状态可能会影响器件的可靠性。极限参数只是由一系列极端测试得出,并不代表芯片可以正常工作在

此极限条件下。

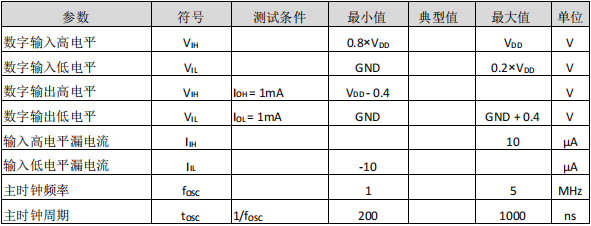

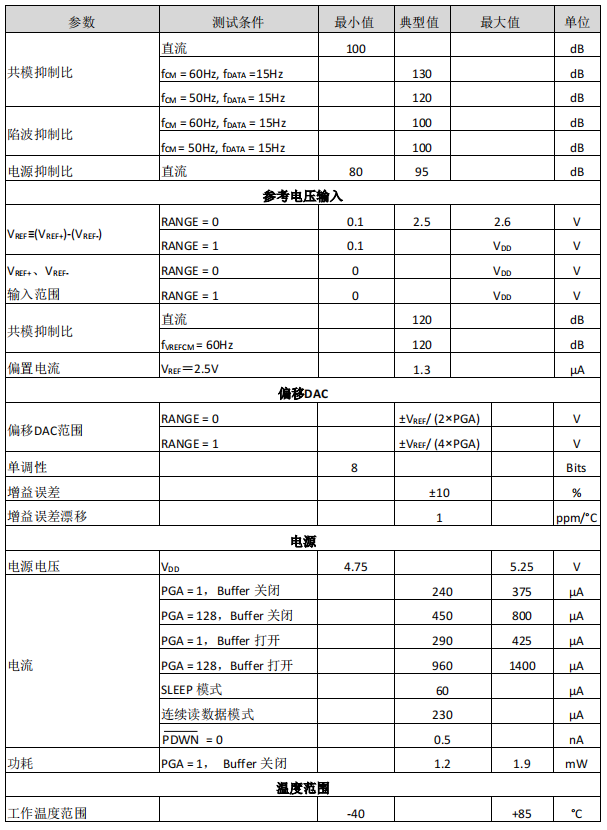

电气参数

数字特性:TMIN到 TMAX,VDD= 2.7V 到 5.25V。

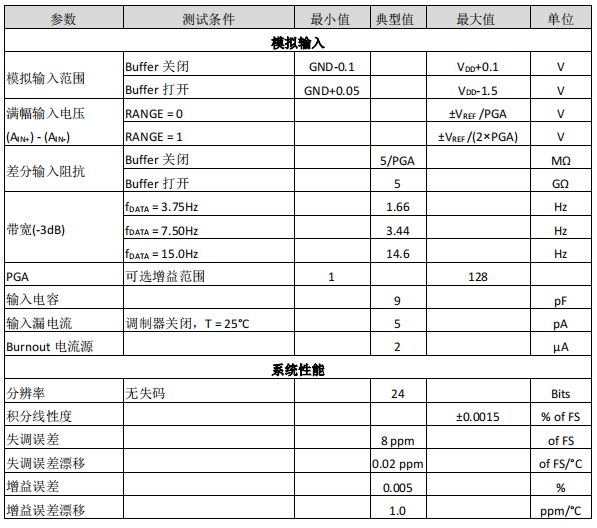

电学特性:TMIN到 TMAX,VDD=+5V,fMOD=19.2kHz,PGA=1,打开 Buffer,

fDATA=15Hz,VREF≡ (VREF+)–(VREF–)= +2.5V。

如有需求请联系——三亚微科技 王子文(16620966594)

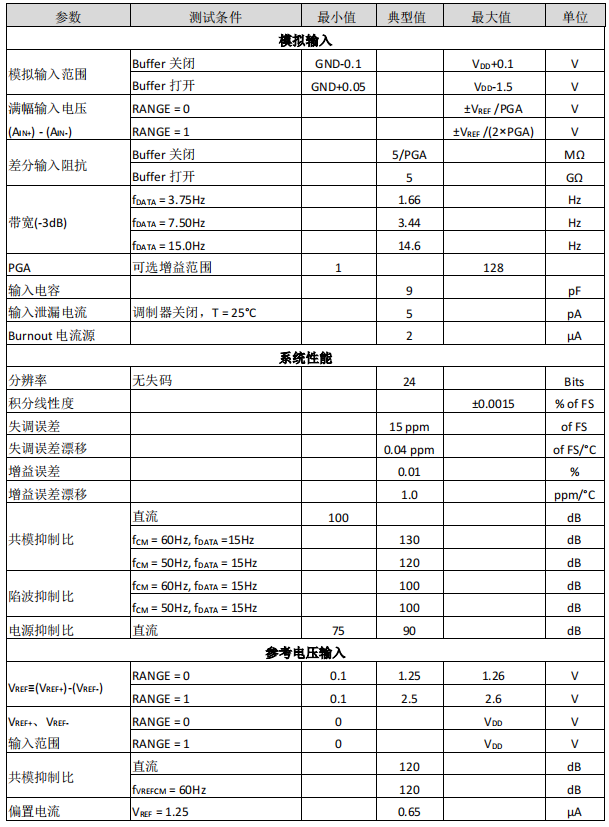

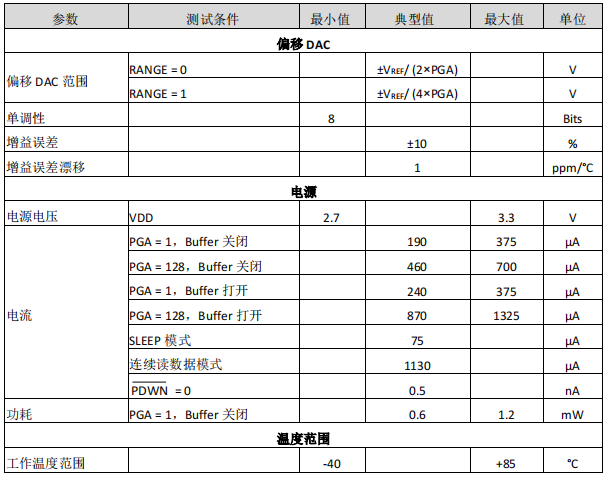

电学特性:TMINto TMAX, VDD= +3V, fMOD= 19.2kHz, PGA = 1, Buffer ON,

fDATA= 15Hz,VREF≡(VREF+)-(VREF-)= +1.25V。

功能描述

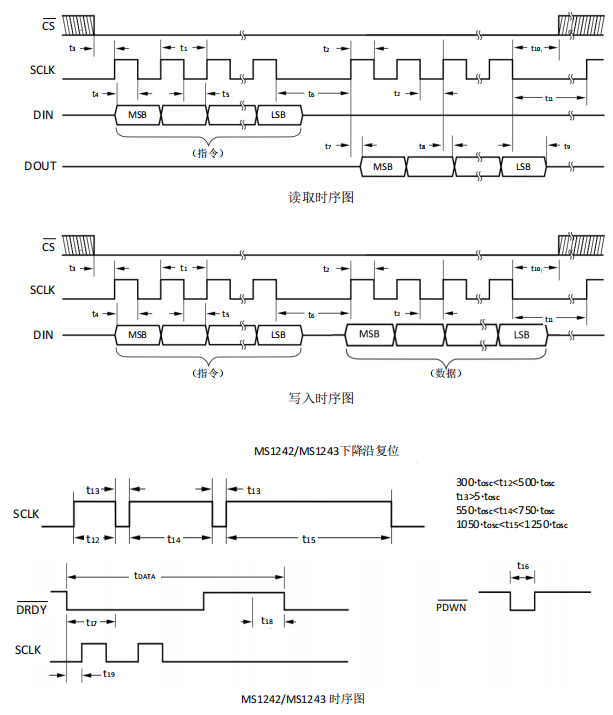

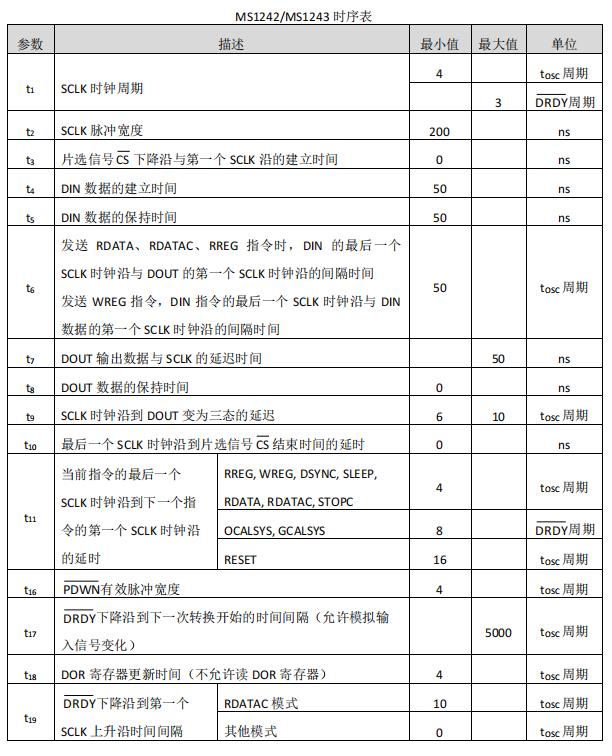

1. 时序图

如有需求请联系——三亚微科技 王子文(16620966594)

2. 模块描述

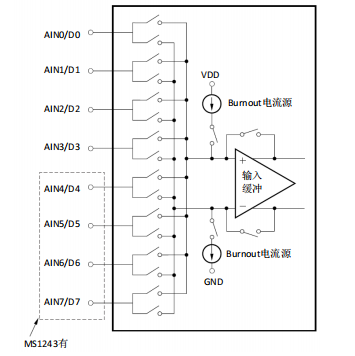

2.1 输入多路信号选择器(Input Multiplexer)

MS1242 的输入信号通道可以任意组合,多路输入选择原理图如下图所示。

MS1242 可以最多配置 2 对差分输入或 3 个单端输入,MS1243 可以最多配置 4 对差分输入或 7 个

单端输入。例如,如果选择 AIN1 为差分正(负)信号的一个输入端,可以选择任意其它输入端为负

(正)端输入。

MS1242 可以实现在单时钟周期内完成输入信号的选择切换、内部数字滤波器的稳定输出。为了降

低切换误差,要求在 DRDY 信号变低后立即配置 MUX 寄存器,允许操作时间参见时序图 t

17。

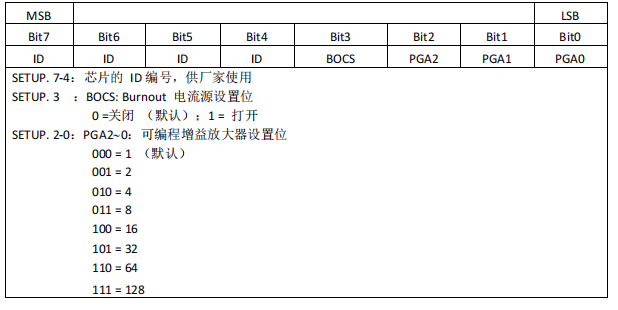

2.2 Burnout 电流源

Burnout 电流源用来检测输入传感器短路或开路,其打开或关闭是通过内部寄存器位(BOCS)来设置

的,其电流大小为 2μA,当输入传感器处于短路时,Burnout 电流源使得 MS1242 输出近似为 0;当输

入传感器处于开路时,Burnout 电流源使得 MS1242 输出近似为满幅状态。

2.3 输入缓冲器(Buffer)

在没有使能模拟输入缓冲器(Buffer)时,输入阻抗约 5MΩ/PGA。当系统要求较高的输入阻抗时,可

以使能模拟输入缓冲器,此时可以将输入阻抗提高约到 5GΩ。

缓冲器的使能信号可以由内部寄存器 ACR 控制。当 ACR 寄存器的 BUF 为高时,输入缓冲器使

能,有效提高输入阻抗。如果使能缓冲器,芯片增加额外的功耗。消耗功率的大小与 PGA 的增益有

关,PGA=1 时,增加约 50μA 电流,而 PGA=128 时,增加的电流则达 150μA。当开启缓冲器后,对输

入信号的范围有所要求,此时输入信号的范围为 AGND+0.3V AVDD-1.5V。

2.4 可编程增益放大器(PGA)

内部的电压增益放大器可以配置为 1,2,4,8,16,32,64,128。通过使用 PGA 可以提高有效转换精度。

2.5 偏移 DAC

为了扩展输入范围,MS1242 内部集成了一个偏移 8bitDAC。偏移 DAC 是一个可编程电压源,输入

信号被 PGA 放大后,和偏移 DAC 输出电压相加,输入到∆-Σ 调制器中。

2.6 调制器(Modulator)

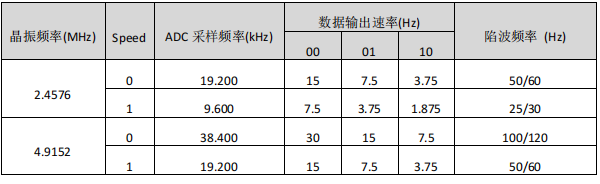

MS1242 的调制器是单环、2 阶∆-Σ 调制器,调制器的采样频率可以通过 SPEED(ACR 寄存器的 bit 5)

控制,具体如下表所示:

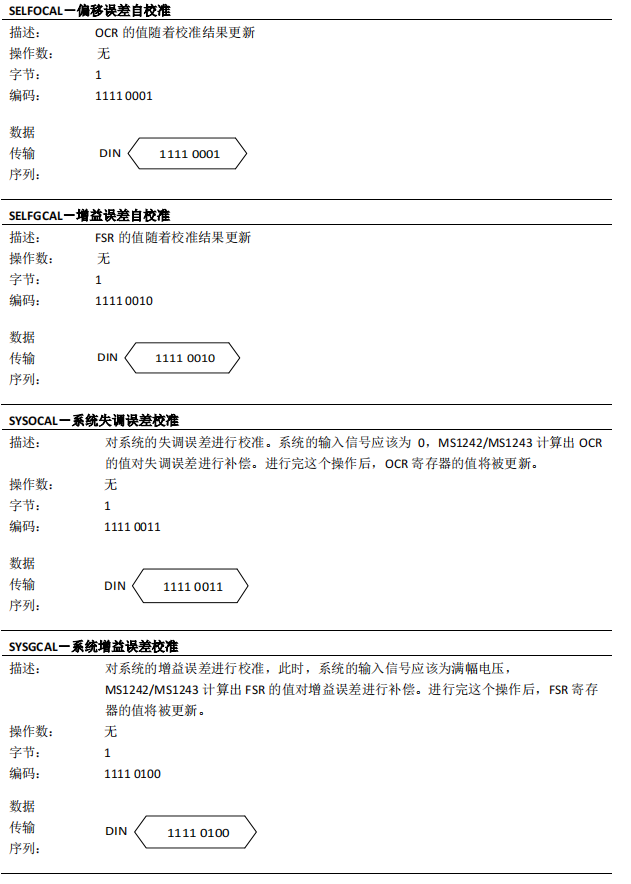

2.7 校准(Calibration)

MS1242 校准包括内部校准和系统校准,校准包括偏移误差校准、增益误差校准。

内部校准是通过内部校准命令:偏移和增益误差自校准(SELFCAL)、增益误差自校准(SELFGAL)、偏

移误差自校准(SELFOCAL)。每个校准占用两个数据转换周期。在校准期间,ADC 关断外部输入端口,

在 SELFCAL 和 SELFGAL 期间 PGA 必须设置为 1。当输入参考电压大于 VDD-1.5V 时,必须关断输入缓冲

器。

系统校准可以校准系统的偏移误差和增益误差,校准必须要求输入正确的输入信号后进行。系统

偏移误差校准(SYSOCAL) 要求输入零差分电压,芯片计算出系统的偏移误差值并写入 OCR 寄存器中,

在正常转换时予以抵消。系统增益误差校准(SYSGCAL) 要求输入正满幅度电压,芯片计算出系统的增

益误差并写入 FSR 寄存器中,在正常转换时予以抵消。每个校准占用两个数据转换周期。

在芯片重新上电、外部环境温度改变、增益(PGA)改变后必须进行误差校准,以保证模数转换的正

确。在校准期间,RANGE 位 (ACR bit2)必须设置成 0,且关闭偏移 DAC。完成校准后 DRDY 管脚变低。

校准完成后的第一个输出数据须舍弃。

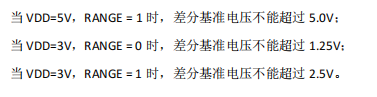

2.8 外部基准电压

MS1242 需要外接参考电压,具体值的选择通过内部 ACR 寄存器配置。参考电压接在 VREF+与

REF-管脚上,电压不能超过芯片的电源电压。

当 VDD=5V,RANGE = 0 时,差分基准电压不能超过 2.5V;

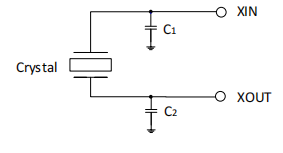

2.9 时钟产生电路(CLOCK GENERATOR)

MS1242 可以外接晶体、振荡器或时钟。如果接外部时钟,则从 XIN 管脚输入,此时 XOUT 悬空。

如果外部接晶体,电路要求如下:要求在 XIN 及 XOUT 管脚上同时接 10pF~20pF 的电容。

2.10 数字滤波器(FIR)

MS1242 带有一个可编程的 FIR 滤波器。FIR 滤波器可以被配置成不同的输出速率。当使用

2.4576M 的时钟时,MS1242 的输出数据的速率可以被配置成 15Hz、7.5Hz 或者 3.75Hz。此时,FIR 滤

波器可以同时对 50Hz 和 60Hz 的杂波信号进行陷波滤波。

若希望得到其他的输出数据速率,则须使用其他的时钟频率。此时,陷波频率也同时跟着改变。

比如,当使用默认的寄存器配置,时钟频率为 3.6864M 的时候,

输出数据的频率为: (3.6864MHz/2.4576MHz) ×15Hz = 22.5Hz

陷波频率为: (3.6864MHz/2.4576MHz ) ×(50Hz 和 60Hz) = (75Hz 和 90Hz)

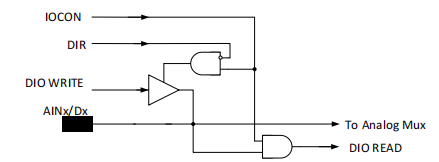

2.11 数据 I/O 接口

MS1242/MS1243 的数据接口提供双重功能:模拟输入和数据 I/O。此端口的配置通过内部

IOCON、DIR、DIO 寄存器设置。上电默认配置为模拟输入。下图是输入端口的等效电路:

2.12 串行总线接口( SPI )

MS1242/MS1243 通过 SPI 总线与外部的控制器进行通讯。MS1242/MS1243 只能用于从模式。总线

接口是标准的四线 SPI 总线,包括 CS 、SCLK、 DIN 和 DOUT。

2.12.1 片选信号( CS )

在与 MS1242/MS1243 进行通讯前,外部的控制器必须先发出 CS 片选信号。在整个通讯期间, CS

信号必须维持为低。当 CS 信号变高后,整个 SPI 总线会被复位。 CS 信号也可以被接为常低。

2.12.2 串行时钟(SCLK)

SCLK 内置施密特触发器。如果在 3 个 DRDY 周期内都没有出现 SCLK 时钟,那么在下一个 SCLK 来

临时,SPI 总线将被复位,进而开始下一个通讯周期。SCLK 上的一个特定的波形可以复位整个芯片。

2.12.3 数据输入(DIN)和数据输出(DOUT)

DIN 和 DOUT 引脚分别用来输入和输出数据。在未使用时,DOUT 为高阻态,允许将 DIN 和 DOUT

接在一起然后通过一个双向的总线来驱动它。需要注意的是,这种情况下不适合向 MS1242/MS1243 发

出 RDATAC 指令。因为 RDATAC 指令需要用 STOPC 指令或者 RESET 指令来终止。而在 RDATAC 模式

下,这条双向总线会一直被 DOUT 占用向外部发送数据,所以就无法通过总线向 MS1242/MS1243 发送

STOPC 指令或者 RESET 指令,就无法终止 RDATAC 状态。如果 DOUT 发送的数据中形成 STOPC 或者

RESET 指令,此时 DIN 会检测到 STOPC 或者 RESET 指令,从而终止 RDATAC 状态或复位芯片。

2.13 数据准备就绪 ( DRDY )

DRDY 信号表示内部数据寄存器的状态。当内部数据寄存器 DOR 内新的数据准备就绪时, DRDY

信号会变低。当执行完 DOR 的读操作后, DRDY 信号变高。在 DOR 寄存器的数据准备更新时 DRDY 信

号也会变高,表示此时 DOR 寄存器内的数据不可用,防止在 DOR 寄存器进行更新时从 DOR 寄存器内

读取数据,参见时序图 t18。

DRDY 信号也可以从 ACR 寄存器的 bit 7 来获得。

2.14 数据同步(DSYNC)

MS1242/MS1243 可以通过 DSYNC 指令来进行数据同步。当使用 DSYNC 指令进行数据同步时,数

字滤波器在 DSYNC 指令的最后一个 SCLK 时钟的边沿被复位,同时调制器也将处于复位状态。在

DSYNC 后的第一个 SCLK 内的系统时钟的上升沿,重新开始转换。

2.15 上电速率(Supply Voltage Ramp Rate)

MS1242/MS1243 的上电电路可兼容数字电源低到 1V/10ms 的上电速率,为了确保正常工作,电源

电压应单调上升。

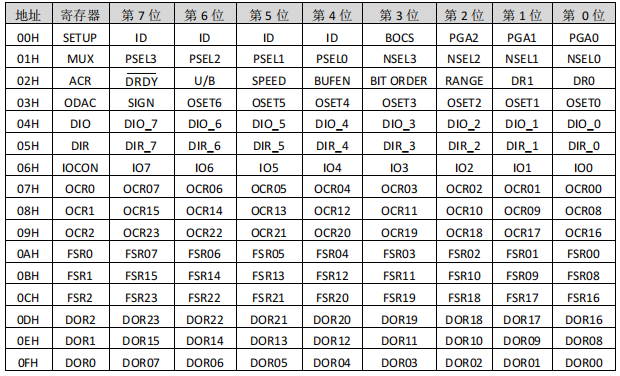

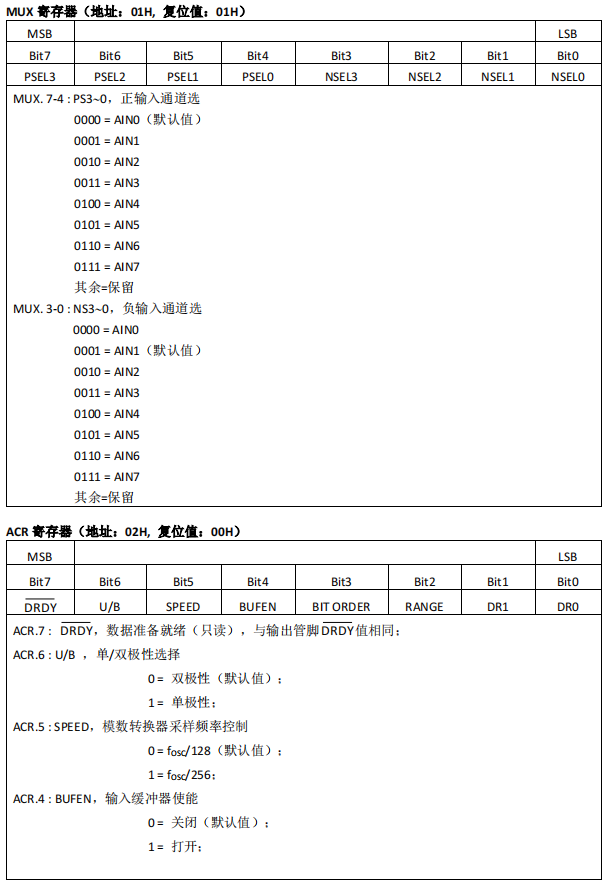

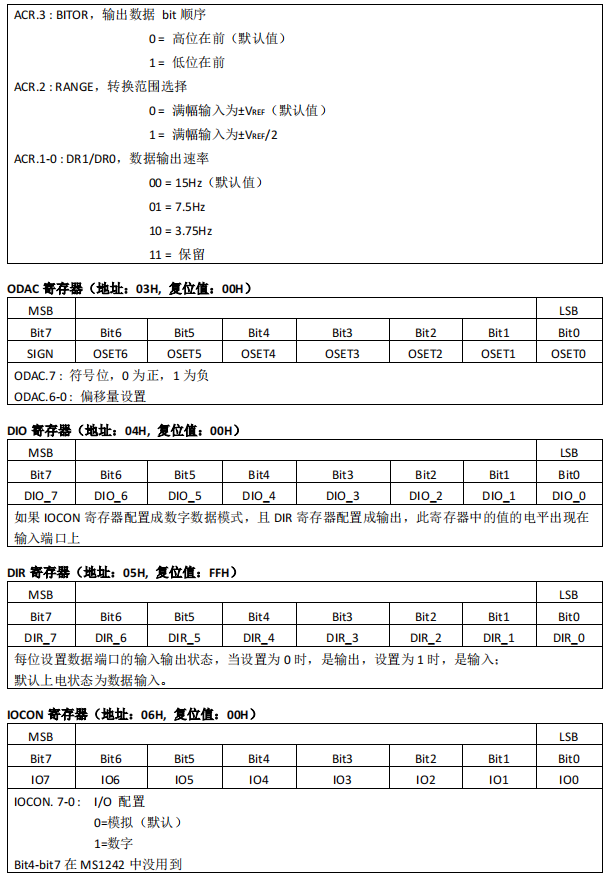

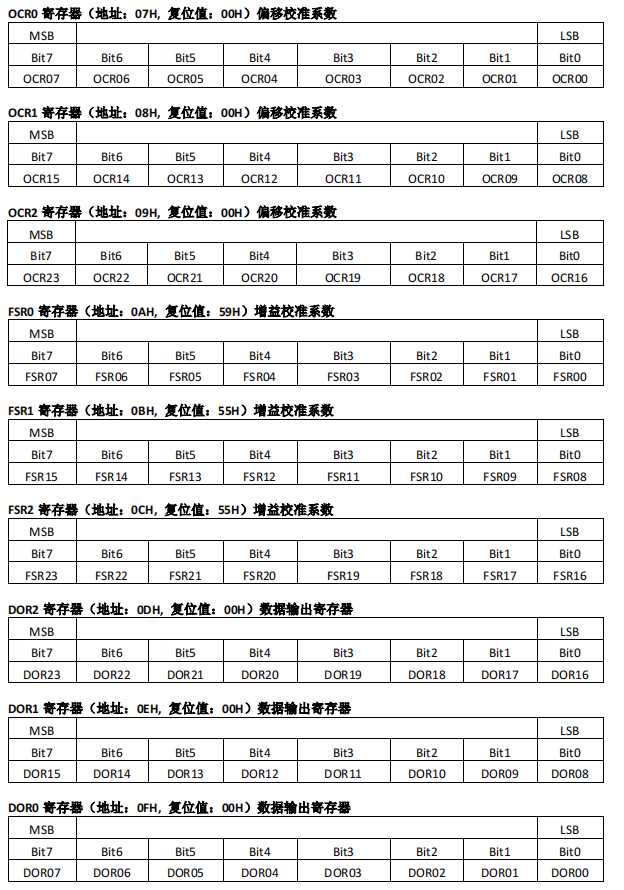

3. 寄存器描述

MS1242/MS1243 通过控制寄存器来配置工作方式。

3.1 寄存器列表

MS1242/MS1243 内部寄存器详细列表如下表所示:

3.2 寄存器详细描述

SETUP 寄存器(地址:00H, 复位值:X0H)

如有需求请联系——三亚微科技王子文(16620966594)

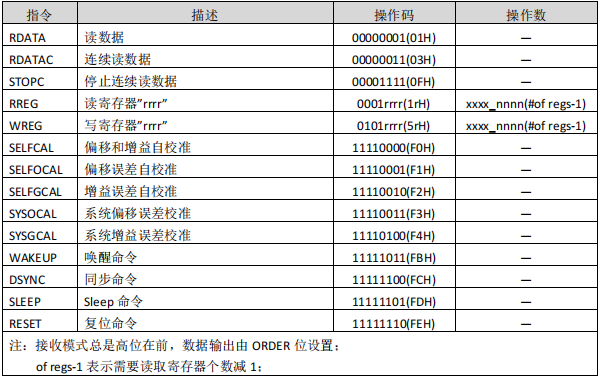

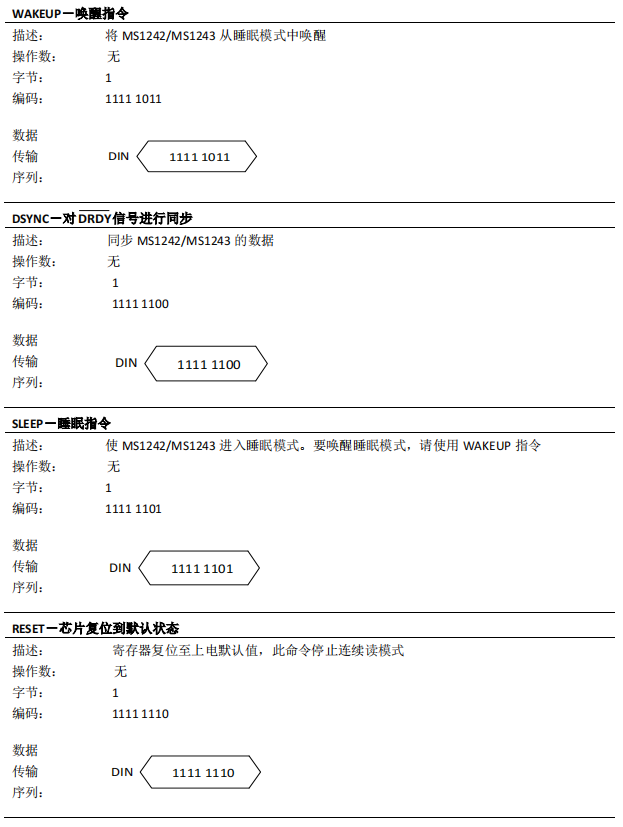

4. MS1242/MS1243 指令描述

MS1242/MS1243 使用了一系列指令,这些指令中有些是单条的(比如 RESET),有些则需要另外

的操作数(比如 WREG 等)。

操作数:

n = 数量 ( 0 到 127 )

r = 寄存器 ( 0 到 15 )

x = 任意值

指令列表

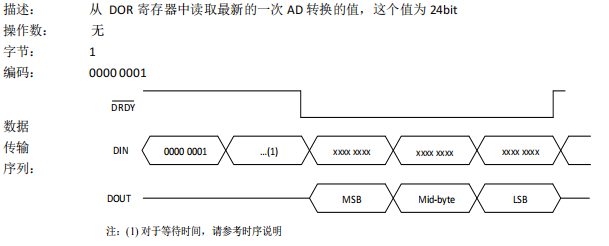

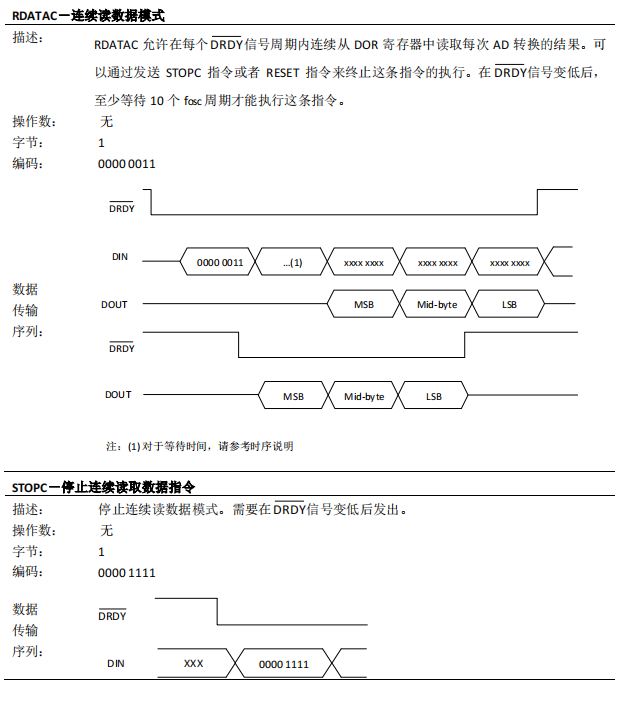

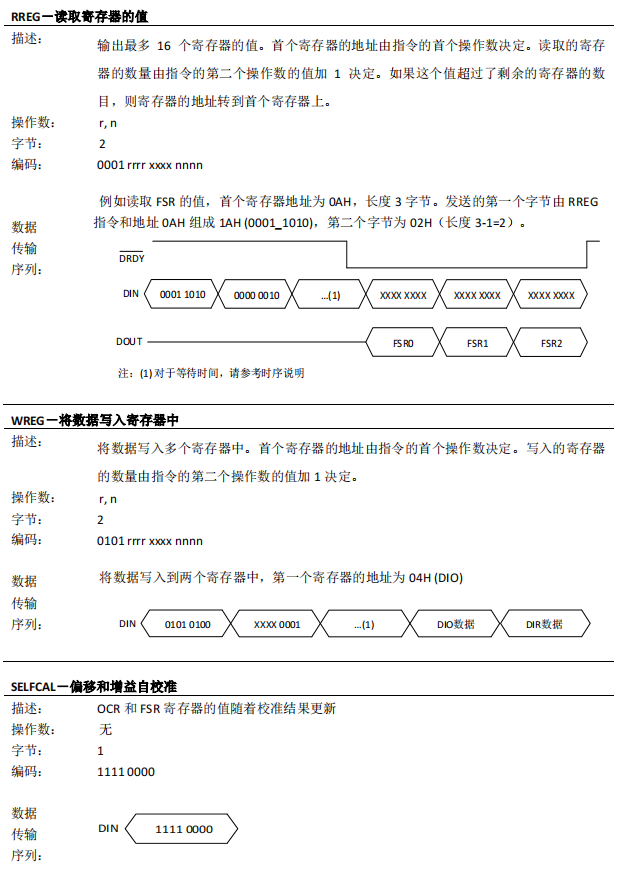

RDATA-读数据模式

如有需求请联系——三亚微科技王子文(16620966594)

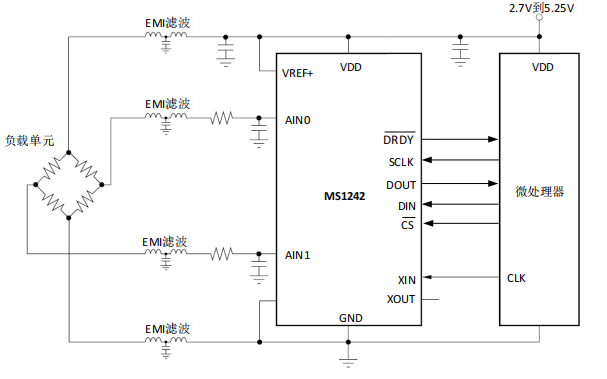

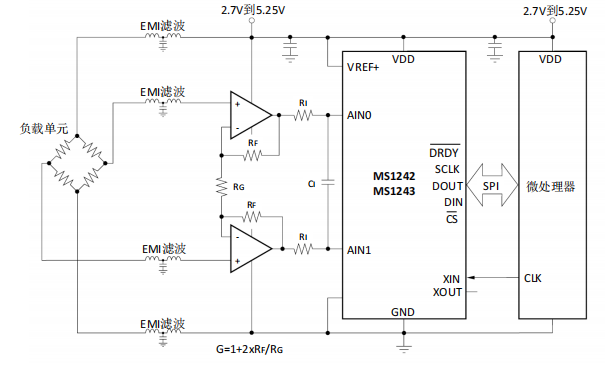

典型应用图

下图是 MS1242 在普通精度重量计的典型应用图:

下图是 MS1242/MS1243 在高精度重量计的典型应用图:

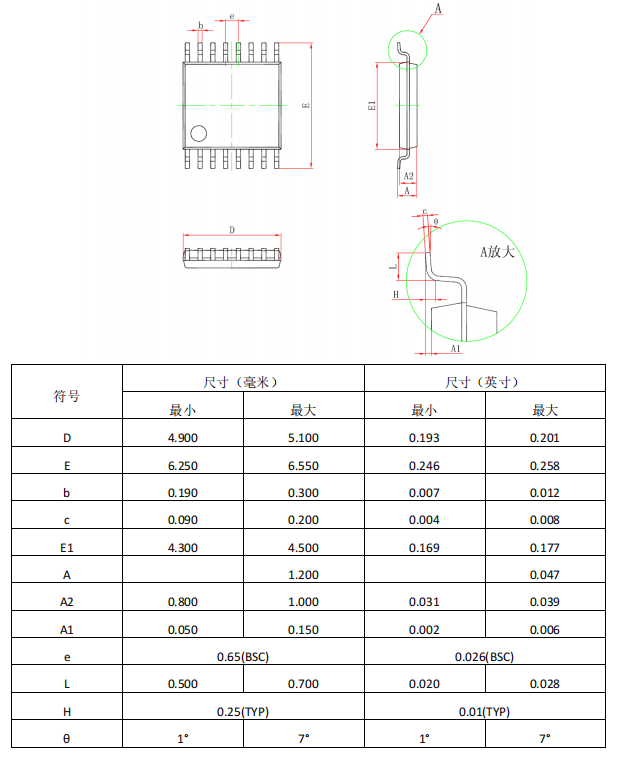

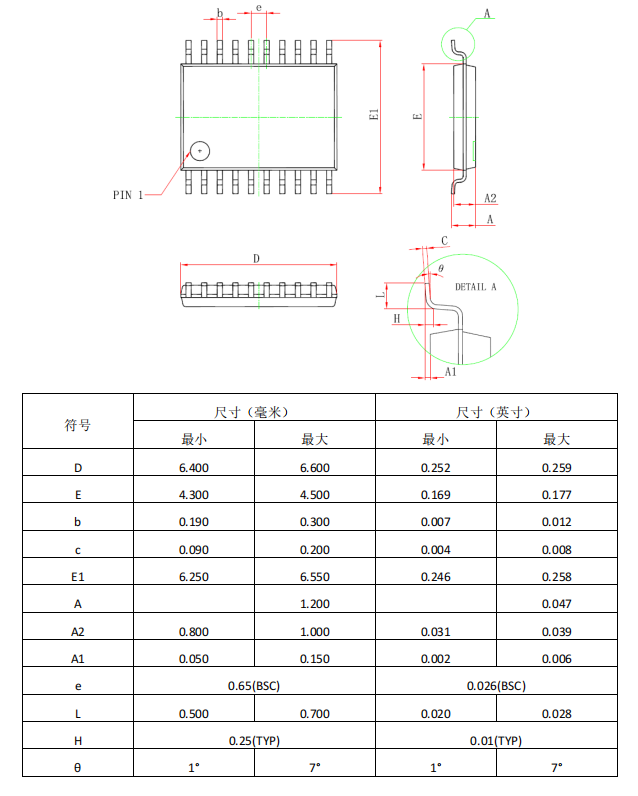

封装外形图

TSSOP16

TSSOP20

审核编辑 黄宇

——爱研究芯片的小王

-

MS5198T/MS5199T——低噪声、低功耗、16/24 位 ∑-Δ ADC2024-11-13 2991

-

MS1242,替代ADS1242,24bit 高精度、低功耗模数转换器2024-02-19 6334

-

24bit 模数转换器MS5148T2023-06-01 1243

-

瑞盟24bit模数转换器MS5180T中文手册2023-02-13 582

-

瑞盟16bit/24bit模数转换器MS5196T/MS5197T,兼容AD7796/AD77972023-01-10 857

-

国产16bit/24bit模数转换器MS5196T/MS5197T的应用及特点2023-01-06 1341

-

MS1243 完美替代AD12432022-11-07 1424

-

MS5198T模数转换器概述、特点及应用2022-07-20 1914

-

MS5195模数转换器概述、特点及应用2022-07-19 2632

-

MS5193T模数转换器2022-07-18 2055

-

MS1242/MS1243模数转换芯片的特点及应用2022-06-23 5858

-

国产24bit高精度、低功耗模数转换器MS1242/MS12432021-06-28 2300

全部0条评论

快来发表一下你的评论吧 !