浅谈Verilog设计模拟电路 数字和模拟纠葛

模拟技术

描述

随着可综合模拟电路设计的出现,数字电路性能越来越强,模拟电路却由于电源电压的下降而导致设计更加困难。有时候但你学习电路的时候你会傻傻的分不清模拟电路和数字电路。

1.模拟与数字合体,结果是?

模拟电路和数字电路是对电路的经典分类。数字电路处理离散的数字信号,模拟电路处理连续的模拟信号。在经典的课本里,模拟电路和数字电路设计与分析的方法论都有很大区别,模拟电路的分析像物理,设计则像一门艺术;数字电路的分析像数学,而设计起来是一板一眼,基于严密的逻辑流程。

然而,模拟和数字之间的间隔并非不可打破。一方面,信号的本质是连续的,一切数字电路只是模拟电路的一种特例,甚至可以把数字电路用在模拟电路中(例如反相器也可以当作一个放大器用,而且是电流复用的那种J);另一方面,利用数字电路可扩展性好,可控性好等特性,我们可以把一些传统在模拟域处理的信号搬到数字域处理并获得很好的结果。模拟和数字合体的结果并不仅仅是混合信号电路,而是一种全新的设计理念。

模拟和数字融合可以分成两种方向,即使用数字方法实现传统的模拟电路(数字-模拟),以及使用模拟方法实现传统的数字电路(模拟-数字)。本期我们主要介绍数字-模拟电路。

2.数字-模拟

随着半导体技术的发展,越来越多人正在探索把原来模拟域处理的信号搬到数字域处理。这不仅仅是标新立异,而且是由半导体技术发展的趋势决定的。所以啊,一个电路的命运不知要看工程师的奋斗,还要看历史进程。

那么,半导体技术如何让数字技术入侵模拟电路呢?大家都知道,随着半导体制程的发展,器件特征尺寸变小,器件速度变快,这对于数字电路和模拟电路都是件好事,皆大欢喜。然而,特征尺寸变小是要付出相应代价的。代价第一就是随着MOSFET栅极氧化层变薄,器件击穿电压降低,因此电源电压也随之降低。这对于数字电路来说对性能影响会被栅电容变小期间速度变快而抵消因此不是太大的问题,但对于模拟电路来说问题可就大了。首先,模拟电路的首要指标是信噪比,降低电压意味着信号摆幅降低,但是噪声不会与电源电压同步降低,因此低电压对于信噪比存在不利影响。其次,器件的阈值电压因为漏电的关系也不会与电源电压同步降低,这就让传统cascode等模拟工程师喜闻乐见的电路结构在低电压下无法再使用。最后,因为阈值电压与电源电压没有同步降低,因此在低电源电压下器件的工作范围更接近于亚阈值区,因此模拟电路的线性度变差了

除了电源电压降低带来的诸多问题以外,先进半导体制程的单位面积价格很高,但是模拟电路的整体尺寸并不随着特征尺寸缩小而等比例缩小(尤其是无源器件例如电感,其大小与特征尺寸根本就没关系),因此在先进半导体制程下模拟电路的成本其实是升高了。

与模拟电路相反,特征尺寸缩小对于数字电路性能有益无害(除了漏电流增加,但是这个可以说不算性能:)),因此用数字电路尽量代替模拟电路才能真正享受半导体工艺进化带来的益处。

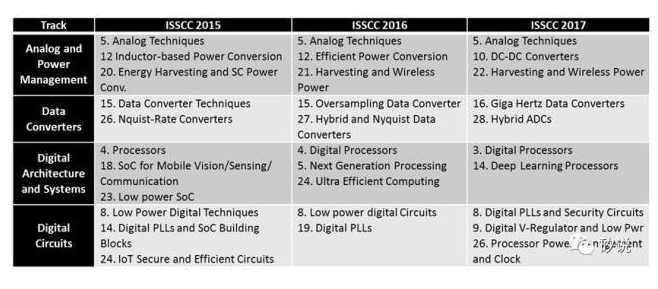

从近三年年ISSCC的track比较也能看出数字慢慢进入模拟领域代替经典模拟电路的趋势。在ISSCC 10个大track中,模拟track包括传统模拟电路与功耗管理(Analog),模数转换器(Data Converters)。数字track包括架构与系统(Digital Arch and Sys),和数字电路(Digital Circuits)。 然而,在下面的列表中,也有“Digital PLL”,“Digital V-Regulator and Low Pwr”这样有趣的session。

下面我们介绍几类典型的数字-模拟电路。

All-Digital PLL

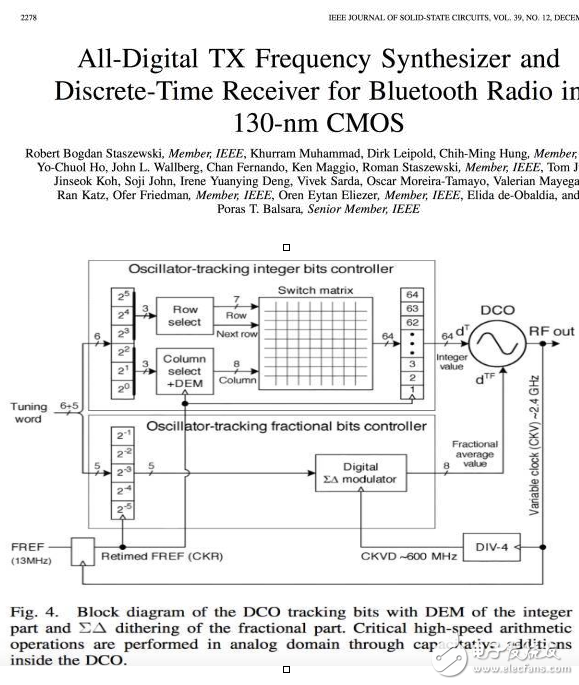

十几年前,所有的PLL工程师应该都自我认定为模拟工程师吧,直到本世纪初R. Staszewski(当时在TI,现在在University College Dublin当教授)惊世骇俗的一篇All-Digital Frenquency Synthesizer横空出世。

传统的模拟PLL中,振荡器的相位信息被转化成模拟电压信号,这个电压信号经过一系列反馈环路信号处理后,成为压控振荡器(VCO)的控制信号。全数字锁相环(ADPLL)的思路则是首先设计了一个数控振荡器(DCO),由数字信号控制varactor以及capacitor bank以控制振荡频率,虽然DCO的振荡频率是离散的,但是通过sigma-delta调制理论上可以近似范围内的任何频率。在DCO设计完成之后,ADPLL中又进一步在反馈环路中把相位转化为数字信号而不是模拟电压信号,并且把这个数字信号在数字域经过类似处理后去控制DCO。想象一下,之前模拟PLL的滤波器往往需要用到巨大的片外电容/电感,而使用ADPLL的话这一切都可以用一个片上数字滤波器搞定,这是多美好的一件事情!除了滤波器之外,ADPLL还有容易完成相位调制等等其他优势。如今,digital PLL已经是固态电路领域的一个稳定session。而且,各大芯片公司的通信产品中也已经商用了数字化的PLL技术(我还在复旦的时候Staszewski来做过讲座,在讲座中自豪地说他去买手机一眼就认出了许多用了ADPLL的型号。后来TI退出了手机芯片领域,甚至Staszewski所在的部门都被关掉了于是去了学界,这就是另一个故事了)。

Digital LDO

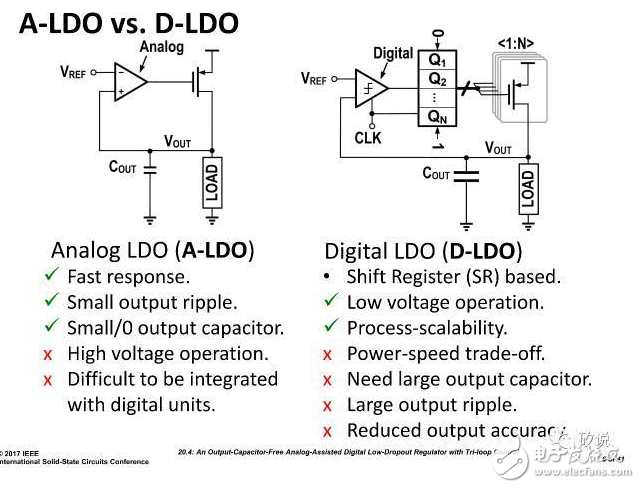

除了PLL以外,模拟转向数字的过程,正在另一传统模拟电路的领域重复着历史——LDO。

所谓数字LDO,就是在沿袭传统模拟LDO的基础上,沿袭负反馈的精神,但采用比较器和数字控制逻辑实现输出电压的稳定性。传统的数字做法基于单比特比较和Barrier Shifter,建立精度低,且输出的纹波/噪声大。但是,随着模数转换技术和数字控制理论/实现的发展,数字LDO的缺点在逐渐被克服。

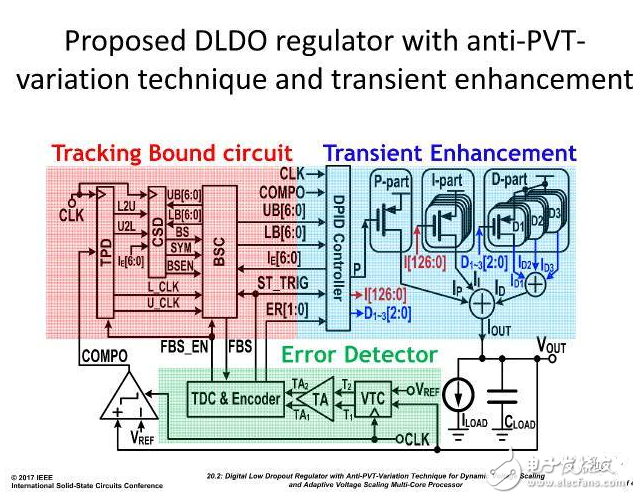

***交通大学提出了基于TDC的高精度误差检测反馈回路,避免了以barrier shifter实现的传统电路电路大抖动。并且在数字控制的部分,完整的提供了数字话PID解决方案,实现静态建立的补偿与加强。

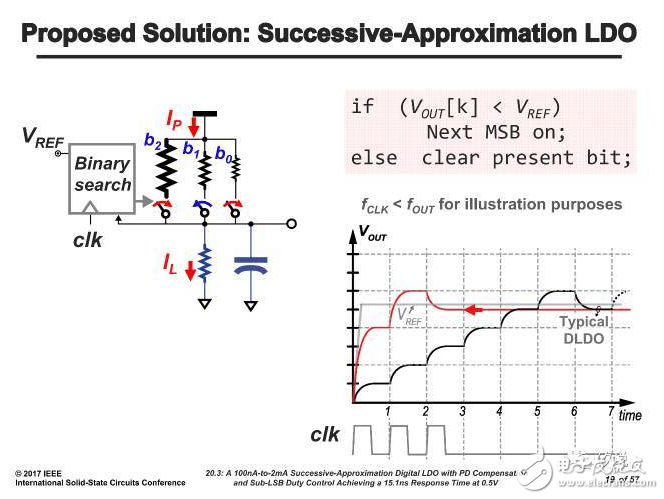

UCSD的数字LDO将整个LDO建立融入到一个逐次比较模数转换的过程中,缩短了传统仅基于极性搜索关键路径,利用二进制搜索提高了DLDO的瞬时响应,并在此基础上作了稳定性分析。

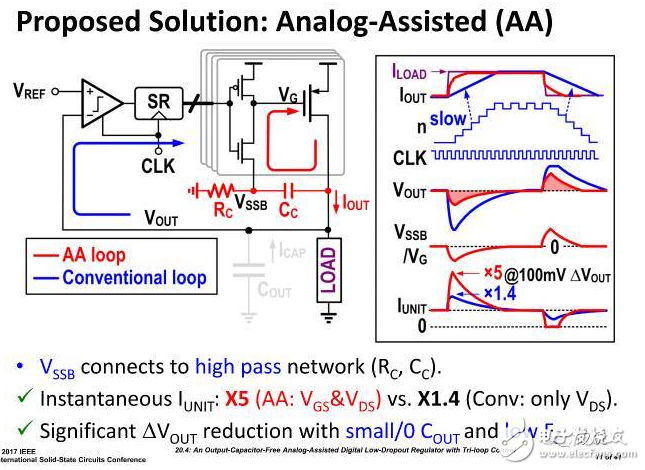

澳门大学/华南理工大学提出的模拟辅助DLDO,巧妙地采用了一个避免了没有大电容下退藕下的补偿原理。仅仅采用了一组电容/电阻,实现了一个快速反馈路径。

Digital Opamp

每个学EE的人都有过被模拟电子学/Circuits 101这样的课摧残的经历,运算放大器早已成为了各位心中模拟电路的代名词。运放怎么能和数字电路混在一起呢?但近年来,随着inverter based的opamp逐渐走向成熟,各种对运放的新思路层出不穷。现今看来,把运放定义为模拟恐怕已经是上个时代的故事了。

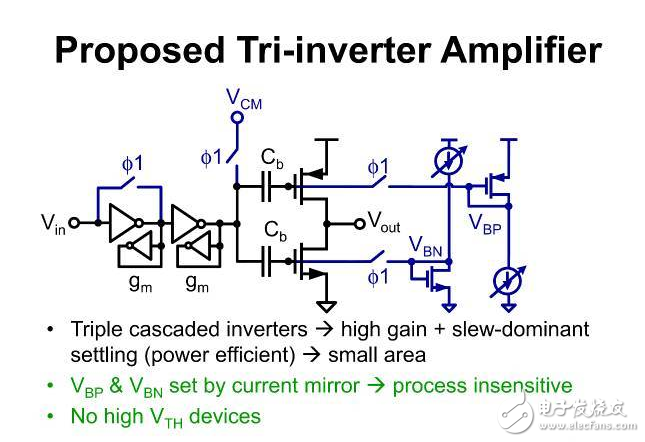

首先我们来看Stanford大学研发的超声成像系统中的采用的一个运算放大器。该放大器集成了目前主流的各类数字化设计的运放技术,前两级为级联反相器,第三级是由动态偏置的Class AB级,像三个级联的反相器。当该放大器以负反馈方式链接后,该反相器可以实现ring-amplifier(由俄勒冈州立大学与密歇根大学在前两年ISSCC提出)。

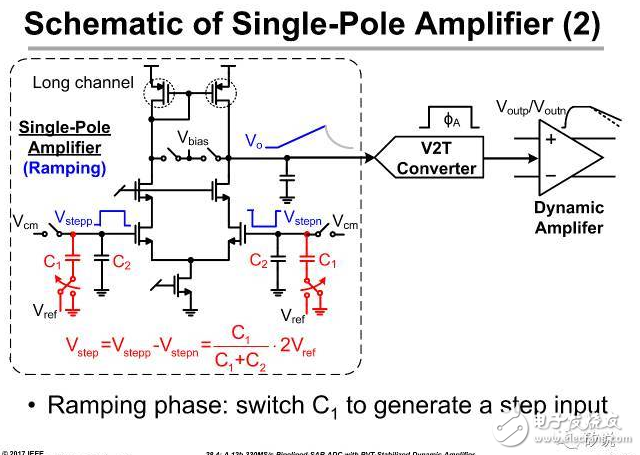

还有类似充放电模型的“积分型”动态放大器,在联发科(Mediatek)的一篇噪声整形/逐次比较(Noise-Shaping SAR ADC)中提到了如下结构,

通过合理选择充电/放电路径,单级放大器的输出电平受到输入电压的调制而产生差异,由此实现信号放大。很明显的,该放大倍数对许多电路加工参数敏感(PVT sensitive)。由此,UT Dallas的研究者针对这一问题,提出了跟踪PVT因素的建立时间产生电路:

该产生电路通过类似replica的想法仿造出一个脉冲信号,该信号的脉冲宽度接跟随PVT变化而变化,由此实现稳定的动态放大器。

Synthesizable All-Digital PLL/RF Transmitter

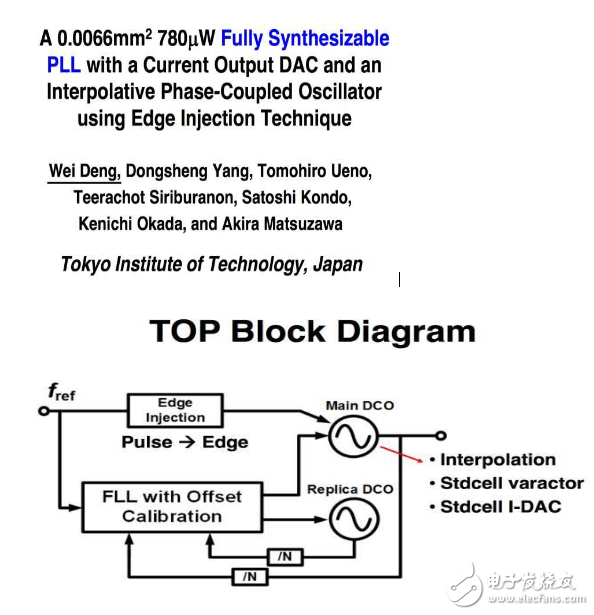

前面的全数字电路虽然使用了数字信号,但是其设计流程还是走的是传统定制电路的路子,类似当年在设计8086的时候数字门电路还是要手动设计一样。那么,有没有真的用数字电路流程,用标准单元库综合的办法实现的模拟电路呢?这个在目前也已经实现了,例如,来自Tokyo Institute of Technology的Wei Deng在过去的几年里连续发表了多篇可综合PLL的论文,证明了其可行性。

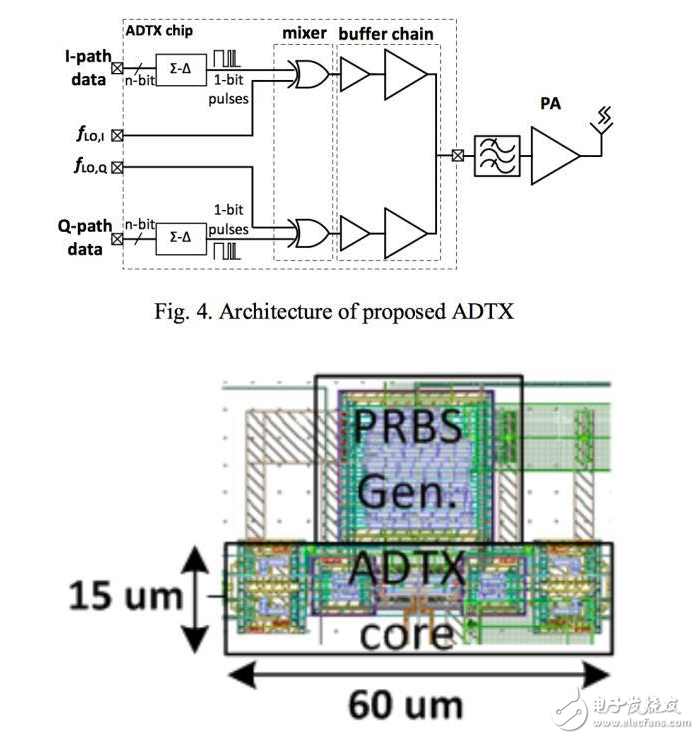

除此之外,今年TCAD上也有一篇论文“A Novel Fully Synthesizable All-Digital RF Transmitter for IoT Applications”,实现了可综合全数字射频发射机。该电路使用了全数字sigma-delta modulator调制I/Q幅度,使用XOR门作为混频器,并且在全数字driver amplifier的输出端把I/Q合并到了一起。这个TX通过Verilog描述并使用数字流程综合/布局布线,未来写code设计模拟电路的日子可能真的不遥远了。

-

Verilog-A的模拟电路行为模型及仿真2009-11-21 794

-

模拟电路和数字电路合集2016-07-25 1007

-

模拟电路偷走了数字电路的魔力2016-09-20 595

-

模拟电路和数字电路学习笔记2016-09-20 878

-

模拟电路和数字电路的学习笔记2016-09-20 754

-

电路设计中的模拟地与数字地2016-10-10 1179

-

模拟电路与数字电路的区别详解2017-05-23 7509

-

什么是模拟电路 什么是数字电路2018-10-16 100911

-

数字电路和模拟电路的区别2019-05-10 37682

-

简析模拟电路与数字电路2019-07-03 9956

-

与模拟电路比数字电路的优点2024-01-24 1746

-

模拟电路和数字电路的概念是什么2024-08-22 1216

-

数字地和模拟地如何处理2024-09-06 809

-

pcb数字地和模拟地怎么隔离2024-09-06 2211

全部0条评论

快来发表一下你的评论吧 !