基于FPGA的实时视频图像采集处理系统

FPGA/ASIC技术

描述

随着社会的不断发展,视频图像采集处理技术在许多行业领域中扮演着非常重要的角色,如军事、安全监控、工业视觉等领域,而各行各业对于视频图像采集和处理技术的要求也越来越高。高速、实时性是主要发展趋势之一。目前,视频图像采集与处理技术的发展主要分为两类:一是基于PC在相关特定的PCIe采集板卡的基础上,通过软件对视频图像进行处理;二是利用相关的集成硬件如DSP、MCU、FPGA等对视频图像进行采集处理[1]。相对来讲后者的处理效果不如前者,但实时性好、体积小、方便使用,更适合于工业的需求。

FPGA现场可编程逻辑门列,采用并行运算模式,且工作频率较高,可对大量数据进行实时操作与处理,在通信领域、图像处理等方面上优势明显[2]。因此,本设计选用FPGA作为系统的控制和数据处理中心。

1 系统总体概述

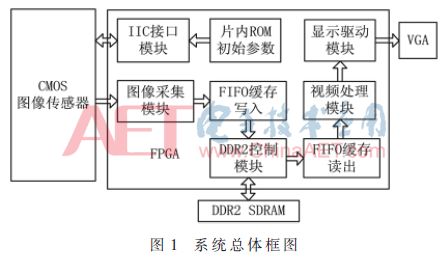

基于FPGA的视频采集处理系统可分为:视频采集模块、图像存储模块、数据处理模块和图像显示模块。工作过程为:首先,FPGA通过IIC总线协议对摄像头进行初始化配置,摄像头对焦工作拍摄采集图像,然后,采集的视频数据通过FIFO缓存器不断写入到DDR2 SDRAM中存储,再经过FIFO缓存器读出视频数据,接着,选择性对读出的视频图像数据进行处理,最后在VGA上显示视频图像。系统的总体框图如图1所示。

2 中央控制单元

2.1 FPGA

从FPGA硬件开发的角度考虑,利用EDA开发软件和硬件描述语言Verilog编程,对FPGA芯片进行开发,得到其工程要求的硬件功能。对比传统的硬件设计开发,减少了器件的浪费和多次焊接的工作量,设计过程也更加灵活、方便、高效。

另外,FPGA要实现对每个模块的控制和处理,除并行数据处理优点外,自身必须拥有较多I/O口,丰富的逻辑单元等。鉴于此,选用了Alter公司研发的Cyclone IV系列的EP4CE617C8。此款FPGA拥有179个I/O接口,62 792个逻辑单元,392个乘法器,且功耗低。

2.2 视频图像采集模块

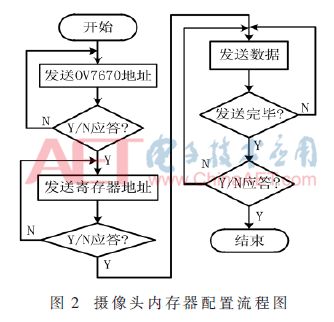

CMOS OV7670图像传感器,其体积小,工作电压小,640×380像素,可选用自带的降噪、数模转换、分频等功能,是较好的视频图像采集选择。FPGA通过IIC总线协议与CMOS摄像头进行初始化配置。IIC总线写入前,CMOS摄像头的SCLK和SDAT引脚必须带上拉电阻。IIC总线写入时,首先写入设备地址,CMOS的初始地址为0x42,其次写入寄存器地址,最后写入数据。其IIC总线数据写入流程如图2所示。

IIC总线与CMOS的数据通信后,配置CMOS摄像头控制寄存器。时钟配置使用外部时钟即FPGA的工作时钟频率,目的是更好地控制CMOS摄像头。PLL寄存器配置零分频、使能内部线性稳压器LDO,内部电压工作稳定。配置的Verilog部分代码分别依次为:

SET_OV7670+19 : LUT_DATA=16'h1180;

SET_OV7670:5 : LUT_DATA=16'h6b00;

其他相关控制寄存器中,配置了水平镜像、关闭彩条、视频格式RGB565等功能。保证其能在系统高速运行下采集到可靠度大、信息性强的视频图像数据。

2.3 系统存储模块

2.3.1 DDR2 SDRAM

DDR2 SDRAM作为系统存储器,选用采用1 GB内存的DDR2 800系列 SDRAM作为存储器。DDR2工作时钟频率为200 MHz[2],具有读写速度快、集成度高、存储容量大以及成本低等特点。其操作速率是普通SDRAM的4倍,能够较好地达到系统实时性的要求。

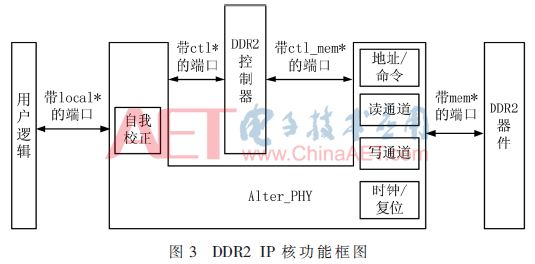

DDR2不仅能在系统时钟控制下工作,也可以独立的进行操作,如自刷新、自预充电净化等,其控制复杂[3]。因此,利用Quartus II自带的IP核构建DDR2 SDRAM控制器。同时也生成了Altera数字PHY。PHY是连接DDR2 内核控制器和外部DDR2器件的桥梁。PHY拥有四层接口,分别为带local_*类的用户逻辑接口、带mem_*类的外部DDR2芯片接口、带ctl_*和ctl_mem_*的PHY与IP控制器相互连接的接口。其功能框图如图3所示。

IP内核控制器的使用将DDR2复杂的控制操作转变成用户简单的读写时序操作,因此,DDR2存储模块可设计分为时钟、复位、初始化、控制、数据通道和仲裁等子模块。其中数据通道子模块建立了DDR2连接FIFO缓存器的通道。

2.3.2 FIFO

FIFO是一种先入先出的存储器,没有地址定义,使用简单。FIFO只能顺序读写数据,确保了数据的安全性。由此,在多数情况下作为系统数据缓冲器使用[5]。

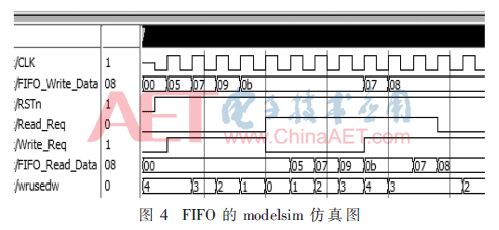

在Quartus II的内核中,建立异步FIFO的控制器。异步FIFO,即读写操作时钟信号不一致,有利于图像数据的缓冲。wrusedw信号控制着数据的读写请求。当wrusedwd等于FIFO深度值4时(为方便说明,仿真的FIFO深度为4),表示FIFO已空,Write_Req信号有效,只能写入数据。wrusedw为0,表示FIFO已满,Read_Req信号有效,只能读出数据。wrusedwd为其余值,则读、写数据请求都可执行。如图4所示。

3 视频图像处理模块

本文通过Sobel边缘检测对图像数据进行处理。边缘检测意义在于能够获取目标物体的边缘信息,有利于目标识别和追踪[6]。Sobel边缘检测算法具有计算量小、检测精度高等优点,也是最常用的图像边缘处理方法之一。

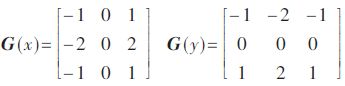

Sobel边缘检测算法过程:首先,确立Sobel算子模板,它包含了横纵向两组3×3运算算子矩阵模板。如下式:

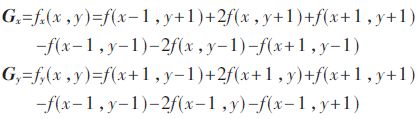

其次,利用水平和垂直方向的矩阵算子与原始图像像素点进行平面卷积分运算,算出X、Y两个方向上的一阶导数梯度值[7],如下式:

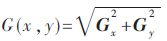

然后,把计算出的X、Y方向梯度值做平方求和后再开方,得到中心点的梯度值。如下式:

最后,中心点梯度值与设定的阈值互相比较,大于阈值的为边缘点,输出为黑色,小于阈值的为普通点,输出为白色[8-9]。

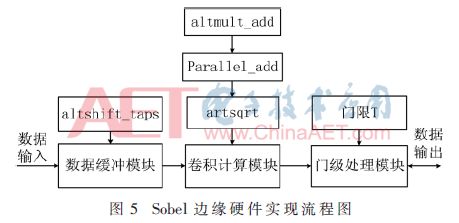

Sobel边缘检测的实现包括缓冲模块、计算卷积模块和门级处理模块。其中,缓冲模块使用基于RAM的移位寄存器altshift_taps,卷积计算模块使用6个可编程乘加器aitmult_add和2个并行加法器parallel_add计算出水平和垂直的梯度值,再通过浮点平方根altfr_sqrt得到中心点值。门级处理模块即阈值的比较[10]。原理过程如图5所示。

4 实验

完成系统硬件设计后,保存工程文件。并绘制电路原理图和PCB图。最后,制作电路板。完成所有工作后,建立系统,进行实验。

实验一:实时视频图像采集显示实验。首先,FPGA控制CMOS 7670采集图像;然后,FPGA对采集图像数据传输和存储;最后,通过VGA显示图像。其画面清晰、流畅。实验结果如图6所示。

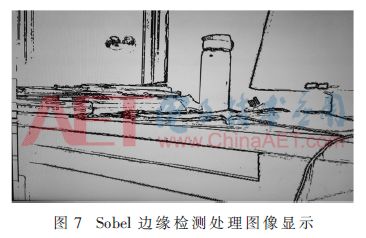

实验二:Sobel边缘检测算法处理视频图像显示实验。在实验一的基础上,增加了对图像数据的Sobel边缘检测处理,再通过VGA进行显示。图像中物体轮廓提取明显,且实时性较好。实验结果如图7所示。

5 结论

实时视频图像采集与处理技术广泛用于监控、工业视觉等领域。本系统以FPGA核心,充分利用其高速、大数据处理能力和硬件编程设计等特点,结合相关器件,实现了对视频图像的采集、处理和显示。实验结果画面清晰、流畅,效果好。同时在此基础上,增加了对物体的边缘检测,在物体追踪和识别方面也具有一定的实用意义。

-

基于HDMI的全高清实时视频采集与图像处理系统2021-06-23 1256

-

请问一下怎么设计一个基于FPGA的实时视频图像处理系统?2021-05-06 1228

-

基于FPGA的实时视频图像采集处理系统2020-05-19 1884

-

FPGA实时视频图像处理系统的原理是什么?2019-08-22 3420

-

一种基于DSP+FPGA视频图像采集处理系统的设计与实现2017-12-25 5826

-

基于FPGA的视频图像处理系统的设计2017-11-22 5486

-

实时图像采集和处理系统的设计方法2017-10-31 1537

-

基于DSP和FPGA的模块化实时图像处理系统设计2017-10-23 1334

-

基于FPGA的视频图像处理系统设计_李莲2017-03-19 1220

-

基于FPGA+DSP实时图像采集处理系统设计2017-01-03 1270

-

基于FPGA的玻璃缺陷图像采集预处理系统设计2016-08-30 716

-

基于FPGA的视频图像处理系统2015-05-23 23247

-

基于FPGA的小型微光视频图像增强处理系统2009-01-11 627

全部0条评论

快来发表一下你的评论吧 !