详解LDO电路的电源抑制比

描述

电源抑制能力

原理

电源抑制(Power Supply Rejection)能力是SoC系统中电源模块很重要的指标,在当今数字和模拟电路高度集成的趋势下,一个能提供稳定输出电压的系统模块显得尤为重要,而这个模块又很容易受到供电电源的噪声和纹波影响,电源抑制能力描述的就是对这一类影响的抑制能力。

实际电路搭建

LDO理论电路

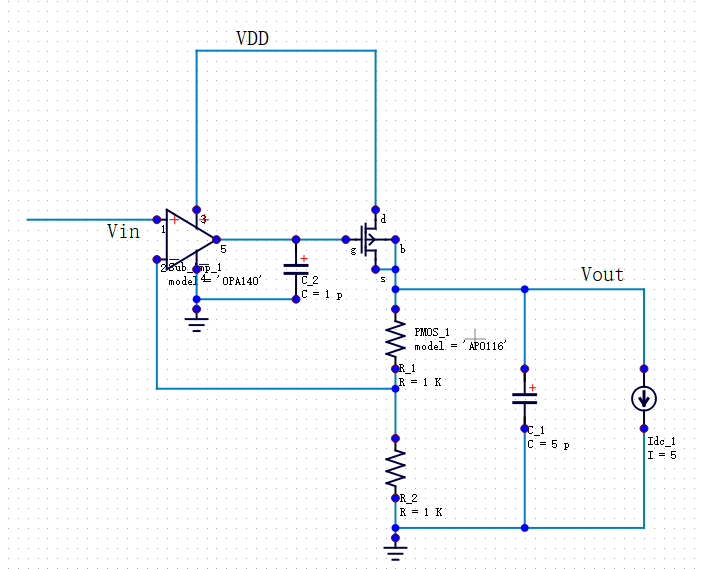

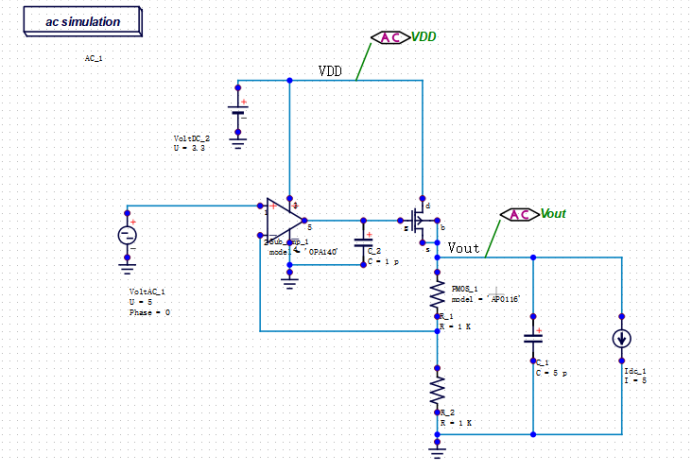

使用巨霖PowerExpert软件可以搭建一个LDO的器件结构示意图:

上图中的放大器作为误差放大器,电压从放大器输出经过一个PMOS,为电阻R_1和R_2提供电流,实现分压。假设该误差放大器跨导为 ,小信号等效电阻为

,小信号等效电阻为 ,输出电阻为

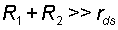

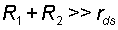

,输出电阻为 。为了保证静态功耗低,R_1和R_2取值应保证

。为了保证静态功耗低,R_1和R_2取值应保证 。上述电路图是一个LDO的结构模型,展示了LDO的基本原理,下面分析输入电压纹波对输出电压的影响。

。上述电路图是一个LDO的结构模型,展示了LDO的基本原理,下面分析输入电压纹波对输出电压的影响。

PSR分析电路

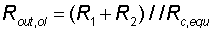

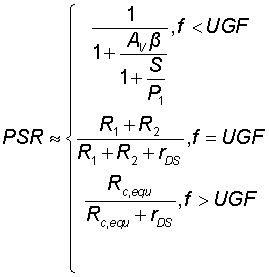

LDO在分析PSR时的等效电路可以看成,PMOS的输出电阻与总电路的输出电阻的串联,总电路输出电阻等于输出端开环等效电阻与闭环反馈电阻的并联,开环输出电阻为 ,闭环反馈电阻为

,闭环反馈电阻为 是电路的环路增益,等效电路如下:

是电路的环路增益,等效电路如下:

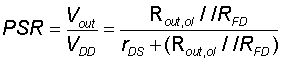

PSR可以看做是上图中VDD与Vout的电压比值,即 。

。

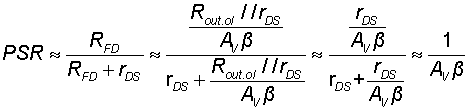

在电路实际工作在不同频率下PSR的值也会不同,在低频阶段,高环路增益导致电流绝大部分流向 ,又由于

,又由于 ,所以

,所以 这也是理想情况;在频率升高至放大器带宽以上时,放大器的开环增益下降,这导致

这也是理想情况;在频率升高至放大器带宽以上时,放大器的开环增益下降,这导致 增大,PSR变差。开环增益需乘上衰减因子

增大,PSR变差。开环增益需乘上衰减因子 ,

, 表示放大器的带宽,当频率增加到单位增益频率(Unit Gain Frequency,简称UGF)时,放大器增益为1,反馈环路消失,

表示放大器的带宽,当频率增加到单位增益频率(Unit Gain Frequency,简称UGF)时,放大器增益为1,反馈环路消失, 失效;当频率继续增加,电容的等效阻抗继续减小,从而对

失效;当频率继续增加,电容的等效阻抗继续减小,从而对 的分流程度继续增大,输出端的交流分量减小,VDD的交流分量不变。在频率增加过程中PSR的表达式变化如下:

的分流程度继续增大,输出端的交流分量减小,VDD的交流分量不变。在频率增加过程中PSR的表达式变化如下:

仿真验证

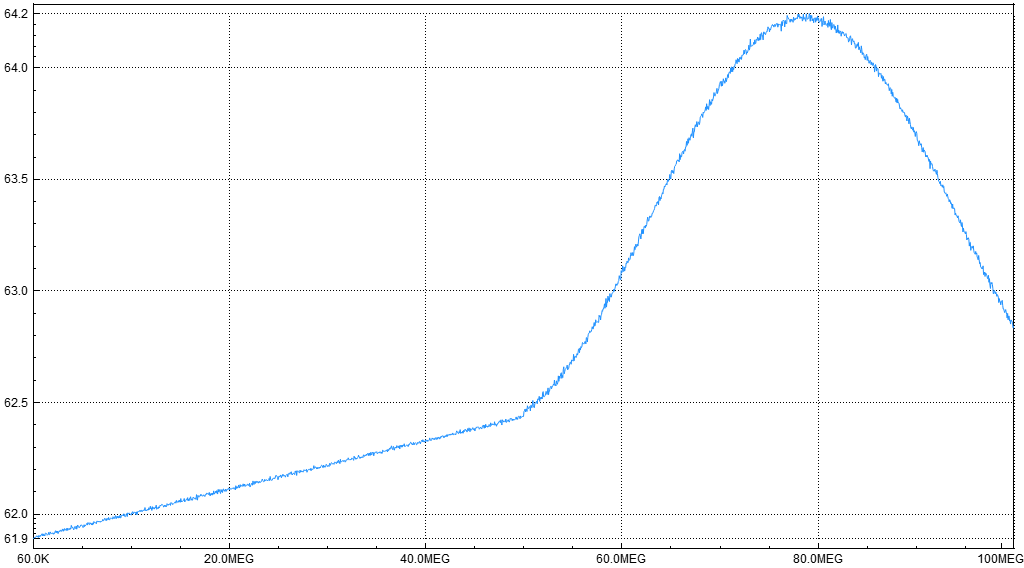

在巨霖PowerExpert中搭建LDO的PSR分析电路并进行AC仿真,仿真电路和结果如下:

由仿真结果可见,该电路的PSR变化趋势符合上述分析。

PSR优化

通过上述对 LDO 电路的电源抑制比 PSR 进行了分析量化,在实际设计过程中有很多种优化放置,篇幅问题本文仅简单提出三种,不做仿真和验证。最直接方式是增加输出电容减小噪声,从而提高PSR,但是这会增大器件的版图面积,增加成本;还可以减小 LDO 的负载,电路对电源噪声敏感度降低,但会导致高功耗,影响使用寿命;还可以采用高PSR 基准源,使供电电源更稳定,电源噪声对输出更少影响,但电路结构变得更加复杂,还引入了新噪声源。综上所述,以上这些方式都有各自优点与缺点,在实际设计中需要考虑各种因素,选择适合的优化方式,再使用仿真软件验证,巨霖的PowerExpert作为电路仿真软件,具有精度高,收敛性好,器件库丰富等优势,可以在实际电路设计中精准仿真电路,成为工程师们设计环节的有力助手。

欢迎从官网申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!

-

LDO电源抑制比的测量方法2024-07-14 2848

-

什么是LDO?浅析低压差稳压器 (LDO) 中的噪声及电源抑制比2024-03-15 7388

-

电源抑制比怎么提高2023-12-12 1788

-

电源抑制比是什么意思?电源抑制比怎么提高?2023-09-02 10347

-

电源之LDO-4. LDO的电源抑制比2023-07-24 3323

-

电源抑制比简述2023-04-24 10917

-

LDO基础知识:电源抑制比2022-11-01 845

-

一文详解LDO的电源抑制比2022-08-30 27114

-

关于ldo的纹波抑制比 精选资料分享2021-07-30 1876

-

LDO的电源抑制比测量2019-03-20 4000

-

关于LDO基础知识:电源抑制比2018-06-28 25966

-

高电源抑制比无片外电容LDO设计2018-02-23 1178

-

电源抑制比(PSRR),电源抑制比(PSRR)是什么意思2010-03-09 16387

全部0条评论

快来发表一下你的评论吧 !