精度测频资料分享

描述

原理

1 常用的测频方法[1]

① 利用电路的某种频率响应特性来测量频率,如谐振测频法[低频测量,应用较广]、电桥测频法[高频、微波段测量]

② 利用标准频率与测频进行比较来测量,精度取决于标准频率的准确度,如拍频法[低频]、示波器法[低频]、差频法[高频]

③ 电子计数测频法[适用于用数字电路实现]:直接测频法[测周期法和测频率法]和等精度测频法

2 频率测量的常用方法

| 直接测频法 |

原理:在一个单位时间t里计数被测信号的上升沿/下降沿的个数N。如t=1s,则被测信号频率为N Hz。 优点:过程简单,计算量少,计数的结果就是被测信号的频率 缺点:单位时间t的精确影响测量误差;计数个数存在±1的误差,其对低频影响较大,对高频影响较小。 缺点:整个测频范围内的测频精度是不同的。如闸门时间是1s时,测量100MHz的信号可达到10-8的测量精度,但测量10Hz的信号只能达到10-1的测量精度。[3] 适用:存在正负1误差,适合于高频 |

| 周期测频法 |

原理:测量被测信号连续两个上升沿/下降沿之间的时间间隔t,再求t的倒数。 或:在被测信号的一个周期里,计数标准信号的个数N,N*t(t为标准信号周期)即为被测信号的周期,1/N*t即为频率。 优点:测量时间快,最短只需被测信号的一个周期 缺点:需要求倒数/除法运算,存在误差;计数时间间隔存在±1的误差;这些误差对低频影响小,对高频影响大;当被测信号频率大于标准信号时,这种方法几乎不可以用 适用:适用于低频,当被测信号大于标准信号时,不适用。 |

| 等精度测频法 |

原理:对时间闸门信号用被测信号进行同步,达到减少正负1的误差。对低频信号尤其有效。 计算:标准时钟计数结果为Nt,频率为Fs,单位为Hz,则被测频率Ft = Fs*(Nt/Ns) 优点:在低频阶段比直接测频法有所改进,在测量频率比标准频率高时,精度不会提高。 |

3 等精度测频法原理

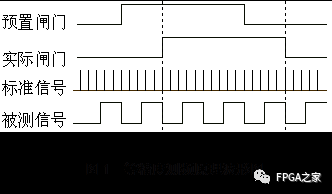

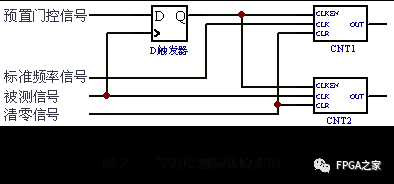

等精度测频方法是在直接测频方法的基础上发展起来的。如图1所示,它的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,其实现方式可用图2来说明。图中,预置门控信号是为Tpr 的一个脉冲,CNT1和CNT2是两个可控计数器。标准频率信号从CNT1的时钟输入端CLK输入,其频率为fs 。经整形后的被测信号(频率为fx)从CNT2的时钟输入端CLK输入,当预置门信号为高电平(预置时间开始)时,被测信号的上升沿通过D触发器的Q端同时启动计数器CNT1和CNT2计数。CNT1和CNT2分别对被测信号(频率为fx)和标准频率信号(频率为fs)同时记数。同样,当预置门信号为低电平(预置时间结束)时,随后而至的被测信号的上升沿通过D触发器的输出端,同时关闭计数器的计数。设在一次预置门时间Tpr中计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns。则下式成立:

由此可推得:

等精度测频法具有三个特点:

(1)相对测量误差与被测频率的高低无关;

(2)增大Tpr或fs可以增大Ns,减少测量误差,提高测量精度;

(3)测量精度与预置门和标准频率有关,与被测信号的频率无关,在预置门和常规测频闸门时间相同而被测信号频率不同的情况下,等精度测量法的测量精度不变。

一种实现过程[7]

① 预设闸门模块:由标准时钟产生预设闸门信号。如标准时钟100us[10kHz],计数1000次,产生预设闸门信号为100ms

② 实际闸门模块:用被测信号来同步预设闸门模块产生的闸门信号来产生新的实际闸门信号,本质是一个D触发器

③ 计数模块:在实际闸门信号有效时,标准时钟和被测信号同时计数,在闸门信号结束时输出计数结果

④ 频率计算模块:由公式进行乘法和除法运算

直接计数测频法

测频法原理:在确定的闸门时间Tw内,记录被测信号的变化周期数或脉冲个数Nx,有fx=Nx/Tw [1]

测周期法原理:需要有标准信号频率fs,在待测信号的一个周期时间Tx内,记录标准频率的周期数Ns,有fx=fs/Ns [1]

最高测量频率为标准信号频率[个人总结]。

测量误差:两种方法都会产生±1个字的误差。最大误差为1/N,N为周期个数。[1]

直接计数测频法缺点:整个测频范围内的测频精度是不同的。如闸门时间是1s时,测量100MHz的信号可达到10-8的测量精度,但测量10Hz的信号只能达到10-1的测量精度。[3]

参考信号:测频法需要得到一个标准的脉宽,测周期法需要一个标准时钟。实际上标准的脉宽必须从一个标准时钟分频得到,而一般,标准始终是从外部晶振分频得到。[1]

测量时间:当计数周期为106个时,计数时间为1s[个人总结]

1 /********************************************************************************* 2 * Company : 3 * Engineer : 空气微凉 4 * 5 * Create Date : 0000 22/03/2013 6 * Design Name : 7 * Module Name : 8 * Project Name : 9 * Target Devices : 10 * Tool versions : 11 * Description : 12 * http://www.cnblogs.com/kongqiweiliang/ 13 * Dependencies : 14 * 15 * Revision : 16 * Revision : 0.01 - File Created 17 * Additional Comments : 18 ********************************************************************************/ 19 `timescale 1ns/1ps 20 `define UD #1 21 /*******************************************************************************/ 22 module Equalfre 23 ( 24 input iGate ,// 25 input iFx ,// 26 input iFo ,// 27 output reg [31:0] oFxCount ,// 28 output reg [31:0] oFoCount // 29 ); 30 //------------------------------------------------------------------------------- 31 reg Start_Count ; 32 reg [31:0] FxCount ; 33 reg [31:0] FoCount ; 34 35 always@(posedge iFx)begin 36 if(iGate) 37 Start_Count <= 1'h1; 38 else 39 Start_Count <= 1'h0; 40 end 41 42 always@(posedge iFo)begin 43 if(Start_Count) 44 FoCount <= FoCount + 1'h1; 45 else 46 FoCount <= 0; 47 end 48 49 always@(posedge iFx)begin 50 if(Start_Count) 51 FxCount <= FxCount + 1'h1; 52 else 53 FxCount <= 0; 54 end 55 56 always@(negedge Start_Count)begin 57 oFxCount <= FxCount; 58 oFoCount <= FoCount; 59 end 60 //------------------------------------------------------------------------------- 61 endmodule

-

FPGA与信号频率测量——等精度测频法2023-11-06 1602

-

展频晶振介绍资料2023-04-14 610

-

高精度音响晶振常用频点2022-05-19 2237

-

基于STM32和CPLD可编程逻辑器件的等精度测频资料下载2021-04-16 1060

-

使用等精度测频原理设计频率计的程序与仿真资料免费下载2021-01-20 1073

-

CDMA信号的时频差高精度估计算法2017-11-20 1122

-

基于DSP的高精度测频方法与软件设计_薛海东2017-03-19 795

-

DSP之采用等精度测频原理的频率计程序与仿真2016-04-15 492

-

msp430等精度测频程序(源码)2012-11-29 24632

-

ARM设计的等精度测频技术在机组转速测控中的应用2010-07-21 1377

-

高精度压频变换电路图2009-04-10 1098

-

使用SPCE061A单片机实现高精度测频2009-01-02 1799

全部0条评论

快来发表一下你的评论吧 !