高速ADC设计中采样时钟影响的考量

描述

在使用高速模数转换器 (ADC) 进行设计时,需要考虑很多因素,其中 ADC 采样时钟的影响对于满足特定设计要求至关重要。关于 ADC 采样时钟,有几个指标需要了解,因为它们将直接影响 ADC 性能,尤其是信噪比 (SNR)。

在本文中,我们将探讨大量实验和权衡——并寻求在工作台上证明它们——以便让您更好地了解下一个 ADC 时钟设计。

时钟权衡及其对 ADC 性能的影响

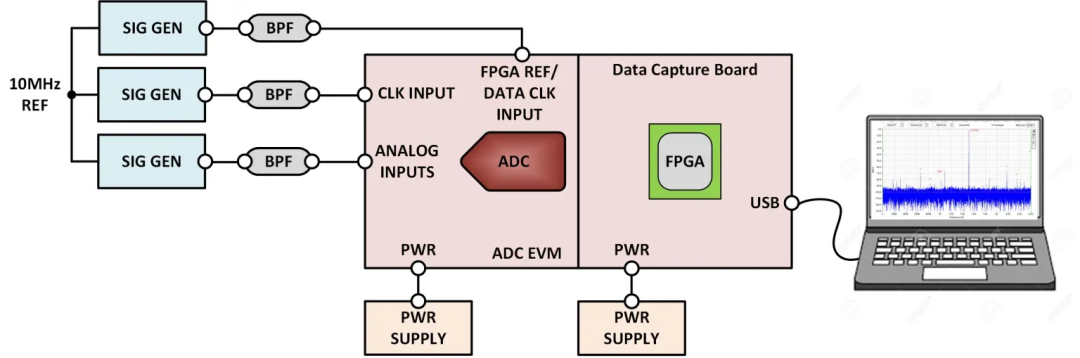

我们使用了一个带有三个信号发生器的评估模块,它们提供 ADC 所需的不同信号,如图1所示。模拟和时钟输入均通过 10 MHz 参考信号锁定参考,并使用带通滤波器进行滤波,以消除来自信号发生器的任何不需要的噪声和杂散。

图 1 ADC 测试测量设置在实验室中的样子。资料来源:德州仪器

在尝试最大限度地提高高速转换器设计的性能时,有许多权衡。让我们首先从源开始:实验室中用作采样时钟源的信号发生器。在实验中,我们使用了输出功率为 +10 dBm 的 25 MHz 时钟或信号发生器。我们在相同条件下配置每个信号发生器,以了解相对相位噪声对转换器性能的影响。

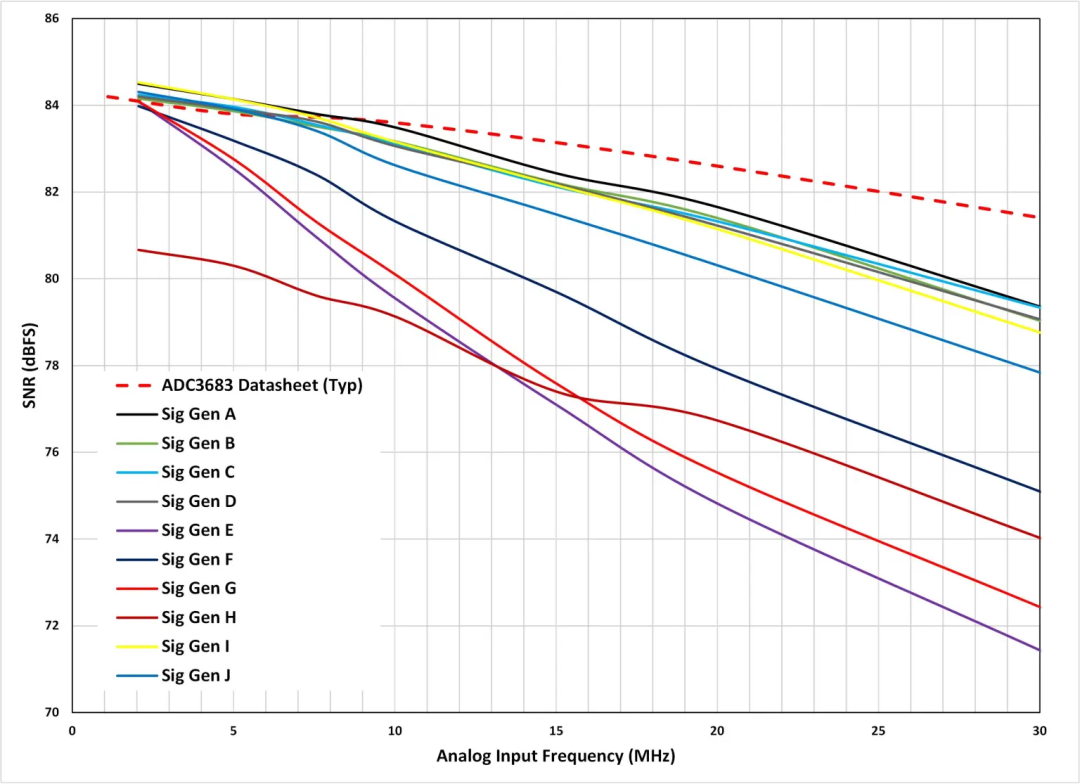

然后,我们利用图 2所示的不同信号发生器以 25 MSPS 的频率对 ADC 进行时钟控制。对于每个测试源,我们将时钟保持在 +10 dBm 不变,并将模拟输入频率 (Fin) 从 2 MHz 扫描至 30 MHz。在每个频率点,我们将信号发生器的输出功率水平调整为 -1 dBFS,然后测量相对于满量程的 SNR 值(以分贝为单位)。为了保持实验的一致性,我们始终使用性能最高的信号源作为模拟输入源。

图 2 ADC 的 SNR 与 Fin@-1 dBFS 的关系显示采用不同的时钟信号源,频率为 25 MSPS @ +10 dBm。资料来源:德州仪器

如图 2 所示,当模拟频率增加时,SNR 开始下降并恶化。这个术语称为“抖动受限”,这意味着在某个时刻,ADC 时钟源、时钟信号链或两者的抖动或相位噪声将开始主导转换器的整体性能,导致在使用噪声更大的时钟源操作转换器时 ADC 的 SNR 更差。

如您所见,随着模拟输入频率的增加,每个信号发生器的相位噪声贡献略有不同,而在较低的模拟输入频率下,相位噪声的影响较小。

时钟的斜率是影响 ADC 性能的另一个特性。时钟沿的斜率越尖锐,减少抖动的可能性就越大。当采样时钟沿穿过 ADC 的采样阈值时,尽量减少时钟沿的时序不确定性也很重要。

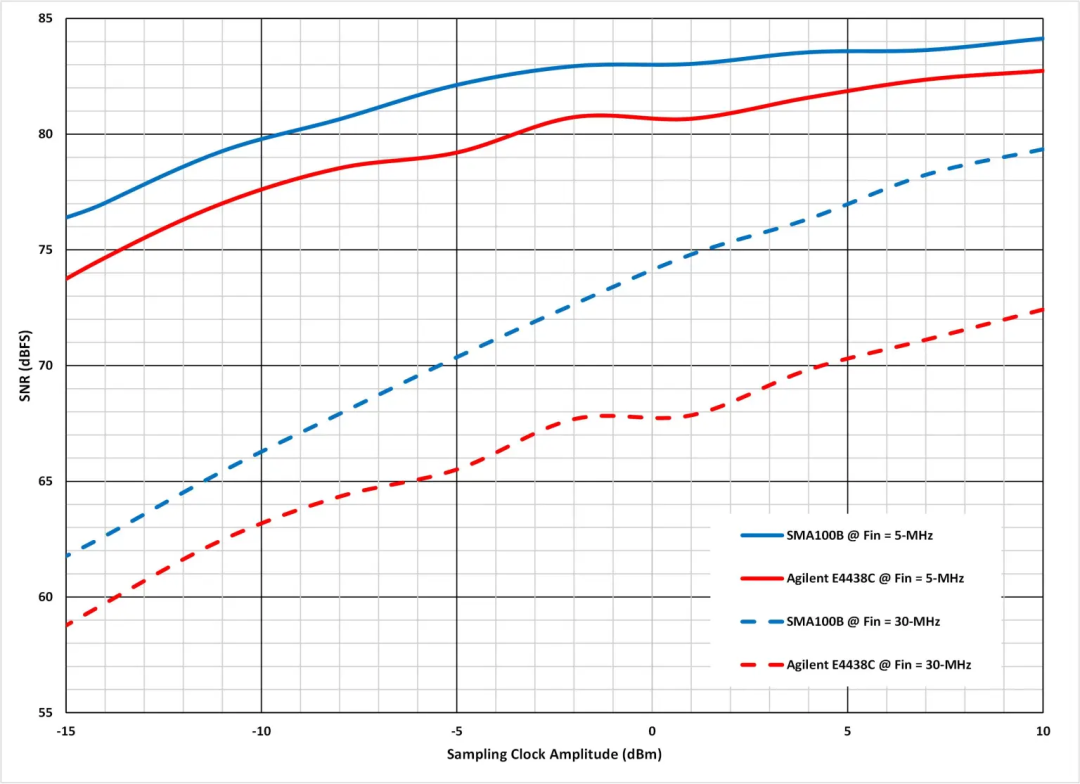

图 3展示了使用高性能信号时钟源和低性能信号时钟源时 ADC 采样时钟斜率对 ADC 性能的影响。从图中可以看出,当将 25 MSPS 时钟源的幅度水平从 +10 dBm 降低到 -15 dBm 并保持 5 MHz 和 30 MHz 模拟输入频率的输出功率水平恒定时,随着时钟信号源变为 +5 dBm 或更小,SNR 开始下降。

图 3 SNR 与采样时钟幅度的关系显示了斜率。来源:德州仪器

请记住,每个 ADC 都有自己的灵敏度水平;因此,+5 dBm 并不涵盖所有情况。它只适用于此 ADC 测试案例,以证明时钟源上更锐利的转换速率如何帮助您从 ADC 获得最佳 SNR。

根据预期的 ADC 性能应用时钟权衡

相位噪声曲线中噪声的一个较大贡献者是噪声基底,也称为宽带噪声。如果一个源的噪声基底高于另一个源,则噪声基底较高的源将增加相位噪声曲线下的面积,从而增加指定积分带宽的抖动值(请注意,抖动是相位噪声的积分)。

带通滤波器通常有助于降低时钟信号和/或模拟输入信号源的宽带噪声。它们还能过滤掉不必要的杂散信号,即使是高性能、低噪声信号发生器也会产生这种杂散信号。

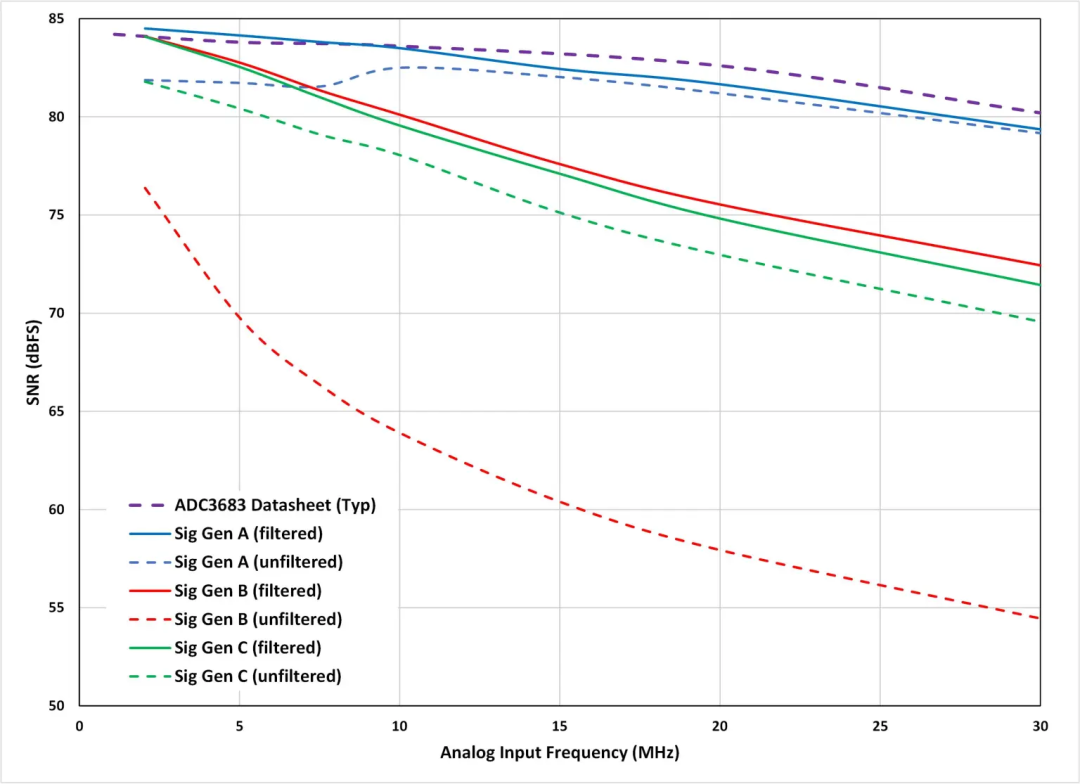

图 4展示了 ADC 的 SNR 性能与模拟输入频率的关系,使用相同的三个信号发生器作为采样时钟(滤波和未滤波两种情况)。在用于时钟的信号发生器的输出上应用滤波器时,可以清楚地看到 SNR 的改善。在性能较低、本底噪声较高的信号发生器上应用滤波器时,情况也是如此,因为其固有相位噪声本来就很差。

图 4显示了在使用不同时钟信号源时 ADC 的滤波和无滤波的 SNR。来源:德州仪器

到目前为止,我们已经使用信号发生器来演示时钟信号的各种权衡。然而,在现实世界中,大多数设计人员都会为他们的 ADC 设计选择特定的时钟设备。在某些情况下,设计人员甚至可能希望使用现场可编程门阵列 (FPGA) 作为 ADC 的采样时钟,尽管我们在 TI 不建议这样做,因为用作时钟的 FPGA 与其他时钟设备相比具有显着的抖动。

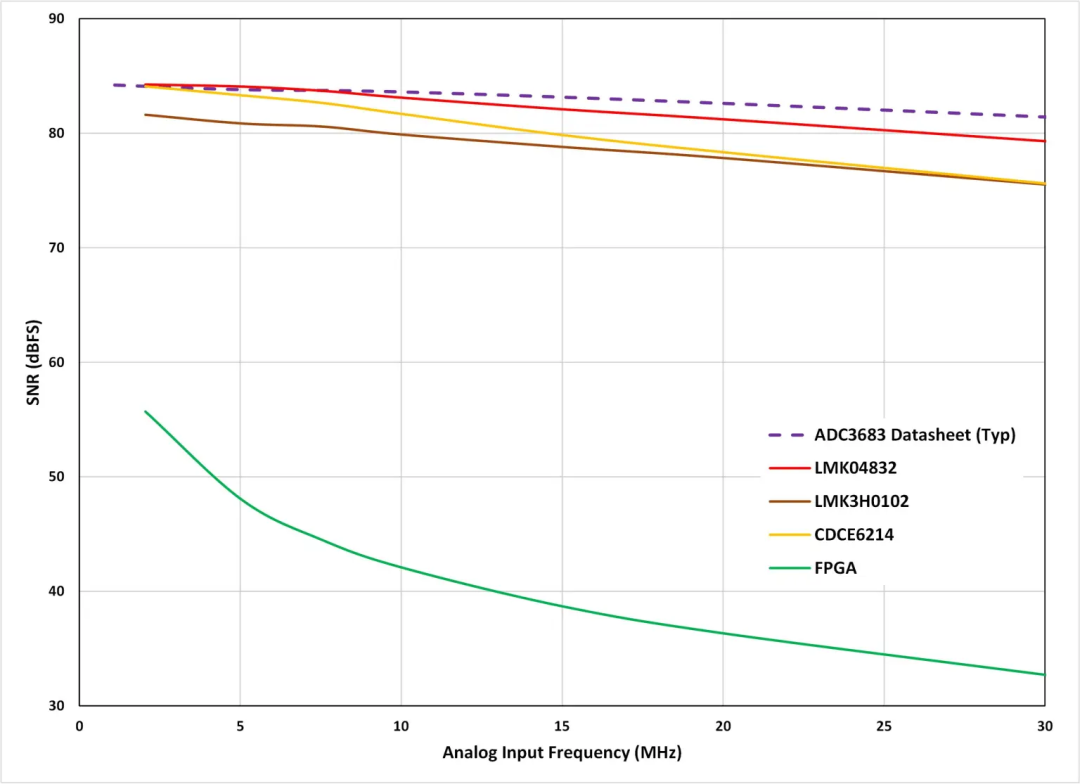

为了进一步解释 FPGA 时钟对 ADC 性能的影响,图 5展示了使用 FPGA 输出时钟为 ADC 提供时钟时对 ADC 的 SNR 性能的影响,而其他时钟设备则不然。具有较高相位噪声和较高本底噪声的时钟源会显著影响转换器的性能。

图 5这是时钟设备和 FPGA 输出时钟与 ADC 的 SNR 在模拟输入频率上的关系。来源:德州仪器

为了实现 ADC 数据表的 SNR,您可能需要考虑多种权衡,以优化您的应用的时钟信号链。这可能包括使用无源巴伦实现而不是有源设备,因为无源巴伦会将更少的噪声引入 ADC 或系统。虽然无源设备会带来更干净的性能,但它们有时在空间和成本方面存在劣势。

正如我们在本文开头提到的,具有高转换速率的快速上升信号(例如低压正射极耦合逻辑 (LVPECL) 或电流模式逻辑 (CML))可使 ADC 性能优于低压差分信号 (LVDS)。差分式接口也更好,因为它们本身可以消除任何共模噪声。将时钟设备输出配置为单端低压互补金属氧化物半导体 (LVCMOS) 信号会导致 ADC 的 SNR 性能降低。

选择合适的时钟

提供干净、高转换速率的时钟源对于最大程度地提高任何 ADC 性能都至关重要。这些基本原理在使用每秒千兆采样的 ADC 或任何高速 ADC 进行设计时也适用,尽管本文中的所有实验案例都在每秒兆采样的范围内。

了解相位噪声和抖动之间的差异也至关重要。确保将积分带宽上限设置为至少 Fs(我们建议为采样频率的两倍),以捕获采样时钟源贡献的抖动的噪声基底。请记住,宽带噪声基底是相位噪声和抖动计算的最大噪声贡献者,对 ADC 的 SNR 性能影响最大。

选择正确的时钟有助于实现 ADC 的预期性能,因为并非所有时钟设备、振荡器和信号源都是一样的。在适当的时候对时钟进行滤波,有助于降低杂散、降低宽带噪声或两者兼而有之。然而,使用滤波器时可能会有权衡,因为滤波器会降低时钟沿的斜率。

远离 FPGA 时钟。我们知道,它们在 FPGA 结构中设计和实现起来很简单,而且是一种低成本的替代方案。但如果 ADC 的 SNR 性能是您设计的重点,那么它们就无法提供所需的性能。

选择正确的时钟接口也很重要。差分信号是消除时钟信号上的共模噪声和干扰的关键。使用 LVPECL 或 CML 类型的接口可获得最佳的斜率信号质量,而不是 LVDS 或单端 LVCMOS 时钟信号接口。

-

求助,关于高速ADC采样的几个问题求解2025-01-14 477

-

10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能#ADCEE_Voky 2022-08-16

-

PCB接地设计宝典4:采样时钟考量和混合信号接地的困惑根源2014-11-20 15068

-

请问关于高速ADC时间交替采样时钟同步问题2018-07-24 3309

-

信号分析仪和无线测试仪中的射频采样高速ADC时钟解决方案2018-09-30 3399

-

存在高速ADC(如100M以上)拥有外部事件使能引脚的么,就是外部事件直接让ADC在这个点进行采样,不用考虑时钟的2022-03-14 15787

-

PDMA可以做高速ADC采样吗?2023-06-26 431

-

高速ADC的低抖动时钟设计2009-11-27 729

-

高速ADC时钟抖动的影响的了解2017-05-15 1678

-

高速ADC在低抖动采样时钟电路设计中的应用2017-11-27 1320

-

了解时钟驱动高速 ADC的使用方法2018-06-13 6961

-

ADC采样时钟的计算方法解析2019-10-14 21627

-

如何去正确理解采样时钟抖动(Jitter)对ADC信噪比SNR的影响2021-04-07 10904

-

计算隔离式精密高速DAQ的采样时钟抖动的简单步骤分享2022-11-13 1710

-

ADC时钟极性与启动时间的关系2023-01-05 2276

全部0条评论

快来发表一下你的评论吧 !