复位电路的设计问题

描述

前言

最近看advanced fpga 以及fpga设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

流程:

1.同步复位:

优点:⑴大多数DFF都有异步复位端口,因此采用异步复位可以节约资源。

⑵设计相对简单。

⑶异步复位信号识别方便,而且可以很方便地使用fpga的全局复位端口。

缺点:⑴在复位信号释放时容易出现问题,亚稳态。

⑵复位信号容易受到毛刺的影响。这是由于时钟抖动或按键触发时的硬件原因造成的。

代码:一个4bit的计数器。

1 always @(posedge clk /*or negedge sys_rst_n*/) begin 2 if (~sys_rst_n) begin 3 count <= 0; 4 end //if 5 else begin 6 count <= count + 1'b1; 7 end //else 8 end //always

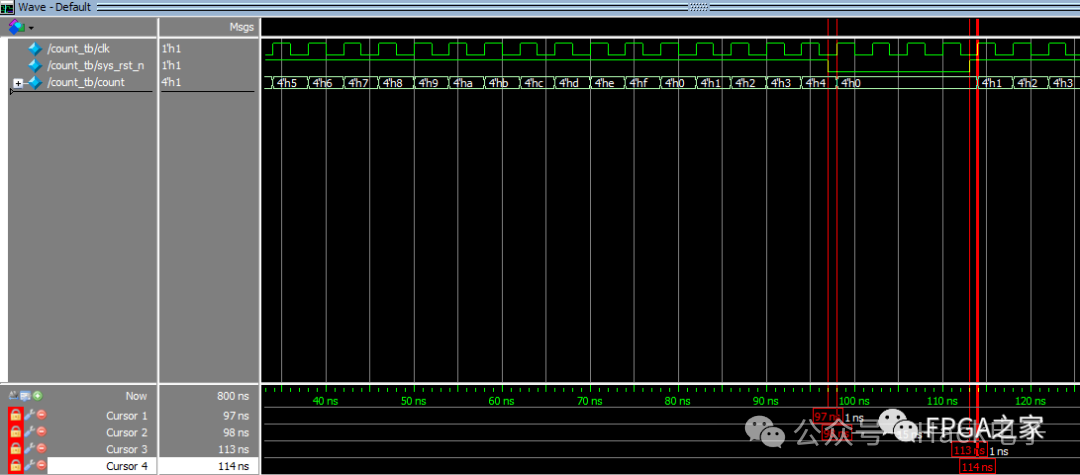

仿真解析(下图):

时钟上升沿如果复位信号为低电平,复位开始,时钟上升沿若复位信号为高电平,复位结束。

2.异步复位:

优点:⑴降低亚稳态出现的概率。

⑵使所设计的系统成为100%的同步时序电路,有利于时序分析,综合出来的Fmax一般较高。

⑶只有在时钟有效沿才有效,可以滤除高于时钟频率的毛刺。

缺点:⑴复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。

⑵大多数的Dff只有异步复位端口,会浪费较多的逻辑资源。

代码:

1 always @(posedge clk or negedge sys_rst_n) begin 2 if (~sys_rst_n) begin 3 count <= 0; 4 end //if 5 else begin 6 count <= count + 1'b1; 7 end //else 8 end //always

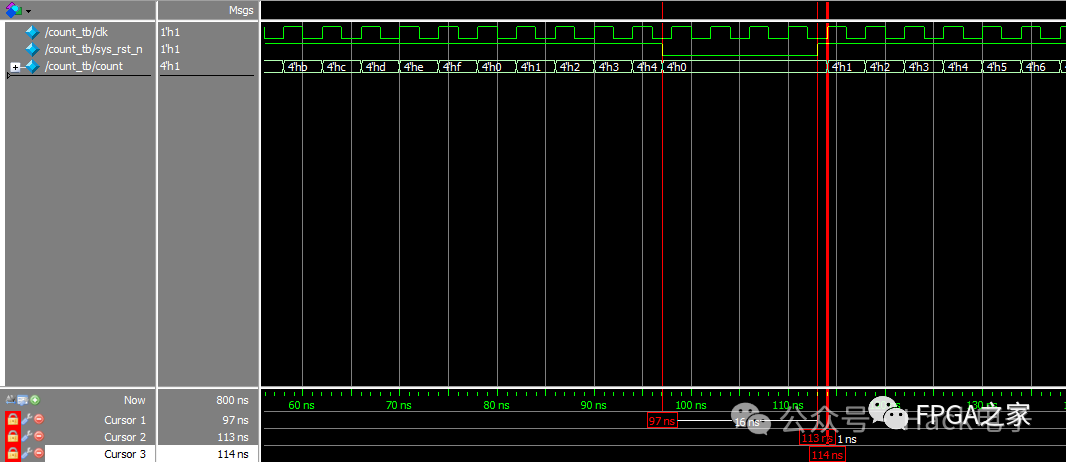

仿真解析(下图):

复位信号低电平时候,系统立刻进入复位态;

3.异步复位同步释放:(推荐使用)

优点:结合了同步复位与异步复位的优点。

缺点:容易受到噪声与宰脉冲的干扰。如果可能,最好对输入到fpga的异步复位信号先进行滤波与去抖动。

代码:

1 module rstn_as ( 2 //input; 3 input wire clk, 4 input wire sys_rst_n, 5 //output; 6 output reg rst_n 7 ); 8 reg rst_n_reg; 9 always @(posedge clk or negedge sys_rst_n) begin 10 if (~sys_rst_n) begin 11 rst_n <= 1'b0; 12 rst_n_reg <= 1'b0; 13 end //if 14 else begin 15 rst_n_reg <= 1'b1; 16 rst_n <= rst_n_reg; 17 end //else 18 end //always 19 20 endmodule

wire rst_n; rstn_as u1( .clk (clk), .sys_rst_n (sys_rst_n), .rst_n (rst_n) ); always @(posedge clk or negedge rst_n) begin if (~rst_n) begin count <= 0; end //if else begin count <= count + 1'b1; end //else end //always

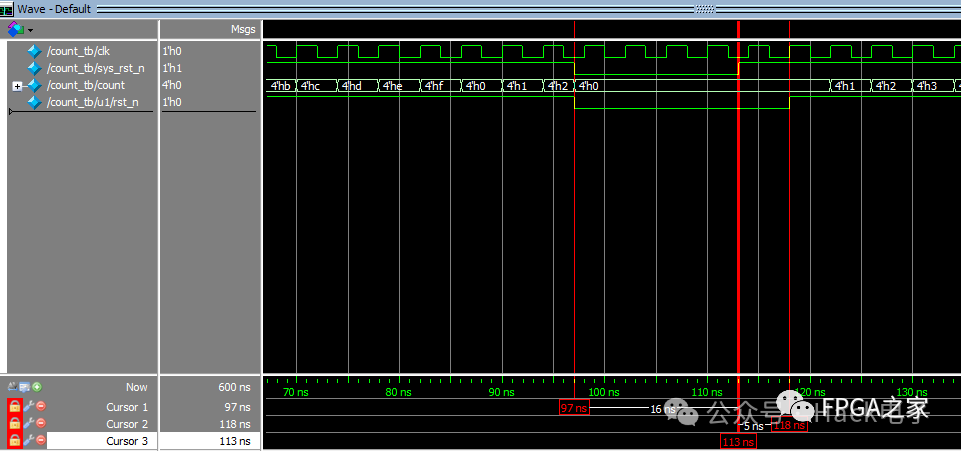

仿真解析(下图):

当复位信号低电平时,系统立即复位;当时钟上升沿检测到复位信号失效后,在下一个时钟上升沿拉高rst_n。新的rst_n是已经同步化了的复位信号。

-

复位电路静电整改案例分享(一)——交换机复位电路2024-10-19 1682

-

复位电路介绍 复位电路的原理及作用2024-10-18 9616

-

STM32复位电路用复位芯片和阻容复位电路区别2024-08-06 4166

-

rc复位电路的电阻作用2023-12-14 3384

-

MCU复位电路知多少?2023-10-17 2738

-

复位电路2022-01-17 773

-

STM32复位电路2021-12-24 1161

-

复位电路的设计2021-11-06 1488

-

复位电路的作用是什么2021-08-07 30773

-

复位电路集锦2016-12-14 826

-

复位电路及具有所述复位电路的电视机2011-11-11 1113

-

常见的复位电路2011-04-18 11529

-

主板的复位电路检修2009-04-26 4313

-

RC复位电路2008-10-24 3849

全部0条评论

快来发表一下你的评论吧 !