Achronix Speedcore eFPGA的特性和功能

描述

Speedcore嵌入式FPGA(embedded FPGA,eFPGA)知识产权(IP)产品是Achronix公司于2016年推出的颠覆性技术,并于当年开始向最终客户交付,目前出货量已经超过2500万。

Achronix的第四代Speedcore eFPGA IP(Speedcore Gen4),该产品添加了机器学习处理器(MLP)模块,在保留原有功能的基础上,将性能提高了60%、功耗降低了50%、芯片面积减少65%,可为需要大量计算和I/O带宽的全新人工智能/机器学习及高性能应用提供强有力的支持。Speedcore Gen4在多个工艺节点上可用,包括台积电(TSMC)的7纳米工艺技术等。

利用Speedcore eFPGA IP,客户可以将FPGA功能集成到他们的SoC中,使他们既可以拥有在ASIC中才能实现的最佳硬件加速平衡,又可以拥有FPGA技术的灵活性和可编程性。

本文详细介绍了Speedcore eFPGA的特性和功能,欢迎您阅读,以进一步了解该产品。您也可以在Achronix微信公众号的“产品介绍”栏目中随时阅读本文。

产品亮点

Speedcore嵌入式FPGA(eFPGA)知识产权(IP)——唯一一款已在各种大规模量产应用中采用的eFPGA技术。

客户可自定义eFPGA的资源,包括逻辑资源、RAM资源、机器学习处理器(MLP)/DSP模块、二维片上网络(2D NoC):

逻辑单元——6输入查找表(LUT),并且集成了广泛的MUX函数和快速加法器

逻辑RAM —— LRAM2k每个存储模块的容量为2kb;LRAM4k每个存储模块的容量为4kb

块RAM —— BRAM72k每个存储模块的容量为72kb;BRAM20k每个存储模块的容量为20kb

DSP64模块——每个模块都带有18×27乘法器、64位累加器和27位预加器

机器学习处理器(MLP)——在DSP64基础上做了升级。支持整数(int4/int8/in16/int32)和浮点格式(FP24,FP16,bfloat16)。对不同的乘法器精度,每个MLP可支持的乘法器数量会不同,最多支持32个乘法器/累加器(MAC)

2D NoC——用户还可以在定制二维片上网络2D NoC,以实现大带宽的高效数据交互。

客户自定义的模块

Achronix以一个GDSII的形式提供eFPGA IP。

SpeedcoreIP在以下工艺技术节点上可用:

TSMC 16FFC

TSMC 12FFC

TSMC N7/N6

TSMC N3A

SpeedcoreIP也可以移植到其他工艺节点上

Speedcore的性能:

最高运行频率:750MHz

典型运行频率:300MHz-500MHz

延迟最低的接口:

在Speedcore实例与宿主SoC之间仅有一步延迟

支持零延迟接口

Achronix的ACE设计工具可为Speedcore IP提供支持:

功能齐全的工具可为以Speedcore eFPGA为目标的RTL进行综合、布局、布线和优化性能等操作

包括用于综合的Synplify Pro工具

易于评估:

使用Achronix的ACE设计工具进行基准测试的设计

使用VectorPath加速卡验证功能

Speedcore eFPGA IP为ASIC和SoC带来了可编程逻辑的强大功能和灵活性。客户明确其逻辑LUT、RAM、MLP/DSP资源、NoC等需求,然后Achronix就会配置满足其个性化需求的Speedcore IP。Speedcore查找表(LUT)、RAM、MLP和DSP64模块等可以像积木一样进行组装,从而为任何给定的应用创建优化的可编程结构。在Speedcore IP的交付包中,还包括一个ACE设计工具的个性化版本,用于对Speedcore IP进行编程。

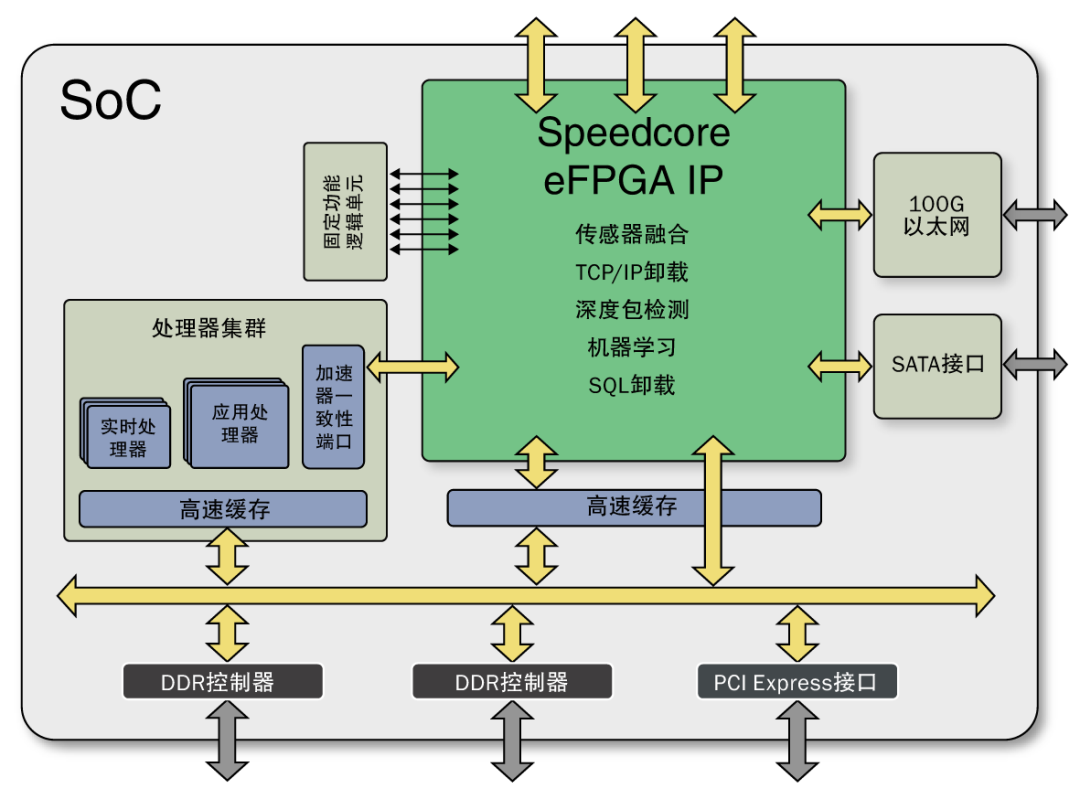

Speedcore集成框图

Speedcore eFPGA技术已实现量产,并且自2016年起开始交付给最终客户,目前出货量已经超过2500万。Achronix的客户包括一些全球最大的科技公司。这些公司已经认识到Speedcore IP是一种颠覆性技术,可以使他们显著提高其系统的整体性能。

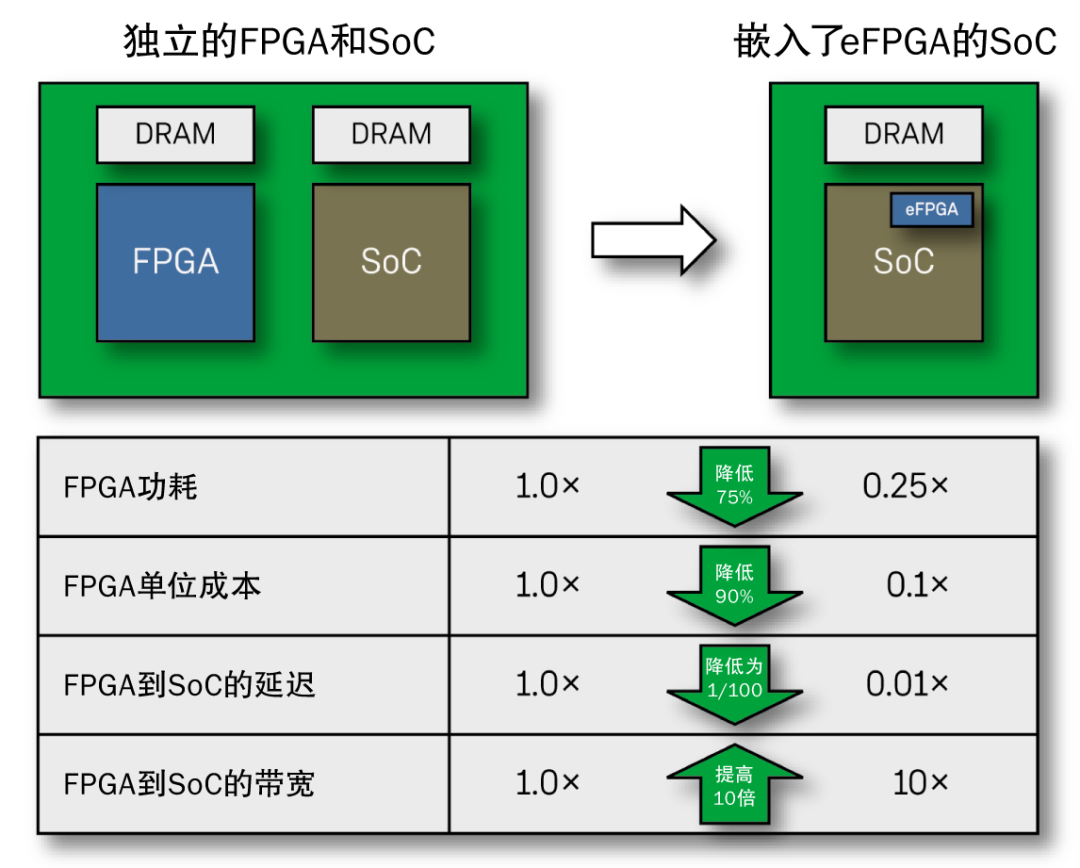

在SoC中嵌入Speedcore技术将带来诸多好处,与一款独立的FPGA芯片相比,Speedcore eFPGA IP提供了以下优点:

降低75%的功耗

节省90%的成本

1/100的延迟

高10倍的带宽

Speedcore eFPGA可以最小化芯片面积,提高性能,降低功耗,减少成本并且令SoC设计历久弥新

经过验证的技术

构建SoC的成本和风险非常高,不能冒险使用未经验证的嵌入式IP。Achronix是唯一一家可以同时大批量生产并交付eFPGA和独立FPGA的公司。设计人员可以100%确信SpeedcoreIP将会正常工作,因为它已得到全面的验证,并且经过了流片验证。

工艺技术

Speedcore IP在台积电的16FFC, 12FFC,N7/N6, N3A工艺节点上均可用。对于其他工艺技术,Achronix可以轻松移植SpeedcoreIP以支持其需求。请联系Achronix获取更多关于移植Speedcore技术的详细信息。

评估Speedcore eFPGA

在将Speedcore技术部署于SoC中之前,Achronix可以轻松地对其进行评估:

通过使用一个Speedcore eFPGA的示例实例,Achronix的ACE设计工具可被用来编译设计,以对性能、资源使用率和编译时间等进行评估。

Achronix使用其Speedcore芯片尺寸生成器(Speedcore Die Size Builder)工具来估算eFPGA实例的大小。

评估设计可以被加载到Achronix的VectorPath加速卡中,以验证功能和性能。

此外,SpeedcoreIP附带超过一千页的详细文档,以帮助您将该技术集成到您的SoC中。Achronix还提供了如下一些现场教程:

基准测试和评估

物理设计实现

时钟和复位网络设计

时序收敛

配置

验证

Speedcore支持广泛的应用

将Speedcore技术嵌入复杂的器件中,除了这些直接客观上的各项优势,设计人员还可以为其SoC设计增加独有的、长期的价值。Speedcore IP内核作为可重新配置的协处理器和硬件加速器来支持各种各样的任务,相比面向字的(word-oriented)CPU架构,这些任务在面向位的(bit-oriented)FPGA架构上执行时显然更加高效——诸如SQL卸载引擎、inline I/O处理、加密、搜索引擎算法加速、压缩和增强多媒体处理等功能。无论是使用Speedcore技术已实现量产的应用,还是目前正在由SoC设计人员使用Speedcore IP实现的应用,其范围都在不断扩大。

关于Achronix半导体公司

Achronix半导体公司是一家私有的、采用无晶圆厂模式的半导体公司,总部位于美国加利福尼亚州圣克拉拉市,同时提供高性能FPGA和嵌入式FPGA(eFPGA)解决方案。Achronix历来都是高性能FPGA市场向前发展的推动者之一。Achronix提供的产品包括可编程的FPGA结构,具有硬连线系统级模块的高性能、高密度独立FPGA,数据中心和高性能计算(HPC)硬件加速器板,以及支持所有Achronix产品的一流EDA软件。公司在美国、欧洲和中国都设有销售办公室和代表处,在印度班加罗尔设有一间研发和设计办公室。

-

Primemas选择Achronix eFPGA技术用于Chiplet平台2024-09-18 1564

-

基于Speedcore eFPGA IP构建Chiplet2023-09-06 1056

-

Achronix Speedcore eFPGA IP性能介绍2022-12-23 920

-

Achronix宣布其Speedcore eFPGA IP核出货量超千万个2021-03-26 2409

-

Achronix推出全新EFPGA项目,帮工程师快速构建低成本测试芯片!2018-12-24 1525

-

Achronix推出其第四代嵌入式FPGA产品2018-12-10 1064

-

Achronix半导体全面对接Speedcore eFPGA技术2018-12-01 3823

-

解密:Achronix 7nm eFPGA的设计方法2018-11-30 3498

-

Achronix与Mentor携手带来高等级逻辑综合(HLS)与FPGA技术之间的连接2018-08-30 8428

-

Achronix宣布为其eFPGA IP解决方案推出定制单元块2018-01-22 1186

-

Achronix定制单元块大幅提升Speedcore eFPGA性能2017-10-19 1431

-

全新Speedcore标准比FPGA更高效,大幅缩减芯片面积及功耗2017-10-18 2112

-

Achronix宣布用于SoC加速的Speedcore嵌入式FPGA IP产品开始供货2016-10-11 3462

全部0条评论

快来发表一下你的评论吧 !