低噪声放大器的两种设计方法与低噪声放大器设计实例

电子说

描述

低噪声放大器的两种设计方法

低噪声放大器(LNA)是射频收发机的一个重要组成部分,它能有效提高接收机的接收灵敏度,进而提高收发机的传输距离。因此低噪声放大器的设计是否良好,关系到整个通信系统的通信质量。本文以晶体管ATF-54143为例,说明两种不同低噪声放大器的设计方法,其频率范围为2~2.2 GHz;晶体管工作电压为3 V;工作电流为40 mA;输入输出阻抗为50 Ω。

1、定性分析

1.1、晶体管的建模

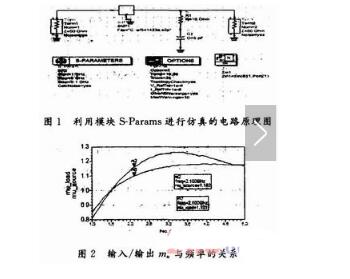

通过网络可以查阅晶体管生产厂商的相关资料,可以下载厂商提供的该款晶体管模型,也可以根据实际需要下载该管的S2P文件。本例采用直接将该管的S2P文件导入到软件中,利用S参数为模型设计电路。如果是第一次导入,则可以利用模块S-Params进行S参数仿真,观察得到的S参数与S2P文件提供的数据是否相同,同时,测量晶体管的输入阻抗与对应的最小噪声系数,以及判断晶体管的稳定性等,为下一步骤做好准备。

1.2、 晶体管的稳定性

对电路完成S参数仿真后,可以得到输入/输出端的mu在频率2~2.2 GHz之间均小于1,根据射频相关理论,晶体管是不稳定的。通过在输出端并联一个10 Ω和5 pF的电容,m2和m3的值均大于1,如图1,图2所示。晶体管实现了在带宽内条件稳定,并且测得在2.1 GHz时的输入阻抗为16.827-j16.041。同时发现,由于在输出端加入了电阻,使得Fmin由0.48增大到0.573,Γopt为0.329∠125.99°,Zopt=(30.007+j17.754)Ω。其中,Γopt是最佳信源反射系数。

1.3、制定方案

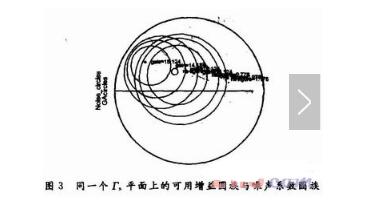

如图3所示,将可用增益圆族与噪声系数圆族画在同一个Γs平面上。通过分析可知,如果可用增益圆通过最佳噪声系数所在点的位置,并根据该点来进行输入端电路匹配的话,此时对于LNA而言,噪声系数是最小的,但是其增益并没有达到最佳放大。因此它是通过牺牲可用增益来换取的。在这种情况下,该晶体管增益可以达到14 dB左右,Fmin大约为0.48,如图3所示。

另一种方案是在可用增益和噪声系数之间取得平衡,以尽可能用小噪声匹配为目标,采用在兼顾增益前提下的设计方案。在这种情况下该晶体管增益大约为15 dB左右,Fmin大约为0.7(见图3)。这个就是本文中提到的第2种方案。

2、以最佳噪声系数为设计目标方案的仿真

2.1、输入匹配电路设计

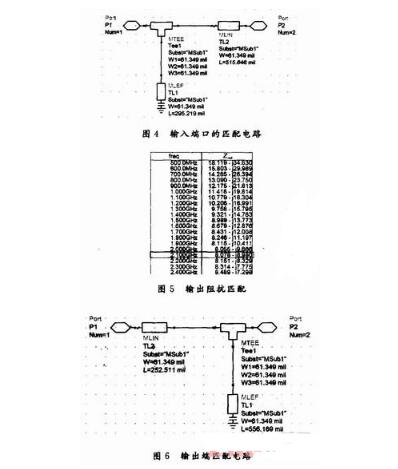

对于低噪声放大器,为了获得最小的噪声系数,Γs有个最佳Γopt系数值,此时LNA达到最小噪声系数,即达到最佳噪声匹配状态。当匹配状态偏离最佳位置时,LNA的噪声系数将增大。前面定性分析中已经获得Γopt=0.329∠125.99°,以及对应的Zopt=30.007+j17.754 Ω。下面可以利用ADS的Passive Circuit/Micorstrip ControlWindow这个工具,自动生成输入端口的匹配电路。

在原理图中添加一个DA_SSMatehl的智能模块,然后修改其中的设置:F=2.1 GHz,Zin=50 Ω。值得注意的是,利用该工具生成匹配电路时,Zload是Zopt的共轭。设置完毕后,再添加一个MSub的控件,该控件主要用于描述基板的基本信息,修改其中的设置为H=0.8 mm,Er=4.3,Mur=1,Cond=5.88×107,Hu=1.0e+33 mm,T=0.03 mil。设置完后,即可进行自动匹配电路的生成,结果电路如图4所示。

将输入匹配电路添加到图1后再进行S参数的仿真。可以看到,最佳噪声系数Γopt的位置由于输入匹配电路的加入而成功匹配到50 Ω的位置。

2.2、输出端匹配电路设计

根据最大功率增益原则进行输出端匹配电路的设计(考虑到输出稳定电路的存在,对输出阻抗的影响,在进行输出阻抗测量时要把稳定电路计算在内),即将输出阻抗(Zopt=8.055-j8.980,如图5所示)使用上述的方法匹配到50 Ω。得到的输出端匹配电路如图6所示。

2.3、仿真结果

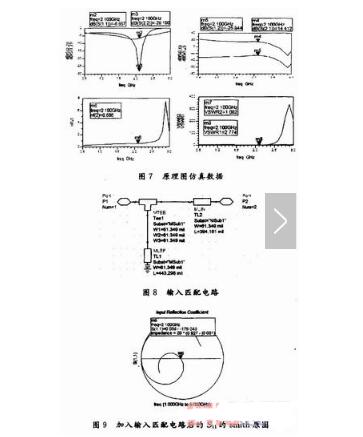

观察最后的仿真结果可以看到,增益为14.4 dB;噪声系数为0.586,这与稳定后的晶体管最佳噪声系数0.573非常接近,且增益平坦度低,稳定性能优异。具体性能指标如图7所示。

3、以噪声系数为主兼顾增益为设计目标方案的仿真

3.1、输入匹配电路设计

如果选择基板材料为环氧玻璃FR-4基板,介电常数为4.3,厚度为0.8 mm,则2.1 GHz时的晶体管输入阻抗为1 6.827-j16.041。采用上述匹配电路生成方法,输入匹配电路采用ADS设计向导中的单支节模块来设计。可以很快得到图8中的匹配电路。如图9所示,图中m6=50(0.927+j0.001)。与50 Ω的非常接近,所以得出的输入端匹配情况比较合理。

3.2、输出匹配电路设计

在完成输入匹配电路设计之后,可以对输出匹配电路进行设计。在此充分发挥CAD软件的优势,借助优化的方法来实现。基本过程如下:

将输入匹配电路的结果添加到图10中,并在晶体管输出端添加如图所示的微带。调出优化控件,并将优化的目标设置为dB(S(11))为-20,dB(S(22))为-15。

在优化开始时,先将TL1,TL2,TL3宽度设置为61.394 mil,这是为了保障在考虑到板材、板材厚度等因素下微带线的特性阻抗为50 Ω。预设TL1,TL2,TL3的长度,优化一次后,刷新结果,观察各种图表的指标是否更好,数值是否达到设置的最大值,如果达到最大值,再次改变设置值重新优化。反复多次后,将会达到再次改变这几个数值,若改变后对于各种指标作用不大,可以尝试改变电阻和输入匹配的数值再进行优化。

通过多次调试发现,R1设为15 Ω,以及加上TL7后,增益和噪声系数以及输入输出驻波比效果更好。仿真电路原理图及优化控件和目标控件如图10所示。

3.3、仿真结果

观察最后的仿真结果可以看到,增益为15.816 dB;噪声系数为0.708,该指标均比定性分析时的都要好,其他性能指标如图11所示。

低噪声放大器设计实例

低噪声放大器的设计步骤

1、直流分析与偏置电路设计

2、稳定性分析

3、噪声圆系数与输入匹配

4、最大增益的输出匹配

5、电路整体微调

6、版图设计

一、直流分析与偏置电路设计

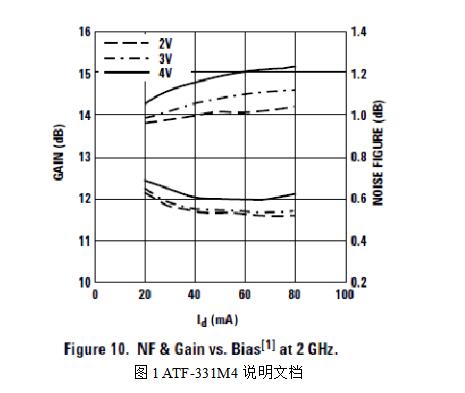

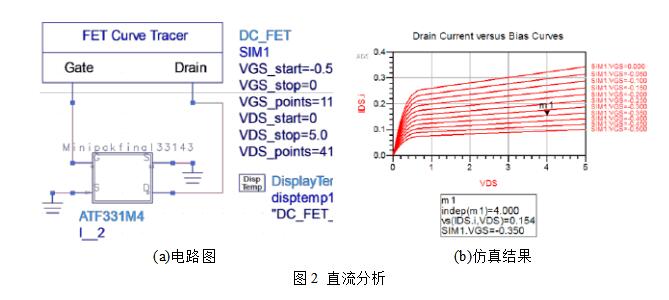

1、从ATF-331M4的说明文档如图1可以看出,2GHz下它在VDS为4V、Id为40-80mA时噪声系数在0.6左右,且增益去到15dB以上,符合设计要求。为使增益尽可能地大,故确定晶体管的偏置VDS=4V,Id=80mA; 2、从Avago的官网下载ATF-331M4的模型,并在ADS2015.01下如图2进行直流分析,以确定偏置VGS的电压。由于ATF-331M4有两个源端,为使每个源端电流为80mA,故应选择Id约为160mA的栅极电压。由直流仿真结果可得VGS约为-0.35V;

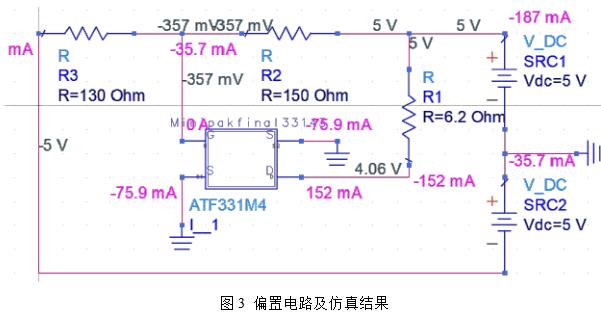

3、确定静态工作点后则可设计偏置电路。本来ADS中有一个“DA_FETBias”的控件工具可以方便地设计偏置电路,但由于需要将晶体管的栅极电压偏置于负电压,这个工具便难以胜任,故只能手动设计偏置电路。使用+5V和-5V的双电源和标称电阻值,可计算出分压器的两个电阻分别为130Ohm和150Ohm时栅极电压约为-0.35V。由于漏极电流约为160mA,要使漏极电压为4V时可计算出漏极电阻约为6.2Ohm。最后得到电路图及直流仿真结果如图3示。

二、稳定性分析

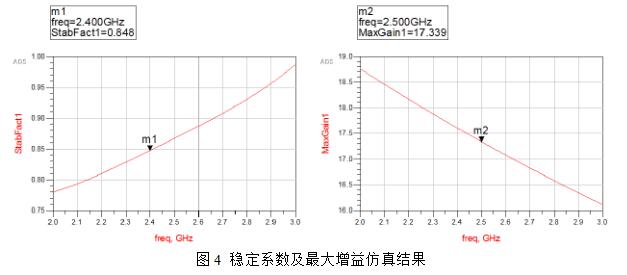

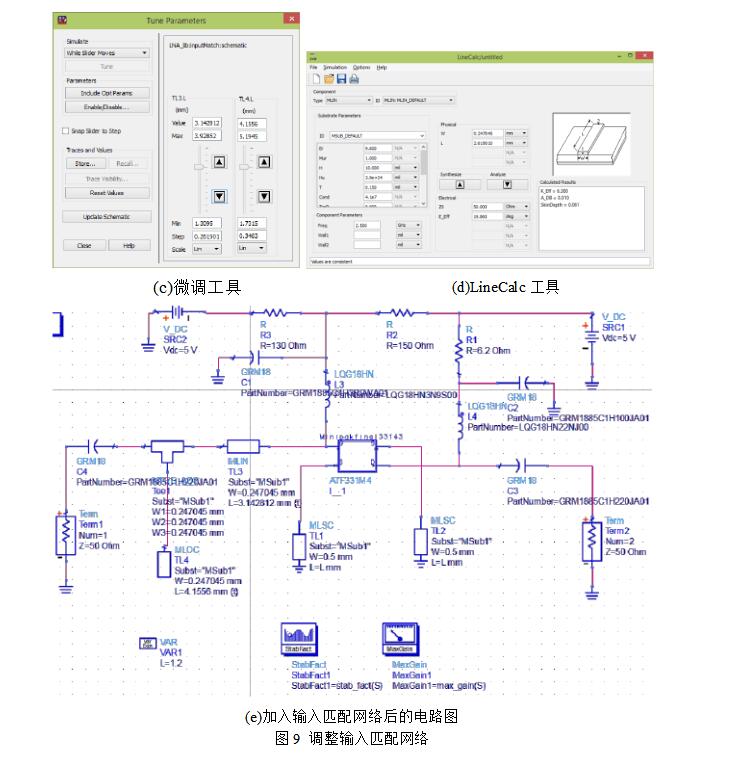

1、向电路图中加入3.9nH的扼流电感L1、L2,3.9pF的旁路电容C1、C2和22nH的隔直电容C3、C4后,再在输入和输出端加入50Ohm的Term控件,以及StabFact和MaxGain控件,进行S系数仿真。如图4可见此时稳定系数K在2.4GHz下为0.848,电路不稳定,同时电路在2.5GHz时MaxGain为17dB。

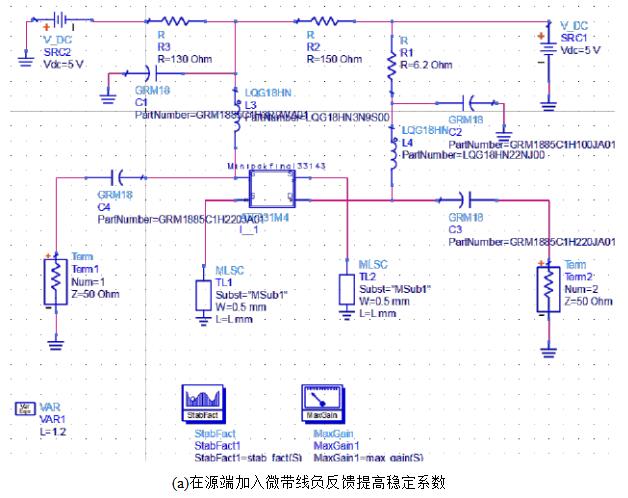

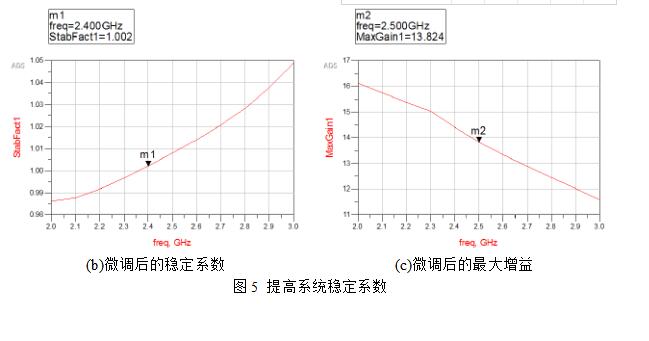

2、为使系统稳定,故如图5a在源端处添加微带线作电感引入负反馈。同时使用变量控件调节微带线的长度反复仿真。最后得到长度在1.2mm时稳定系数K在2.4GHz下为1.002,系统稳定,但MaxGain降低至13.8dB。

三、噪声系数圆和输入匹配

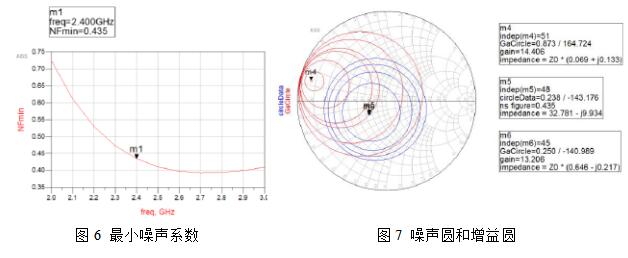

1、进行噪声仿真并画出NFmin参数,如图6可见在2.4GHz时NFmin为0.435dB。接下来就是要设计一个适当的输出匹配网络来实现最小噪声系数;

2、画出噪声圆和增益圆如图7所示。其中M4为增益最大的输入阻抗,增益为14.406;M5为噪声最小的输入阻抗,最小噪声系数为0.435dB。但两者并不重合,需要在这两者之间权衡考虑。对于低噪声放大器,尤其是第一级放大器,首要考虑的是最小噪声。所以选用M5点的阻抗即32.781-j9.934作为输入端的阻抗进行匹配。此时增益约为13.206dB,仍然符合设计要求;

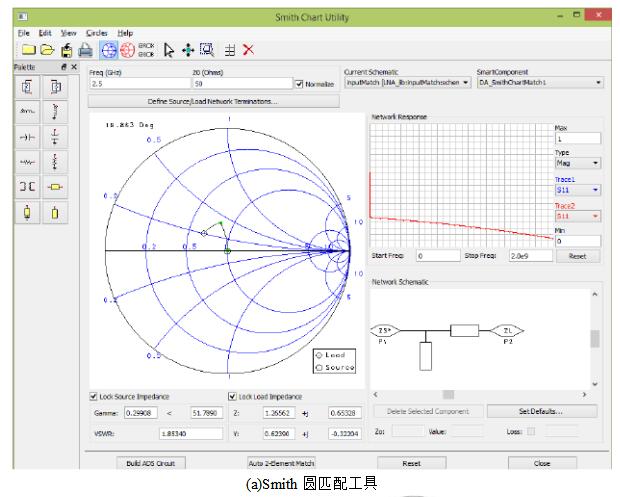

3、如图8使用Smith圆匹配工具DA_SmithChartMatch进行输入阻抗匹配,生成使用微带线的匹配网络。再次进行仿真,可见此时噪声圆的M5点正好匹配至50Ohm,且噪声系数nf(2)在2.4GHz下与NFmin相等,即噪声系数已经达到最优化;

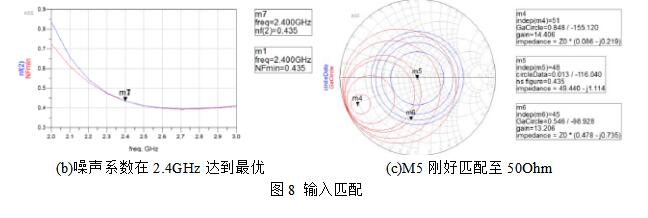

4、如图9将生成的匹配网络放进电路图中并移至隔直电容后,再使用LineCalc程序将微带线转换至实际长度后进行仿真。可见此时噪声优化点已偏离50Ohm,同时噪声系数nf(2)偏离最小噪声系数NFmin。故使用微调工具对输入匹配网络的微带线长度进行微调,使噪声系数达到最优。

四、最大增益的输出匹配

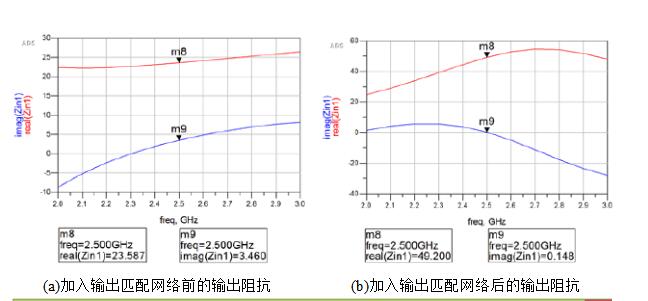

1、使用Zin控件测得输出阻抗如图10a为23.587+j3.46Ohm,即需要将输出阻抗匹配与50Ohm匹配;

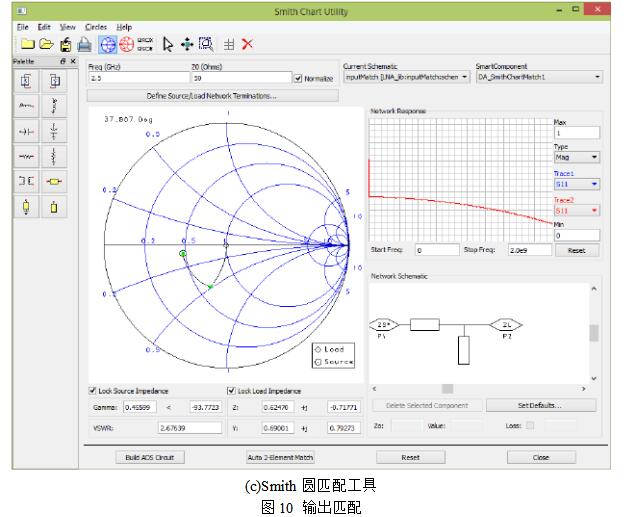

2、如图10c使用Smith圆匹配工具DA_SmithChartMatch进行输出阻抗匹配,生成使用微带线的匹配网络。再次进行仿真,图10b可见此时输出阻抗已非常接近50Ohm;

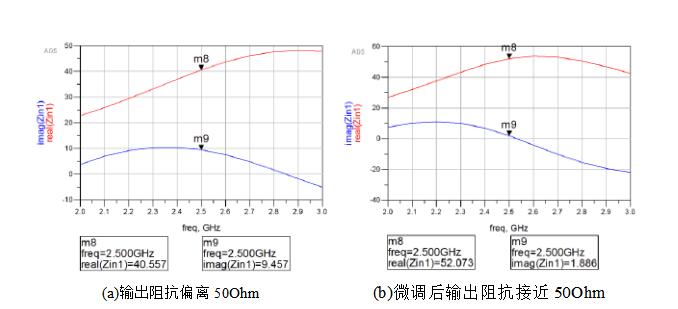

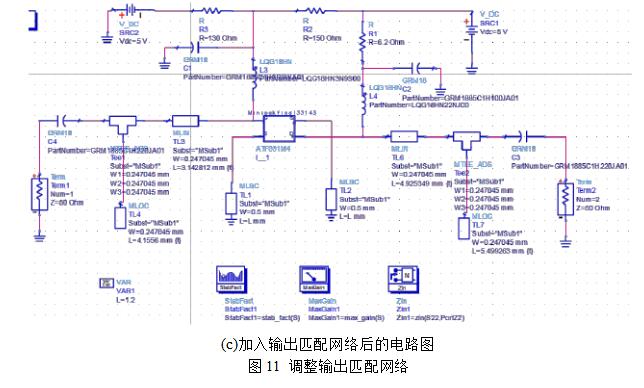

3、如图11将生成的匹配网络放进电路图中并移至隔直电容前,再使用LineCalc将微带线转换至实际长度后进行仿真。此进输出阻抗已偏离50Ohm。故使用微调工具对输出匹配网络的微带线长度进行微调,使用输出阻抗接近50Ohm。

五、电路整体微调

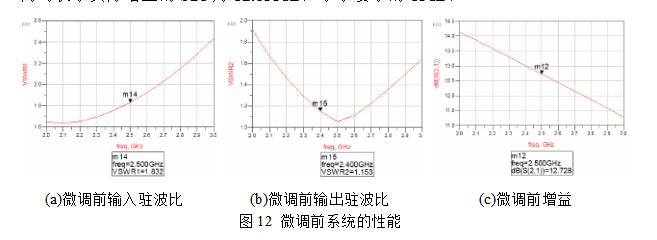

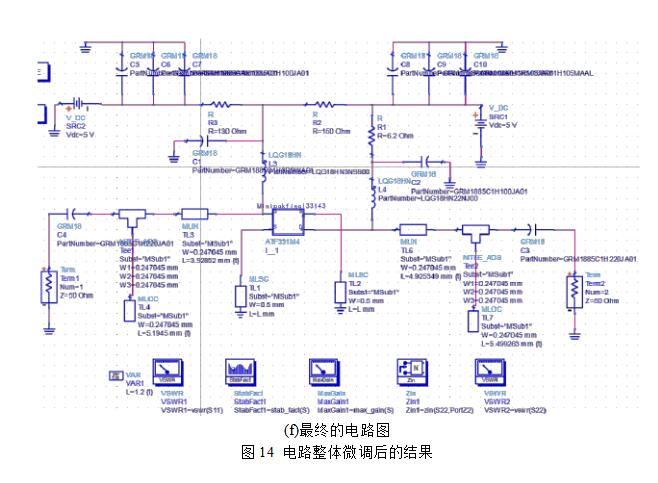

1、分别在正负电源处从电源开始加入1uF、0.01uF和10pF三个去耦电容后对电路进行仿真。图12可见输入驻波比VSWR(input)为1.832,大于1.5的设计要求,同时表示实际增益的S21为12.833dB,小于要求的13dB;

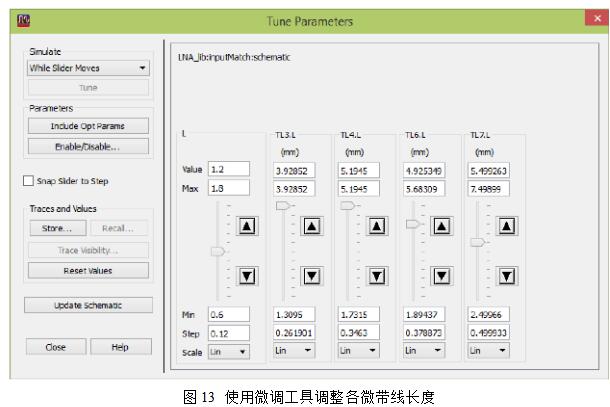

2、对电路微调的方法如下:

(1)增益和绝对稳定系数K值调节:主要调节源极负反馈微带线TL1和TL2。增益和绝对稳定系数是一对矛盾,调节负反馈时增益上升必然导致绝对稳定系数K值下降。所以增益和绝对稳定系数K做一个折中选择。但必须保证电路系统的稳定,即K》1。调节输入输出驻波比VSWR也会对增益有一些影响;

(2)输入驻波比VSWR(input)的调节:主要调节输入端匹配电路微带线TL3和TL4。为了降低VSWR(input),调节TL3和TL4时,让输入端的阻抗往50 Ohm 方向调节,使输入端反射系数最小,从而降低输入驻波比VSWR(input)。但对输入网络的调节会影响到噪声系数和增益;

(3)输出驻波比VSWR(output)的调节:主要调节输出端匹配电路微带线TL6和TL7。为了降低VSWR(output),应让输出端的阻抗往50 Ohm 方向调节,使输出端反射系数最小,从而降低输出驻波比VSWR(output);

(4)输入驻波比VSRW(input)和输出驻波比VSWR(output)的调节会相互产生影响;

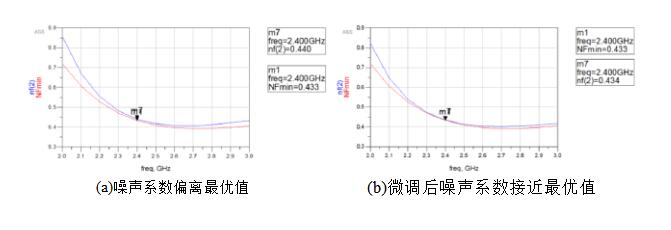

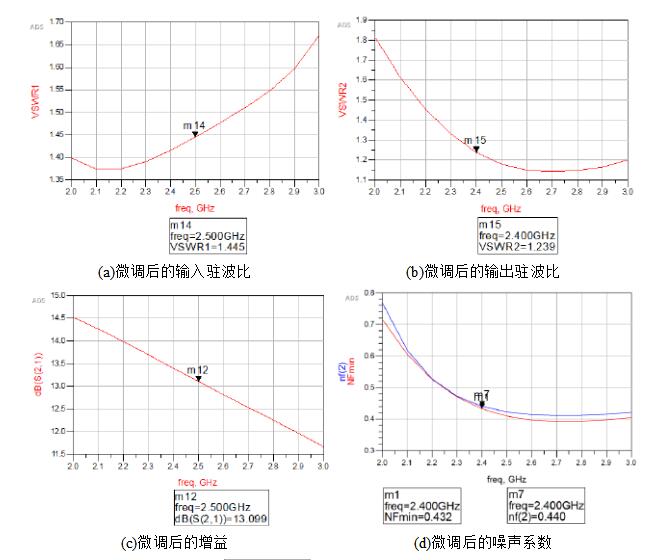

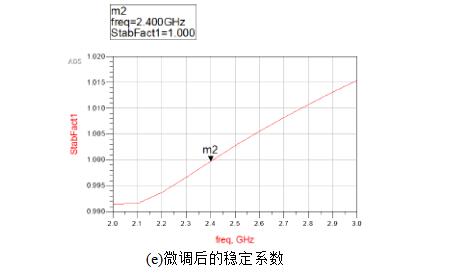

3、如图13对各微带线长度进行微调后最终得到的仿真结果如下。图14可见VSWR(input)为1.445,VSWR(output)为1.239,均小于1.5,代表实际增益的S21为13.099,噪声系数nf(2)为0.44,2.4GHz时的稳定系数为1.0,系统稳定,各参数都达到设计要求。

六、版图设计

1、由于ATF-331M4模型中不带版图,故需自行绘制。根据说明书中的尺寸数据,绘制晶体管的版图如图15所示;

2、将所有元件导入到版图中后手工布局和布线。分立元件之间的距离越小越好。最后得到版图如图16所示。

-

低噪声放大器设计的理论基础2009-10-20 6048

-

宽带低噪声放大器噪声分析2010-05-13 0

-

低噪声放大器,低噪声放大器型号参数2017-09-11 0

-

怎样设计和仿真低噪声放大器?有什么流程?2021-04-07 0

-

低噪声放大器介绍2021-07-27 0

-

利用Cadence设计COMS低噪声放大器2009-07-06 2859

-

低噪声放大器,低噪声放大器是什么意思2010-03-05 3711

-

Ku波段低噪声放大器的设计与仿真2011-10-13 914

-

RF低噪声放大器设计2017-11-23 3169

-

低噪声放大器设计资料2022-11-22 974

-

低噪声放大器简介2023-01-07 2015

-

低噪声放大器的设计原则2023-07-25 1928

-

低噪声放大器工作原理详解2023-09-05 4601

-

低噪声放大器放在哪里?低噪声放大器的作用是什么?2023-09-05 1720

-

低噪声放大器和高功放的区别2024-01-05 821

全部0条评论

快来发表一下你的评论吧 !