功放设计仿真的一般步骤

描述

功放设计仿真的一般步骤

1、首先需要确定放大器的特性指标,并根据指标选定合适的功放管。

2、将厂家提供的晶体管模型库导入到ADS模型库中。

3、根据放大器的要求和晶体管特性确定静态工作点。

4、进行功率放大器的电路设计,包括阻抗匹配、偏置电路等。

5、对所设计电路进行仿真,分析仿真曲线并得出结论。

6、优化功放电路结构和电路参数。

本次PA设计参数如下:

1 频率:960MHz

2 输出功率:10W

3 增益:18dB

4 效率:>30%

5 电源电压:28V

选择了飞思卡尔的功率管MW6S010N。

设计环境:使用软件ADS2009,安装了RF_POWER_ADS2009U1_DK(Designkit)安装飞思卡尔管子的Designkit。

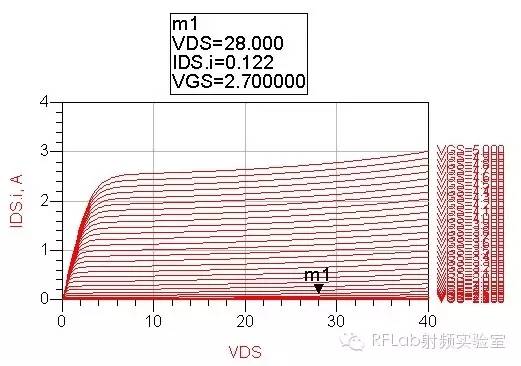

1、 直流扫描

首先对LDMOS管进行直流工作点扫描。根据Datasheet上的指标,得到当偏置为VDD=28V,VGS=2.7V时,IDQ=125mA。仿真结果如图1所示。

图1 功放直流扫描

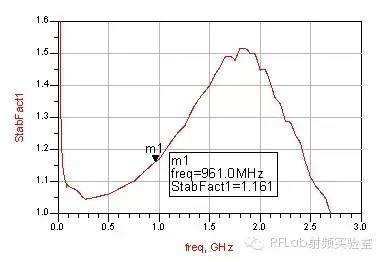

2、 偏置和稳定性分析

按照Datasheet设计功放的偏置电路[由于频率比较低,采用集总电感起到射频扼流的作用,用电容实现电源滤波

] ,然后,进行稳定性分析,从仿真结果图2,可见该器件在工作频段上绝对稳定,可以进行下一步的设计。

图 2 稳定性分析

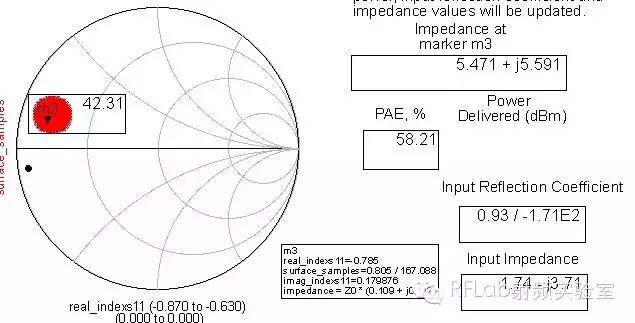

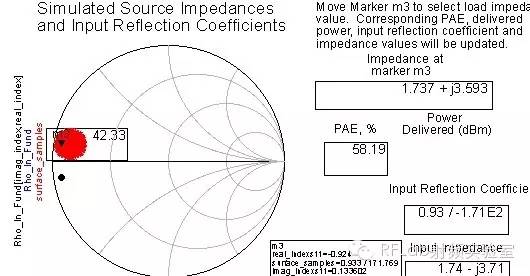

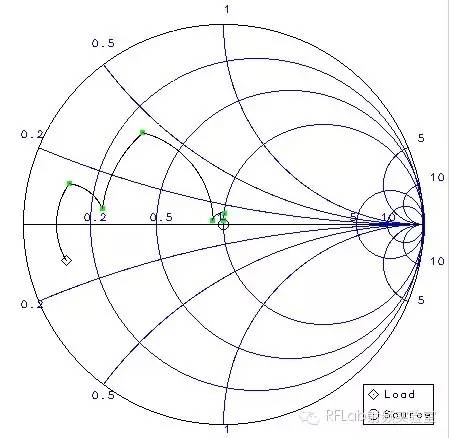

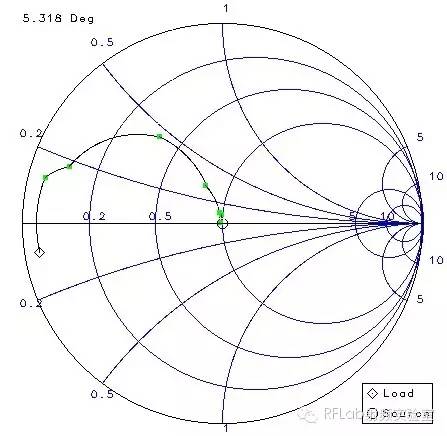

3、负载牵引和源牵引

我们对功放进行负载牵引和源牵引,设定匹配点阻抗960MHz,通过反复修改源和负载阻抗值[利用负载牵引的找到最佳负载阻抗,并将负载阻抗的匹配网络代入源牵引中,找到最佳源阻抗,并作源匹配网络,并将找到的最佳源阻抗的匹配网络再代入负载牵引中,如是反复调整,来找到最终的最佳源阻抗和负载阻抗] ,最终得到收敛,输入功率为23dBm,输出的最大功率值为42.31dBm。负载阻抗为5.471+j*5.591, 源阻抗为1.737+j*3.593,仿真结果如图3和图4所示。

图 3 负载牵引

图 4 源牵引

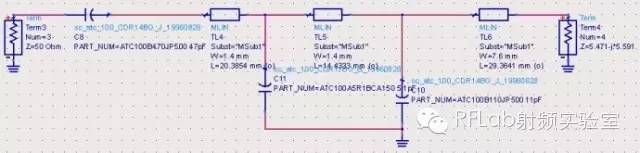

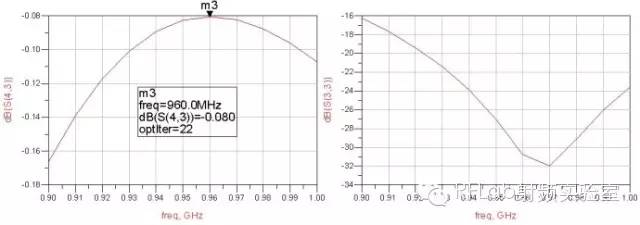

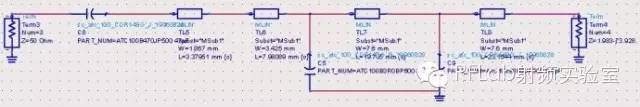

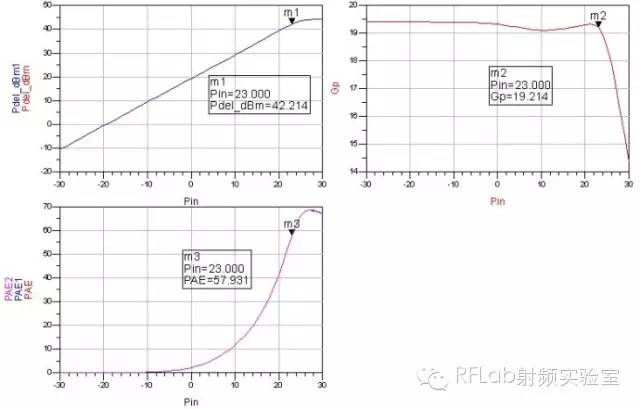

有了源阻抗和负载阻抗,然后利用ADS中的SmithChart工具进行匹配网络[考虑到功放的工作频段和调试的方便性,采用传输线和集总元件混合匹配网络,在Smith圆图上生成匹配电路。整个电路采用微带线作为传输线来实现,使用聚四氟乙烯玻璃纤维板(εr=2.55,h=0.5mm)] 的设计。首先,我们要使靠近功放管的传输线宽度大于功放管的引脚宽度。其次,我们要进行共轭匹配,所以要把SmithChart中的阻抗改为与源阻抗和负载阻抗共轭。最后,匹配电路的Q值尽量小。输出匹配电路的Smith圆图如图5所示。最后,将理想器件换成器件模型得到最终的匹配电路并进行优化,如图6所示,S参数的图如图7所示。输入匹配电路也按照这种方法设计。见图8-10。

图 5 输出匹配Smith圆图

图6 输出匹配电路

图 7 匹配电路S参数

图 8 输入匹配Smith圆图

图9 输入匹配电路

图 10 匹配电路S参数

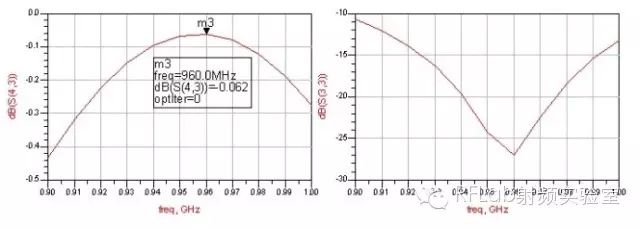

4、 谐波平衡仿真

现在可以把输入输出匹配电路与加了偏置电路的功放管连接起来,进行谐波平衡仿真。扫描输入功率为-30-30dBm,由图11可知,在输入功率为23dBm时的输出功率为42.2dBm、附加效率为57.549%、增益为19.2dB。

图 11 电路参数

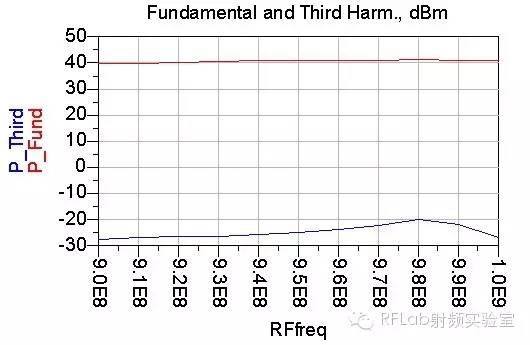

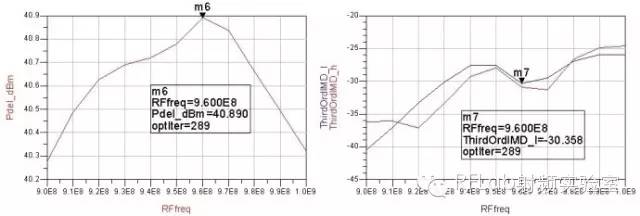

将优化后的原理图封装成一个模型,调用HB1ToneFPswp模板,测试IMD3的值,仿真得到输入22dBm时的输出功率如图12所示。

图12 HB1Tone频率扫描

然后进行HB2Tone仿真,由于只要求输出功率为10W,根据前面的仿真结果,功放在工作频段内增益为18dB,所以设置输入功率为22dBm;频率扫描为900MHz~1000MHz,双音间隔设置为100KHz。

图13 HB2Tone频率扫描

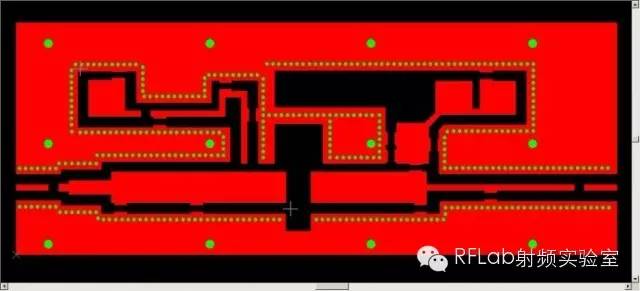

5、印刷电路版图

后面的工作就是将原理图生产印刷电路版图,自动生产的版图不符合我们的要求,我们需要自己进行调整。调整好后将文件导出成Gerber文件,然后再导入到Cam350中。完成的电路图如图14。

图14 印刷电路版图

板子加工完毕之后,就是调试的过程了。调试可能是个折中,妥协的过程,其涉及的方方面面就不在这里详述了。以仿真值搭建的电路不一定在实际测试中能达到仿真软件中的效果,但是正确的仿真却一定能为设计和调试指明方向。

-

mark点定位的一般原理与步骤2025-02-05 3379

-

pcb设计一般流程步骤2023-12-13 6194

-

开发java程序的一般步骤是2023-11-28 3152

-

EMC现场测试的一般步骤和注意事项有哪些?2023-06-26 3967

-

串口设置的一般步骤分享2022-02-22 1002

-

串口配置使用的一般步骤是什么2022-01-21 711

-

串口设置的一般步骤是怎样的?2021-12-16 1674

-

IO口配置的一般步骤是怎样的?2021-12-15 1489

-

UART配置的一般步骤是怎样的?2021-12-13 1502

-

串口配置的一般步骤是怎样的?2021-12-10 1266

-

串口配置的一般步骤有哪些2021-09-29 1302

-

dsp系统开发的步骤_dsp系统的一般设计过程2020-04-08 22302

-

仿真的一个简单的OTL电路,滑动变阻器一般是抑制交越失真的,可我的不管怎么调就是失真是什么原因?2018-07-25 6602

-

SIMULINK仿真的运行2008-06-19 5033

全部0条评论

快来发表一下你的评论吧 !