基于R/C滤波器DAC去干扰电路设计

模拟技术

描述

在路上似乎到处都有令人讨厌的减速带,在行车道和停车场,随处可见它们的身影。尽管它们的尺寸大小不一,但都一样不讨人喜欢。碰到这些减速带时,您可以选择减速通过以减少对车辆的磨损,也可以退回去,但最好的办法是绕过去。

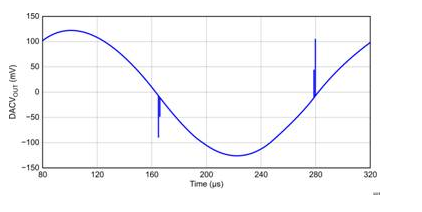

昨天,在我减速通过一条讨厌的减速带时,突然想到了我的那个精密型 16 位 R-2R DAC。它在中间刻度时存在短时脉冲波形干扰问题(请参见图 1)。我想,在选择使用具有较大短时脉冲波形干扰特性的 DAC 时,可以在 DAC 输出端添加一些去干扰电路,从而减少干扰的影响。两种常见的 DAC 去干扰电路是简单的低通滤波器(相当于一种减速方法),以及采样/保持电路(相当于“绕过”干扰)。这两种去干扰电路都可以降低干扰振幅,或者去除干扰能量。

图 1 16 位 DAC 产生的讨厌干扰

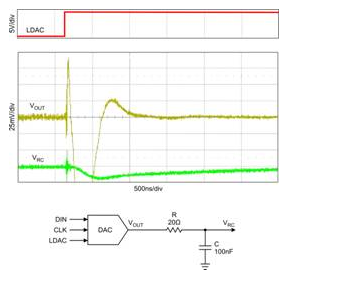

最简单的 DAC 去干扰方法是在 DAC 放大器输出端 (VOUT) 使用一个 R/C 滤波器(图 2 底部)。这种滤波器可以降低干扰的振幅,但增加了建立时间。

图2顶部的曲线为DAC负载DAC(LDAC)引脚的信号。利用DIN(数据输入)引脚和CLK(时钟引脚),便能够以串行方式将一个数据字载入到 DAC 中。一旦DAC 有了全部的数据,LDAC 引脚的升沿便将数据字载入内部 DAC 寄存器。这样便改变了 DAC 输出电压。中间的曲线表示测得的 DAC 输出中间刻度模拟干扰。底部曲线表示使用一个 R/C 低通滤波器后测得的模拟信号。

图 2 R-2R DAC8881 (Vref = 5V, AVDD = 5V) 中间刻度转码

一般而言,这个过程会比较顺利。在您增加(或者减小)数据码值时,输出电压也随之上升(或者下降)。但在四分之一和四分之三中间刻度处,DAC 会产生干扰。中间刻度干扰最大。

要想确定正确的 R/C 比,首先要查看干扰时间,然后给您的滤波器选择一个 3dB点,其比干扰频率低 10 倍左右。

例如,图 2 中干扰时间约为 1 μsec,经过转换得到 1 MHz 干扰时间。由这种估算,我们知道图 2 中的 R/C 值构建了一个 80 kHz 低通滤波器。在选择您的 R/C 值时,请确定 R 足够的低,以避免出现载入误差。

这种 R/C 滤波器解决了 R-2R DAC 干扰问题,但它也并非是一顿“免费的午餐”。正如您在图 2底部曲线所看到的那样,R/C 滤波器延长了 DAC 的建立时间输出信号。

根据您不同的应用要求,简单的R/C滤波器都可以奏效。如果系统要求一个有干扰问题的R-2R DAC,则开关电容解决方案结合 R/C 滤波器可能会是一种解决方案。

-

rc滤波电路中R越大越好吗2024-09-18 2497

-

基于Matlab带阻滤波器电路设计2023-11-20 518

-

干扰滤波器的种类_干扰滤波器怎么装2023-02-23 1806

-

电磁干扰(EMI)滤波器电路.zip2022-12-30 1096

-

《测量电子电路设计-滤波器篇》2021-12-30 1985

-

如何利用R/C滤波器实现DAC去干扰电路?2021-06-08 2336

-

如何去设计并实现抗干扰滤波器?2021-04-28 1726

-

如何使用RC滤波器实现DAC去干扰电路2020-07-31 1100

-

基于RC滤波器的DAC去干扰电路2019-06-20 2476

-

电子滤波器电路图大全(七款电子滤波器电路设计原理图详解)2018-03-26 70445

-

电磁干扰滤波器原理电路设计2014-08-22 4317

-

利用RC滤波器实现DAC去干扰电路2012-01-04 4921

-

电磁干扰滤波器电路2009-12-07 4351

-

滤波器电路设计2009-05-07 1423

全部0条评论

快来发表一下你的评论吧 !