I2C串行EEPROM存储器应用的软硬件处理措施

存储技术

描述

I2C串行EEPROM存储器因具有外形体积小、接口紧凑简单、占用引脚资源少、数据保存可靠、可在线改写、功耗低和价格低廉等显著特点,被广泛应用于嵌入式控制系统中,用于存放配置参数、调整和运行数据等信息。但由于其为同步串行传输,通讯协议非常简单,没有提供更为复杂的纠错和检测机制,在实践中经常因使用不当造成数据丢失、数据无故改写等问题。对于存储数据要求非常高的系统, 例如计量产品、无人值守系统等,如果存储数据发生意外错误,造成的损失是致命的,因此在设计使用I2C串行EEPROM存储器时,更多地需要硬件和软件相互接合,采取一些相关的处理措施,使得产品能够在各种恶劣的使用环境中可靠、正确地运行。

1 硬件处理措施

硬件处理过程中,应重点考虑以下几个方面:

(1)电源是一个控制系统可靠运行的基石,很多产品与外界的有线连接就是电源连接。因此,在产品设计时应对电源电路进行有效滤波处理,并且应该通过EMC的试验检测来降低电源纹波噪声,抑制高频震荡和高压脉冲的侵入,减少由于噪声过大而引起的I2C串行EEPROM器件读写失误。这一点尤为重要,因为实践中很多系统的数据不知何故而发生了错误,可能的一个重要原因就是电源的抗干扰能力有限,从而导致I2C总线干扰。

(2)由于特殊原因,尽管对电源已经进行了有效处理,仍无法避免电磁的干扰,在使用I2C串行EEPROM时,在I2C规范限制条件下,可以采取减小上拉电阻和使用I2C总线驱动器提高输出驱动能力等措施来有效降低电磁干扰对读写的影响。

(3)I2C串行EEPROM 一般具有欠压复位电路,如果微处理器欠压复位的门限电压高于I2C串行EEPROM,那么,由于电磁干扰造成的电压波动使得微处理器可能会在总线通信过程中率先复位,而I2C串行EEPROM保持其当前状态,导致总线出现“挂死”现象,使得数据传输不同步而出现数据错误。因此,应尽量采用带有掉电检测功能的微处理器,设置微处理器掉电复位门槛电压低于I2C串行EEPROM 的欠压复位门槛,使得微处理器与I2C串行EEPROM同步复位[1]。

(4)为防止总线意外“挂死”,如果设计允许,最好能控制I2C器件的电源或选择带有复位引脚的器件。

(5)对于具有写保护功能的I2C串行EEPROM,可充分利用写保护引脚来提供硬件写保护功能,将写保护引脚连接到微处理器的I/O口线上,控制器件在平时处于写保护状态;需要写入时,将写保护引脚变为逻辑“0”。注意,写保护引脚不能悬空,否则器件将无法正常工作。

2 软件处理措施

在保证硬件电路设计可靠的同时,提高软件的抗干扰能力同样重要。在对I2C串行EEPROM进行读写操作时,要从两个方面进行可靠性的设计,首先要保证I2C总线通讯的完整和有效性,其次就是保证I2C串行EEPROM读写数据的正确性。

2.1 保证 I2C总线通讯的完整和有效性措施

2.1.1 总线复位

前面讲到在I2C总线通讯过程中,由于电磁干扰等因素可能导致总线“挂死”或通讯失效,所以在启动通讯前,应先对I2C串行EEPROM器件进行复位操作,以保证I2C总线处于畅通状态。对于具有复位引脚的器件,提供复位信号重新复位;而对于无复位引脚的器件,若电路设计中能控制其电源,则给器件上电复位;若无法控制器件电源,则启动“恢复序列”复位。恢复序列操作流程为:

(1)在SCL线发送9个时钟脉冲;

(2)由Master保持SDA线为高,直到Slave-Transmitter模式释放SDA执行ACK操作;

(3)在ACK操作时,保持SDA线为高;

(4)在Master-Receiver和Slave-Transmitter模式都结束后,Master发送一个Stop命令完成初始化总线[1]。

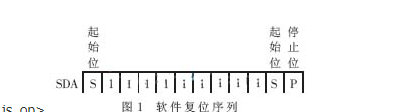

恢复序列如图1所示。

-

AS32X601的I2C模块操作EEPROM详解2025-12-21 1595

-

I2C总线介绍 I2C读写时序介绍2023-10-01 6322

-

I2C串行总线协议是什么?I2C总线有哪些优点?2023-09-12 3259

-

使用I2C读取24cxx串行EEPROM2022-06-30 836

-

使用MSSP模块进行I2C串行EEPROM与PIC16器件的接口设计2021-05-11 1206

-

使用单片机实现I2C存储器设计的中文硬件字库应用的C语言实例2021-03-31 1126

-

嵌入式控制系统中I2C串行EEPROM器件会有什么问题?2020-04-08 1917

-

I2C串行EEPROM的详细中文使用手册详细中文概述2018-06-19 1708

-

使用硬件模块实现8051 MCU与I2C™串行EEPROM的接口2018-03-29 909

-

串行EEPROM存储器及应用2016-12-11 1038

-

I2C串行EEPROM系列中文资料,数据手册2009-07-12 1090

全部0条评论

快来发表一下你的评论吧 !