RZ/G2L高速虚拟串口方案 基于瑞萨RZ/G2L SMARC开发板的虚拟(Virtual UART)实现方案

接口/总线/驱动

描述

RZ/G2L具有丰富的外设,比如千兆以太网,CANFD以及丰富的UART接口,可以满足工业数据收集处理相关的应用。本文主要介绍基于瑞萨RZ/G2L SMARC开发板的一种虚拟(Virtual UART)实现方案,以实现高速Linux UART通信,供客户参考。

虚拟(Virtual UART)方案介绍

很多工业客户,都有Linux下高速UART需求(1Mbps以上波特率),但是RZ/G2L的UART(SCIg,SCIF)在Linux环境下,由于Linux操作系统本身实时性以及硬件FIFO等限制,运行在1Mbps以上波特率时,很容易出现数据丢失,帧错误等异常,而且不太容易解决。考虑到RZ/G2L集成了200MHz的CM33实时CPU核,可以用于执行实时性要求比较高的任务,所以,可以使用CM33小核管理UART硬件模块,同时通过MHU模块跟Linux端CA55大核进行通信,实现虚拟串口方案。Linux端UART应用程序,可以不用修改直接访问对应的虚拟串口设备(/dev/ttySCx)。

具体方案已经在开发板上面实现并测试通过,SCIF可以稳定工作在10Mbps波特率,没有FIFO的SCIg可以稳定工作在1Mbps,而且SCIg支持8和9-bit数据帧,SCIF仅仅支持8-bit数据帧。这种配置可以满足很多需要高速UART的工业客户需求。

复制链接查看关于Github的更多内容:

Github

renesas-rz/rz-virtual-uart: SubCore based UART solution for Linux UART application. Baudrate can be up to 10Mbps. (github.com)

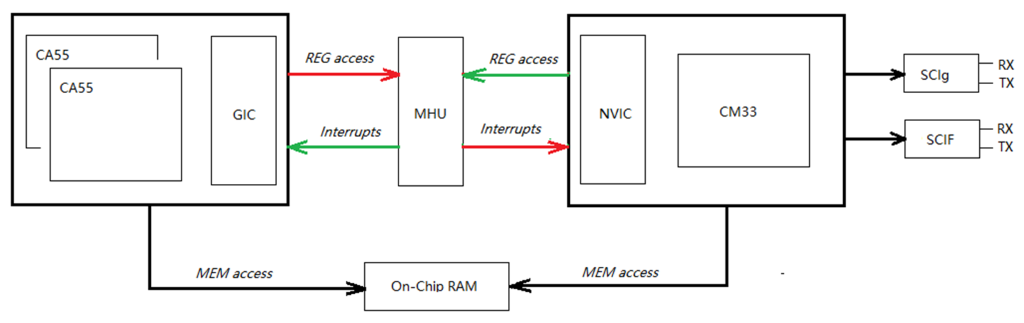

这里,简单介绍一下方案基本实现方式。系统框图如下:

系统框图

RZ/G2L MPU里面集成的MHU模块,可以用于CA55大核和CM33小核之间相互触发外部中断,配合共享内存,可以用于实现UART数据通信。由于MHU硬件资源限制,只能由CM33最多管理两路UART设备:

● SCIg x1 + SCIF x1

● SCIg x1 + SCIg x1

● SCIF x1 + SCIF x1

● SCI x1

● SCIF x1

RZ/G2 产品介绍

RZ/G2L是一款通用MPU,配备双核Arm Cortex-A55 CPU和单核Cortex-M33 CPU,具有3D图形和视频编解码器。采用多核异构的处理器架构,A55 CPU跑Linux操作系统处理复杂控制任务,M33核跑RTOS操作系统处理实时任务。核间通过OPENAMP实现通信。

主要功能

● 2xCortex-A55 (1.2GHz), Cortex-M33 (200MHz)

● 16-bit DDR3L/DDR4-1600 (in line ECC)

● 摄像头接口; MIPI CSI-2 (4 lanes) or Parallel

● 显示接口; MIPI DSI (4 lanes) or Parallel

● 3D图形加速(Arm Mali-G31)

● H.264 codec (RZ/G2L only)

● 丰富连接性及外设:2xGigabit Ethernet,2xCAN-FD,8xADC,7xUART

产品应用

● 家用电器、工业HMI

● 对讲机/门铃、智能摄像头

● PLC、数据集中器等

-

Renesas RZ/G2L, RZ/V2L SMARC模块板硬件设计解析2025-12-30 1644

-

RZ/G2L串口SCI的使用(下)2024-08-03 1398

-

RZ/G2L串口SCI的使用(上)2024-07-25 1448

-

瑞萨RZ/G2L串口SCI的使用(上)2024-01-17 3053

-

【米尔瑞萨RZ/G2L开发板-试用体验】认识一下米尔瑞萨RZ/G2L开发板的核心板2023-07-29 7489

-

【米尔瑞萨RZ/G2L开发板-试用体验】米尔瑞萨RZ/G2L开发板使用SSH登录2023-06-11 7780

-

米尔瑞萨RZ/G2L开发板 安装交叉编译器2023-05-26 3929

-

米尔瑞萨RZ/G2L开发板 TF卡读写速度测试2023-05-22 2788

-

米尔瑞萨RZ/G2L开发板-初体验2023-05-15 2283

-

【米尔瑞萨RZ/G2L开发板-试用体验】开箱2023-05-14 3603

-

RZ/G2L、RZ/V2L SMARC 模块板用户手册:硬件2023-01-09 554

-

【飞凌RZ/G2L开发板试用体验】+01.开箱(zmj)2022-08-28 1449

-

基于瑞萨电子RZ/G2L的FET-G2LD-C核心板和OK-G2LD-C开发板评测2022-05-30 2199

全部0条评论

快来发表一下你的评论吧 !