浮栅晶体管的组成结构以及原理

描述

浮栅晶体管主要是应用于于非易失性存储器之中,比如nand flash中的基本单元,本文介绍了浮栅晶体管的组成结构以及原理。

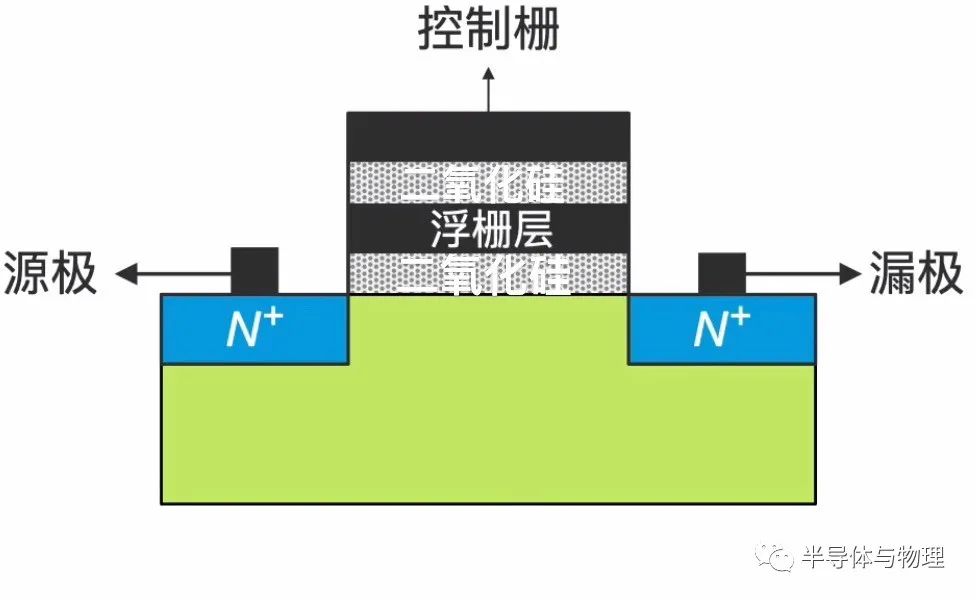

上图就是浮栅晶体管大致的组成图,是在NMOS的基础上在控制栅极下的绝缘层之间加入了一层浮栅层,用于储存电子。 其中与沟道接近的绝缘层二氧化硅厚度比较薄,电子在比较大的电场作用下,会隧穿进入浮栅层。

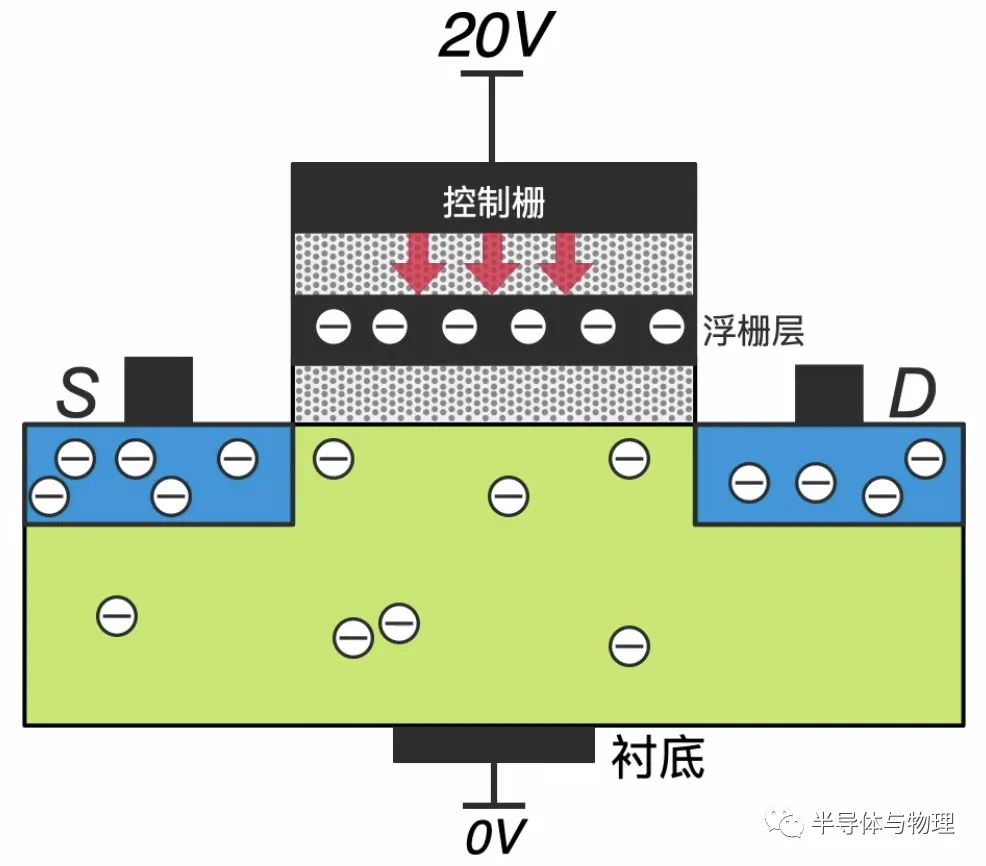

在写入电子时,在控制栅极施加相对于衬底的高压时,离子阱的电子被吸引并隧穿进入浮栅层被存储在其中,如果撤销电压之后,因为浮栅层被绝缘层包裹,浮栅层电子还是存储在这个部位,此状态计为逻辑0。

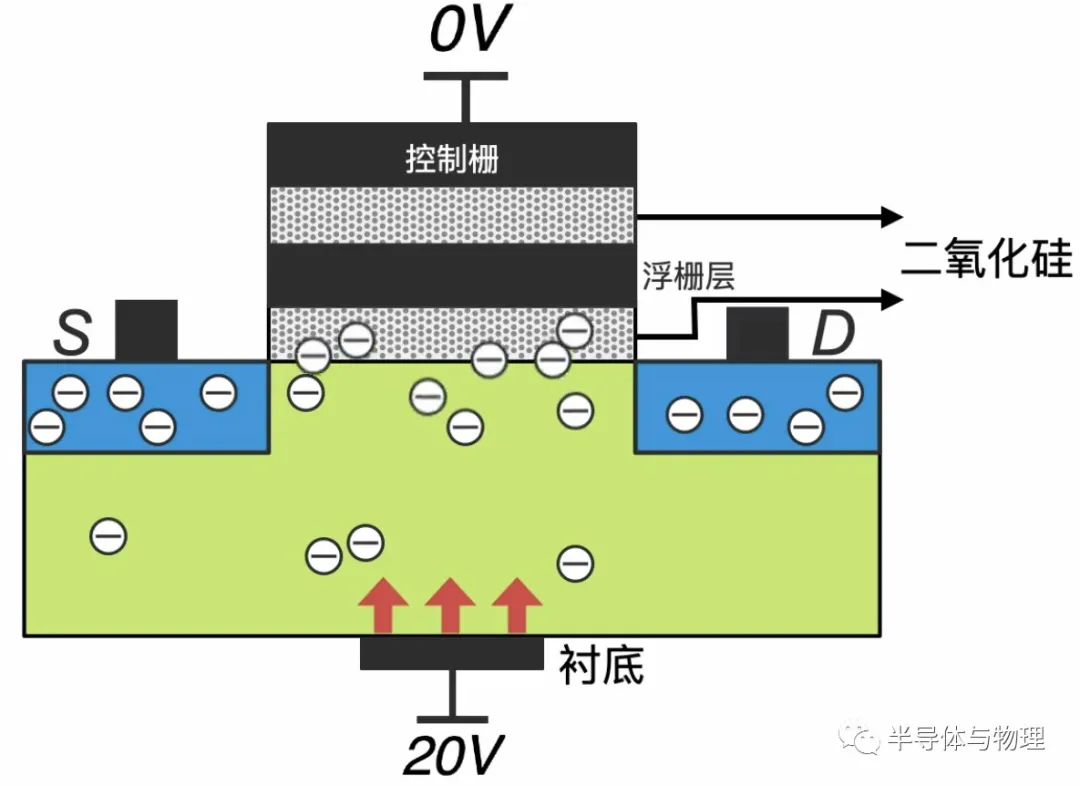

在擦除电子时,需要在衬底加一个相对于栅极的高压,浮栅层存储的电子就会在电场作用下隧穿回到下面的P型半导体里。此状态计为逻辑1。 浮栅晶体管巧妙的使用了物理里非常奇特的量子隧穿,用电场控制电子的存储,是一类很重要的存储器件。 END 转载内容仅代表作者观点 不代表中国科学院半导体所立场

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

绝缘栅双极晶体管的工作原理和结构2024-02-27 6735

-

绝缘栅双极晶体管(IGBT)2012-08-02 2882

-

绝缘栅双级晶体管IGBT2012-08-20 3519

-

晶体管的结构特性2013-08-17 3824

-

IGBT绝缘栅双极晶体管的基本结构与特点2019-03-27 2444

-

IGBT绝缘栅双极晶体管2019-05-06 2169

-

场效应晶体管的分类及作用2019-05-08 4257

-

如何去使用绝缘栅双极型晶体管IGBT呢2021-11-02 2547

-

绝缘栅双极晶体管(IGBT)2009-04-14 7484

-

绝缘栅双极晶体管IGBT2009-05-12 1846

-

绝缘栅双极晶体管原理、特点及参数2009-10-06 7157

-

绝缘栅双极晶体管2009-11-05 770

-

联栅晶体管(GAT)是什么意思?2010-03-05 3677

-

3D-NAND浮栅晶体管的结构解析2024-11-06 5090

全部0条评论

快来发表一下你的评论吧 !