ADC噪声系数对射频接收器的影响

描述

在上期中,我们介绍了控制 PFC 并实现单位功率因数的新方法。

本期,为大家带来的是《ADC 噪声系数如何影响射频接收器设计》,我们将深入探讨如何计算射频采样 ADC 的噪声系数,并说明 ADC 噪声系数对射频信号链设计的影响。

引言

为了制造更小的数字接收器,航天和国防工业采用了现代直接射频 (RF) 采样模数转换器 (ADC)。这些 ADC 消除了射频混合级,并更靠近天线,从而简化了数字接收器设计,同时还节省了成本和印刷电路板 (PCB) 面积。

一个关键(经常被误解的)参数是 ADC 噪声系数,该参数设置用于检测极小信号的射频增益量。本文介绍了如何计算射频采样 ADC 的噪声系数,并说明了 ADC 噪声系数对射频信号链设计的影响。

为什么噪声系数

在数字接收器设计中很重要

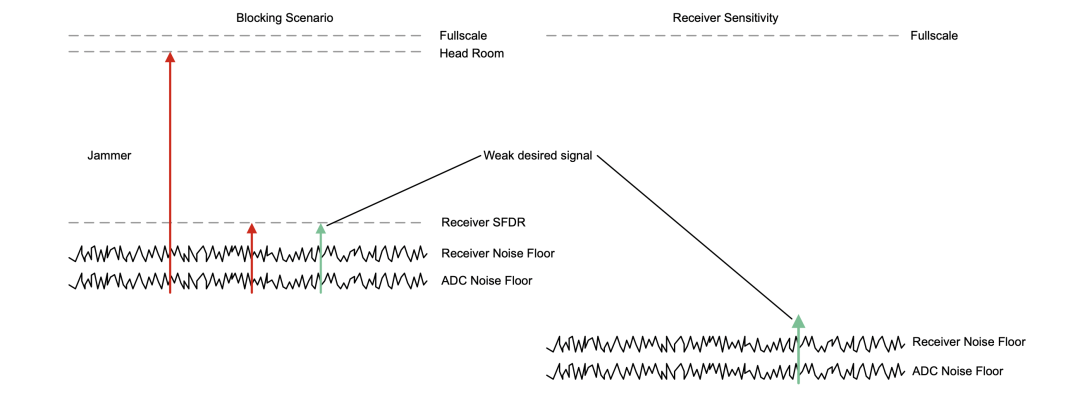

数字接收器在两种不同场景下工作,如图 1 所示。在阻断情况下,存在干扰或干扰器,接收器必须以较低的射频增益运行,以免使 ADC 饱和。在此设置中,ADC 被干扰信号驱动至接近满量程;因此,ADC 的大信号信噪比 (SNR) 决定了可检测到的信号微弱程度。还有其他降级机制,例如相位噪声和无杂散动态范围。

在第二种场景中,不存在干扰。检测可能的最弱信号仅取决于接收器的固有本底噪声,这种情况通常以接收器灵敏度进行测量。噪声系数用于测量由接收器信号链中的元件引起的 SNR 降级。

图 1. 阻断或干扰情况与接收器灵敏度场景的比较

ADC 的噪声系数通常是接收器的薄弱环节(约为 25dB 至 30dB),而低噪声放大器 (LNA) 的噪声系数低至 <1dB。不过,可以通过使用 LNA 向模拟射频前端(靠近天线)添加增益来改善 ADC 噪声系数。1dB 接收器系统噪声系数和 2dB 接收器系统噪声系数之间的差异约为 20%。这种差异意味着噪声系数为 1dB 的接收器可以检测振幅大约弱 20% 的信号。在软件定义无线电 (SDR) 中,这意味着无线电输出功率降低,从而延长电池寿命,而在雷达中,这使得覆盖更远的距离成为可能。

SDR 或数字雷达中的现代接收器设计使用直接射频采样 ADC 来减小尺寸、减轻重量并降低功耗。该架构无需射频下变频混频级,从而简化了接收器设计。ADC 噪声系数越好,所需的增益越低,实现的节省越多。此外,使用更少的额外射频增益意味着当存在干扰时,需要降低的增益更小,并在接收器中保持更高的动态范围。

计算系统的噪声系数

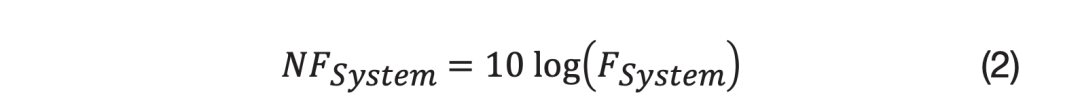

您可以使用 Friis 公式来计算接收器系统的噪声系数。假定一个具有两个放大器和一个 ADC 的简化的理想接收器,如图 2 中所示,方程式 1 按如下方式计算级联系统噪声因子:

方程式 1

其中 Fx 是噪声因子,Gx 是功率增益。

以分贝为单位的系统噪声系数为:

方程式 2

图 2. 典型接收信号链

此处需强调两个要点:系统噪声系数主要由第一个元件的噪声系数 F1 决定,前提是增益 G1 和 G2 足够大,以至于 ADC 噪声系数 F3 可以忽略不计。

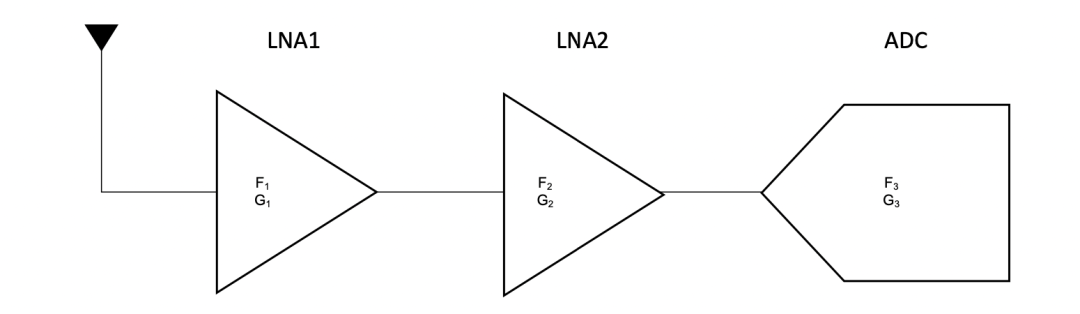

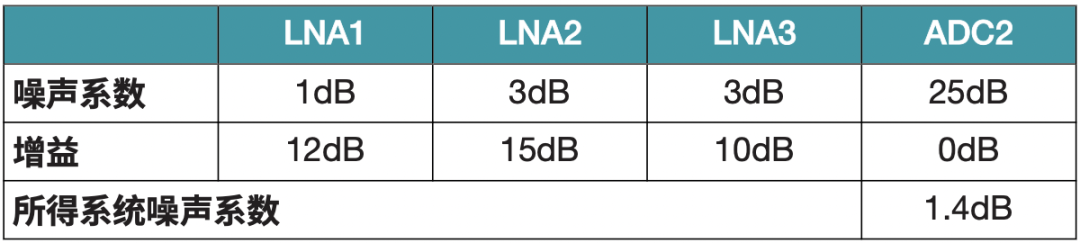

在具有两个级联 LNA 的系统中比较两个分别具有20dB 与25dB 噪声系数的不同 ADC,可以看出系统噪声系数有很大差异(请参阅表 1)。

表 1. 具有两个 LNA 级的系统噪声系数

如表 2 所示,将 ADC2 列中列出的系统(噪声系数相差5dB)设置为低于 2dB 的系统噪声系数,将需要使用第三个 LNA(噪声系数 = 3dB)额外增加 10dB 的增益。

表 2 突出了 ADC 噪声系数对整体系统噪声系数的影响。添加第三个 LNA 会增加成本、电路板面积(匹配元件、布线和电源)和系统功耗,并进一步降低满量程余量。

表 2. 使用 ADC2 且具有

三个 LNA 级的系统噪声系数

假设目标接收器灵敏度为 -172dBm,或非常弱的信号仅比绝对本底噪声高 2dB (-174dBm + 2dB = -172dBm),则该接收器需要优于 2dB 的噪声系数。在上面的示例中,我们使用 ADC1(噪声系数为 20dB,如表 1 中所列),级联系统噪声系数为 1.8dB。

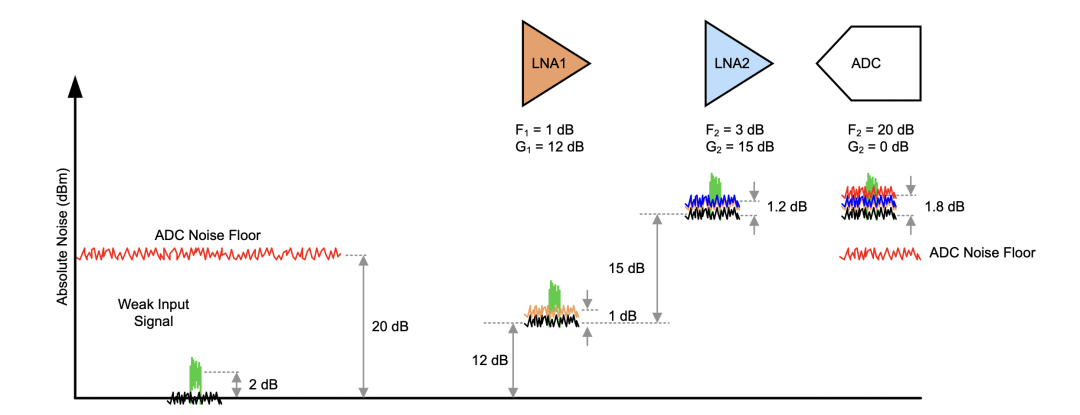

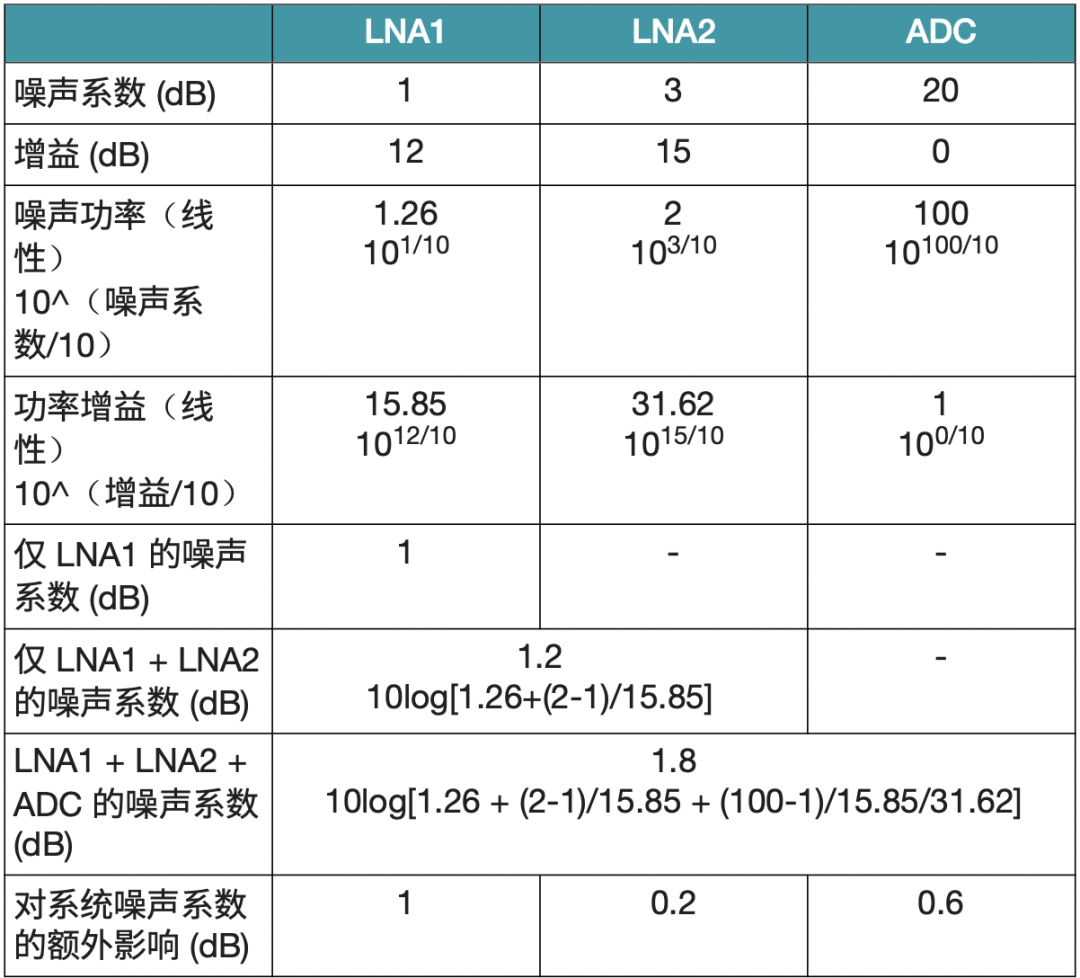

如图 3 和表 3 所示,增益为 12dB 的 LNA1 将输入信号和噪声提高 12dB,而将噪声系数降低 1dB(噪声系数 LNA1= 1dB)。LNA2 将信号和噪声提高了 15dB。尽管 LNA2 具有更高的固有噪声图 3dB,但由于 LNA1 的增益为 12dB,其影响仅降至 0.2dB。

最后,ADC1 的噪声分量(噪声系数 = 20dB)减少至仅 0.6dB,因为它会被两个 LNA 的 27dB 增益降低。因此,您最终会得到 1.8dB 的系统噪声系数,从而留下大约 0.2dB 的余量来检测微弱的输入信号。

图 3. 接收信号链中各个噪声系数贡献的图示

表 3. 计算各个噪声系数的贡献

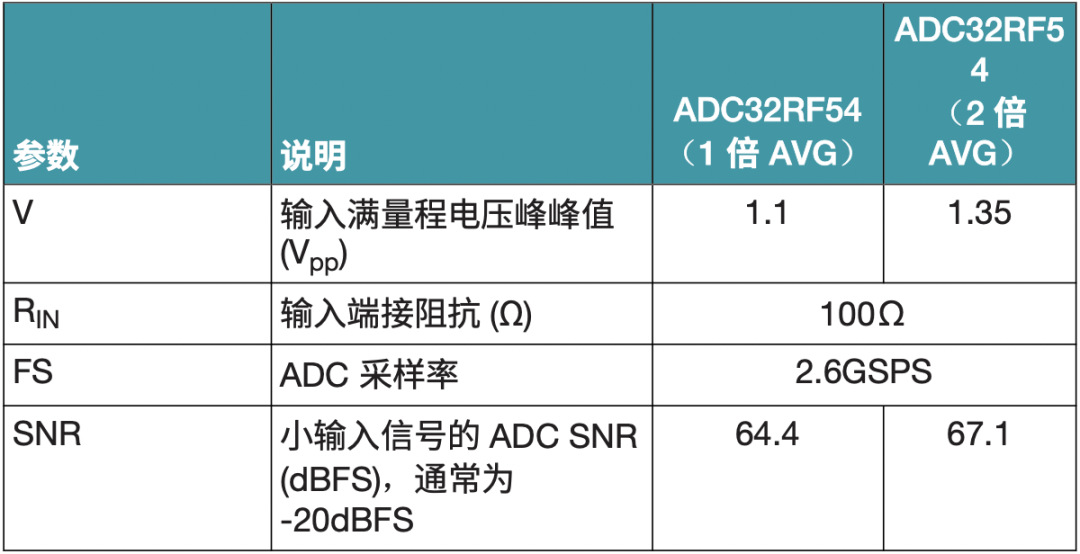

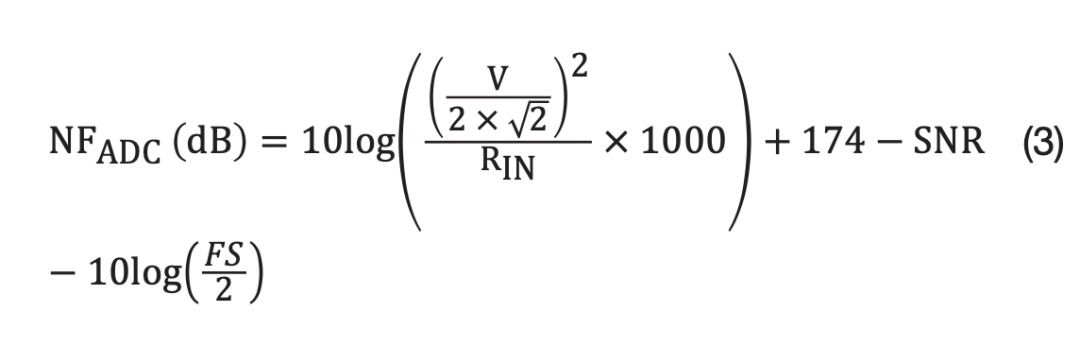

高速数据转换器很少在器件特定数据表中列出噪声系数。可以使用方程式 3根据 ADC32RF54 射频采样 ADC 的常用数据表参数(请参阅表 4)计算 ADC 的噪声系数。

表 4. ADC32RF54 的数据表参数

ADC Noise figure (dB) = PSIG,dBm + 174 dBm – SNR (dBFS) – bandwidth (Hz)

方程式 3

对于 ADC32RF54,噪声系数计算结果为:

噪声系数(1 倍 AVG)= 20.3dB

10log[(1.1/2/sqrt(2))2/100 x 1000] + 174 - 64.4 -10log[2.6e9/2]

噪声系数(2 倍 AVG)= 19.3dB

10log[(1.35/2/sqrt(2))2/100 x 1000] + 174 - 67.1 -10log[2.6e9/2]

结论

接收器噪声系数是一个重要的系统设计参数,因为它决定了最弱可检测信号。除了非常低的固有噪声系数外,ADC32RF54 还提供了高 SNR,即使在输入功率信号较大的情况下,也能让系统保持其噪声系数。具有相同噪声系数但 SNR 更低的 ADC 需要降低输入增益,以防止饱和,在这种情况下,ADC 噪声系数开始增加总体噪声。

-

计算ADC噪声系数需知2015-07-24 6956

-

如何用射频接收机测量噪声系数?这篇文章告诉你方法2017-12-26 11526

-

测量射频设备噪声系数的三种方法2023-08-30 9621

-

VNA的噪声系数是什么2019-03-25 2575

-

多通道射频接收机测量噪声系数的方法2019-06-03 2180

-

如何进行噪声系数测量?2019-08-09 2658

-

手机接收通道噪声系数测试2009-10-31 586

-

频谱分析仪和噪声系数测量2017-12-05 1795

-

那些不可错过的ADC噪声系数详解2018-04-11 9485

-

ADC噪声系数的认识及其分析2018-03-29 4047

-

量化和热噪声如何确定ADC的有效噪声系数2023-02-24 3819

-

噪声系数测量方法和公式2023-03-03 10114

-

最经典的噪声系数测试方法—Y因子法2023-06-13 4968

-

噪声系数分析仪的工作原理 噪声系数分析仪的噪声系数2024-06-03 3004

-

噪声系数分析仪使用方法2024-10-09 1946

全部0条评论

快来发表一下你的评论吧 !