高K金属栅极的结构、材料、优势以及工艺流程

描述

本文简单介绍了高K金属栅极的结构、材料、优势以及工艺流程。

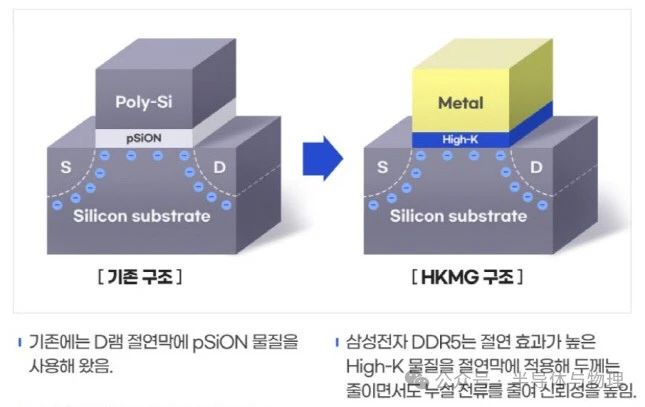

High-K Metal Gate(HKMG)技术是现代半导体制造中的关键技术之一,广泛应用于45nm、32nm、22nm及以下节点的高性能的逻辑芯片和DRAM。

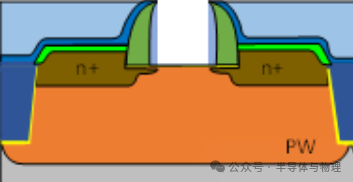

HKMG结构

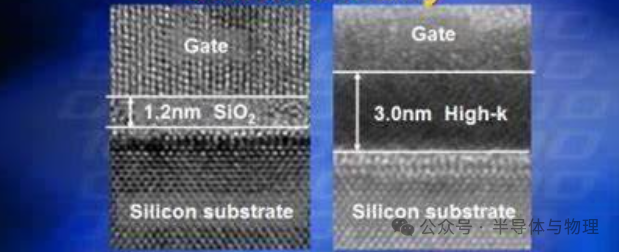

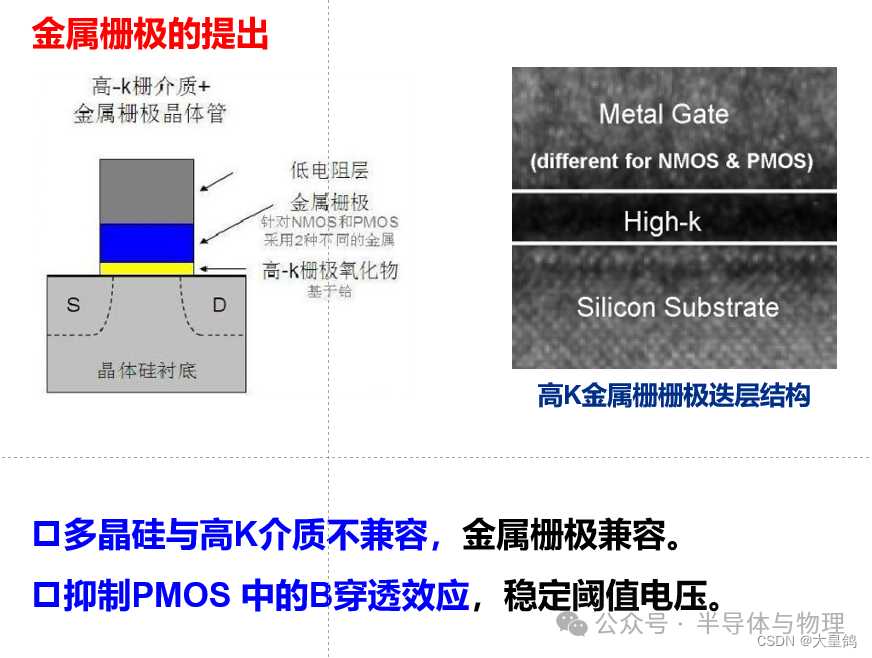

HKMG技术的核心在于使用高K材料替代传统的二氧化硅(SiO2)作为栅介质层,并使用金属材料替代多晶硅作为栅极电极。具体来说: 高K材料:高K材料具有较高的介电常数,可以有效减少栅极漏电流,提高晶体管的工作效率。 金属栅极:金属栅极材料具有良好的导电性和热稳定性,能够更好地控制阈值电压,提升器件的开关速度。

常用材料

高K材料:常见的高K材料包括铪基氧化物(如HfO2、HfSiO、HfSiON等)、铝基氧化物(Al2O3)、锆基氧化物(ZrO2)等。 金属栅极材料:常用的金属栅极材料包括钛氮化物(TiN)、钽氮化物(TaN)、钨(W)、钴(Co)等。

为什么需要HKMG

随着半导体器件尺寸的不断缩小,传统的SiO2/Si栅极结构面临诸多挑战,主要包括: 栅极漏电流过大:随着栅极厚度的减小,栅极漏电流显著增加,导致器件功耗增大。 阈值电压难以精确控制:多晶硅栅极在纳米尺度下难以精确控制阈值电压,影响器件的性能。 性能提升需求:高性能计算和低功耗应用对晶体管的开关速度和能效提出了更高的要求。 HKMG技术通过引入高K材料和金属栅极,不仅解决了上述问题,还进一步提升了晶体管的性能,使得更小、更快、更节能的电子设备成为可能。

为什么速度快

HKMG技术之所以能够提升晶体管的速度,主要有以下几个原因: 减少栅极漏电:高k材料(如HfSiON)具有较高的介电常数,可以在保持相同电容的情况下使用更厚的物理厚度,从而大幅降低栅极漏电,减少静态功耗。 增强栅控能力:高k材料允许使用更厚的栅极绝缘层,同时保持良好的栅控能力,提高晶体管的开关速度和能效。 改善载流子迁移率:金属栅极材料(如TiN)具有更优的功函数匹配,减少载流子在界面处的散射,提高载流子迁移率,增加导通电流(Ion),加快开关速度。

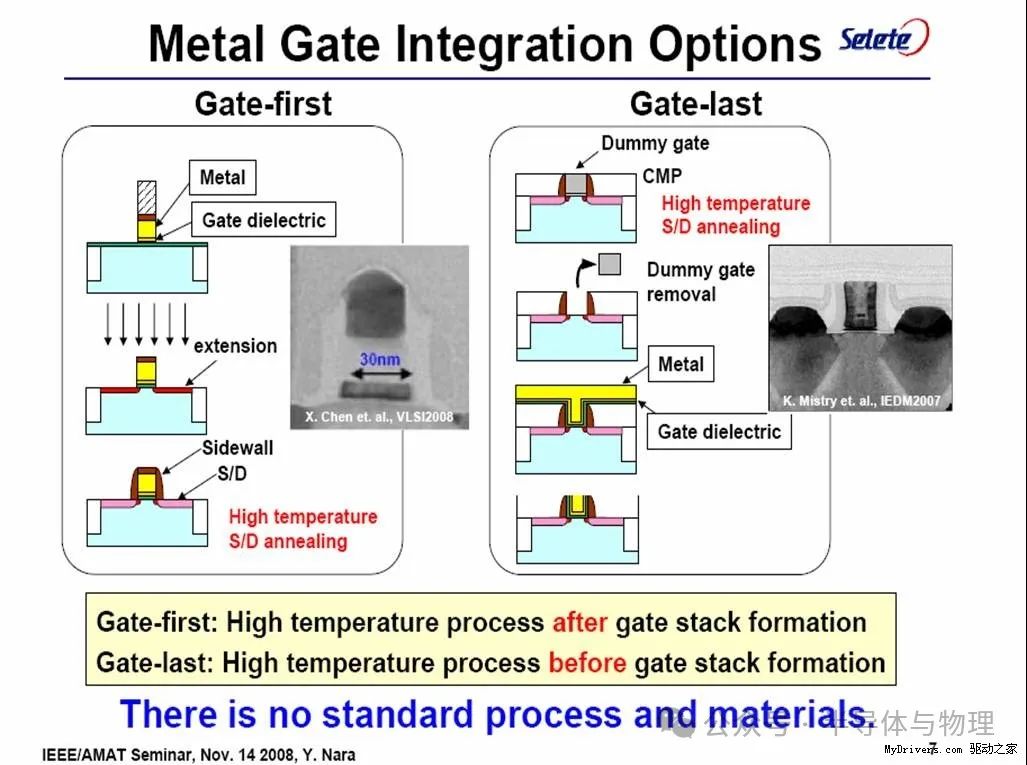

HKMG后栅工艺流程

HKMG技术的实现涉及多个复杂的工艺步骤,以下是一个典型的HKMG制程流程概述:

1.界面层沉积:

工艺技术淀积一层薄薄的SiON薄膜,目的是改善高K材料与衬底硅的界面态。

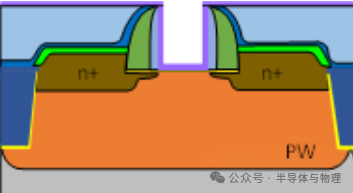

2.高K材料沉积: 通过金属有机化学气相沉积(MOCVD)淀积一层高K介质层HfSiO,然后再经过高温氮化形成HfSiON。

3.金属栅极沉积:

对于NMOS,通过原子层淀积(ALD)技术淀积厚度1nm的La2O3薄膜,形成覆盖层,目的是通过改变NMOS栅极的功函数来调节NMOS的阈值电压Vt。 通过ALD沉积厚度5nm~10nm的TiN金属覆盖层,形成金属栅,改善栅极多晶硅耗尽。 对于PMOS,通过ALD技术淀积厚度1nm的Al2O3薄膜,形成覆盖层,目的是通过改变PMOS栅极的功函数来调节PMOS的阈值电压Vt。 通过ALD沉积厚度厚度5nm~10nm的TiN金属覆盖层,形成金属栅,改善栅极多晶硅耗尽。

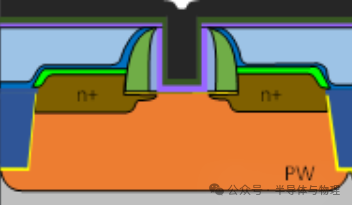

4.通过CMP进行平坦化,清除多余的金属: 通过光刻和刻蚀技术定义出栅极的形状和位置。

-

集成电路制造工艺中的High-K材料介绍2025-03-12 3342

-

轴承结构生产工艺流程柴油机轴承的结构与安装2024-12-07 1784

-

简述连接器的工艺流程2024-09-02 6309

-

轴承的生产流程图—轴承生产工艺流程介绍2022-04-15 18741

-

样板贴片的工艺流程是什么2021-04-26 3468

-

SMT贴片加工的工艺流程及作用2020-07-19 10573

-

印制电路板制作工艺流程分享!2019-10-18 3391

-

晶体管管芯的工艺流程?2019-05-26 3445

-

倒装晶片的组装工艺流程2018-11-23 4940

-

单面和双面印制板的制作工艺流程2018-08-31 3824

-

揭秘十一道独门芯片工艺流程2016-07-13 8675

-

pcb工艺流程2016-02-24 1385

-

PCB工艺流程详解2013-05-22 10173

-

半导体材料的工艺流程2010-03-04 2961

全部0条评论

快来发表一下你的评论吧 !