详解I2S时序

描述

01

整体概括

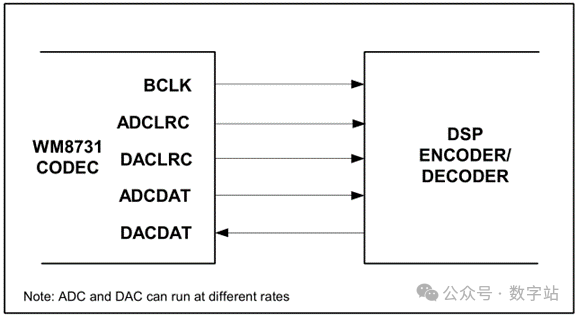

最近调试了一款音频采集芯片wm8731,包含两路音频输入(ADC)和一路音频输出(DAC),音频芯片与主控芯片通过I2S接口传输ADC采集的数据和DAC驱动数据。

本文简要讲解一下I2S协议,该协议包含ADCRC(ADC采集数据的左右声道指示信号)、DACRC(DAC采集数据的左右声道指示信号)、BCLK(位数据对齐时钟)、ADCDAT(ADC输出数据)、DACDAT(DAC采集数据)共五个信号。

WM8731通过ADCRC、BCLK、ADCDAT三个信号传输ADC采集的数据,DACRC、BCLK、DACDAT三个信号传输驱动DAC的数据,ADC和DAC的数据通道共用BCLK信号。ADCDAT和DACDAT均在BCALK的下降沿变化,在BCLK上升沿保持不变。

WM8371的I2S接口包含主机和从机两种模式,两种模式的区别在于时钟(BCLK)和声道指示信号(ADCLRC、DACLRC)由主控芯片还是WM8371提供。

图1是WM8371的主机模式,时钟和声道指示信号均由WM8371提供。

图1 主机模式

下图是WM8731的从机模式,时钟和声道指示信号均由WM8371提供,通过配置内部寄存器实现模式选择,使用FPGA作为主控时,两种模式均可使用,后续详解。

图2 从机模式

02

I2S协议的四种模式

I2S总线根据ADCDAT和DACDAT的数据变化,分为左对齐,右对齐,I2S及DSP共四种模式,其实就是四种数据传输时序,推荐使用左对齐模式或者I2S模式。

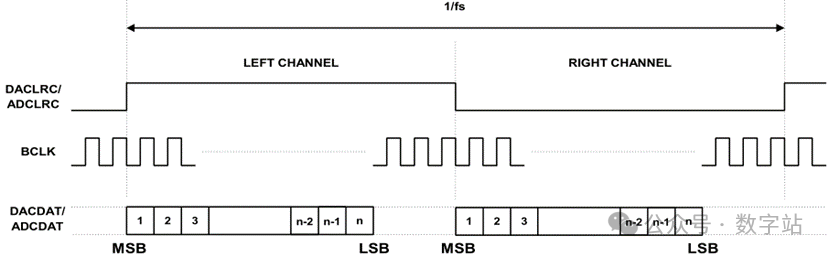

2.1左对齐模式

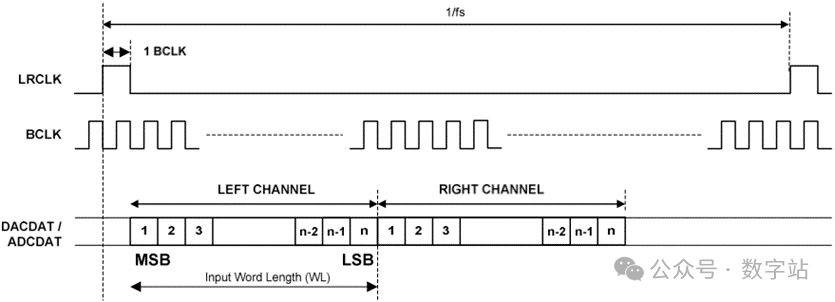

对应时序如下所示,ADCDAT在ADCLRC高电平时传输左声道的数据,ADCDAT在ADCLRC低电平时传输右声道数据,ADCDAT先传输高位数据。ADCLRC的频率等于配置的ADC采样频率fs。

ADCDAT在BCLK的前n个时钟的下降沿传输数据,n表示ADC采集数据的位宽。

图3 左对齐模式

注意BCLK的频率必须大于等于ADC采样率乘以ADC数据位宽乘以2。当WM8371作为主机时,BCLK由WM8371提供,用户不能设置其频率。当WM8371作为从机时,BCLK由用户提供,必须满足频率关系。

注意BCLK的下降沿与ADCLRC/DACLRC的跳变沿对齐,而DACDAT/ADCDAT的第一个数据(MSB)在BCLK下降沿开始传输,即DACDAT/ADCDAT与ADCLRC/DACLRC左边对齐,因此被称为左对齐模式。

在实测主机模式时发现BCLK的周期可能存在占空比不是百分之五十的情况,在设计时需要注意。

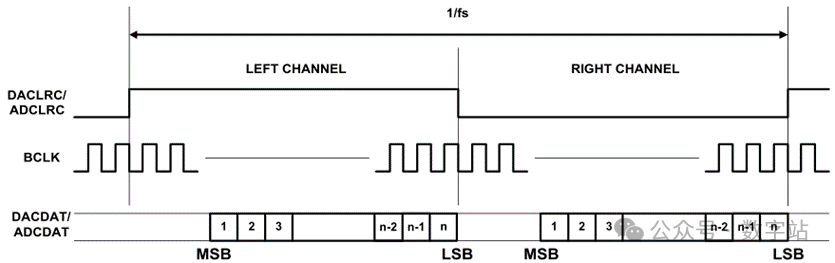

2.2右对齐模式

因为BCLK的频率满足大于等于ADCLRC/DACLRC频率乘以ADC/DAC数据位宽乘以2即可,导致BCLK在ADCLRC/DACLRC高电平或低电平时的时钟个数可能大于ADC/DAC数据位宽,就存在无效时钟。

此时数据起始位与ADCLRC/DACLRC边沿对齐,则是左对齐模式,如果数据的结束位置与ADCLRC/DACLRC边沿对齐,则是右对齐模式,右对齐模式时序如下。

图4 右对齐模式

DACDAT/ADCDAT依旧在BCLK下降沿先传输高位数据,LSB与ADCLRC/DACLRC边沿对齐。

这种模式不好编写适配多种采样率的发送驱动,因为主机模式下不同采样率时ADCLRC/DACLRC电平对应的BCLK个数不同,通用的驱动会比较麻烦,因此一般不推荐使用这类驱动时序。该模式不支持32位ADC和DAC数据位宽。

2.3I2S模式

I2S模式时序如下所示,与左对齐模式类似,但ADCDAT/DACDAT在ADCLRC/DACLRC边沿后的第一个BCLK不传输数据,从BCLK的第二个下降沿传输最高位数据。

图5 I2S模式

图5 I2S模式

该模式使用起来也比较方便,推荐使用。

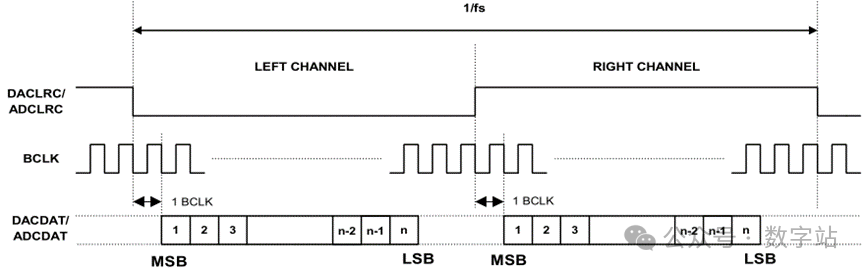

2.4DSP模式

DSP模式时序如下图所示,每次传输数据LRCLK只持续一个BCLK周期,其余时间保持电平。

LRCLK的下降沿与BCLK的下降沿对齐,ADCDAT/DACDAT开始传输n位左声道数据,然后传输n位右声道数据,ADCDAT/DACDAT在剩余的BCLK周期无效。

图6 DSP模式

图6 DSP模式

四种模式下LRCLK和BCLK的频率都是遵守相同规则的,且ADCDAT/DACDAT均在BCLK的下降沿传输数据,在BCLK上升沿期间数据保持不变。

03

WM8371的时序参数

WM8731的ADC和DAC的数据位宽始终为24位,但在I2S或左对齐模式下,数字音频数据可编程为16位、20位、24或32位。即寄存器编程音频数据位宽为16位时,ADCDAT会将ADC采集的高16位数据输出,低8位数据舍弃。如果寄存器编程音频数据位宽为32位时,ADCDAT会把ADC采集的24位数据作为高位,低八位补零,达到32位数据输出。

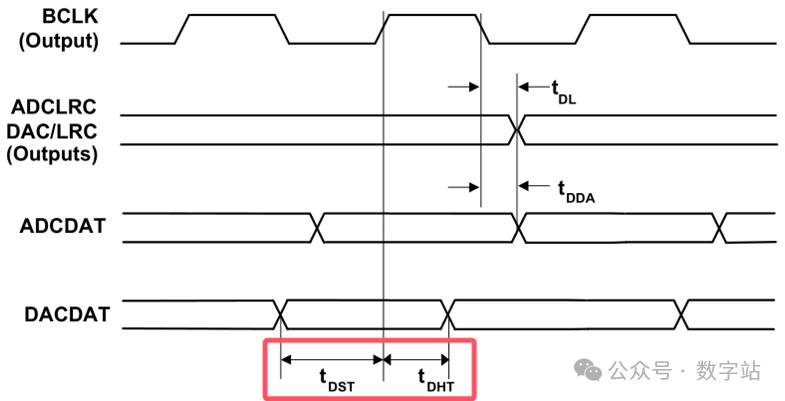

主机模式下的时序参数如下所示,需要重点关注下图红框中的两个时序参数。

图7 主机模式时序参数

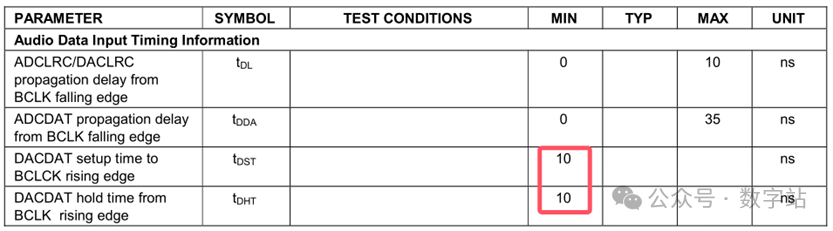

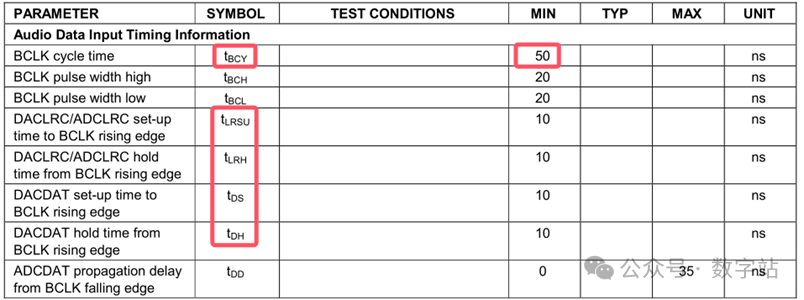

两个时序参数如下表所示,DACDAT必须在BCLK上升沿前后至少10ns内保持稳定。

图8 时序参数

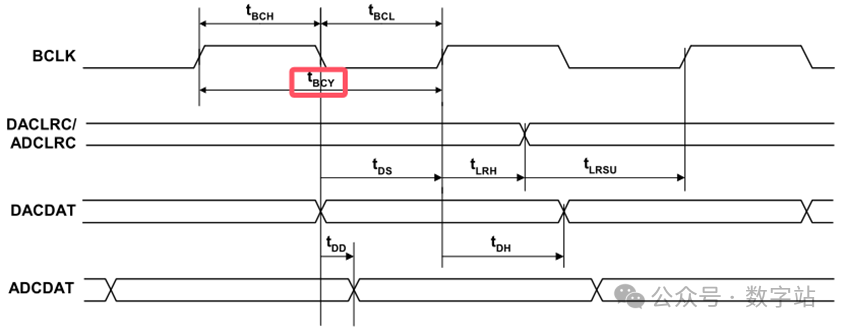

从机模式的时钟信号和声道指示信号都由主控芯片提供,相关的时序参数会多一些,如下图所示。

图9 从机模式时序参数

BCLK的最小周期为50ns,即接口数据传输的最大频率为20MHz,另外DACLRC/ADCLRC和DACDAT在BCLK上升沿前后的10ns内必须保持不变,WM8731才能稳定采集对应信号的状态。

图10 时序参数

本文主要讲解I2S时序,文中图片均来自WM8371芯片手册

-

aic3253的I2S完整的时序图及接口协议如何设置?2024-10-29 352

-

基于MM32F5270的I2S音频播放2023-10-30 3129

-

基于MM32F3270 I2S使用2023-09-27 1999

-

雅特力AT32 MCU SPI/I2S入门指南2023-03-08 8444

-

#硬声创作季 #STM32 手把手教你学STM32-084 I2S录音简介-1水管工 2022-10-29

-

全面解析I2S、TDM、PCM音频总线2022-09-20 16094

-

基于MM32F5270控制器的I2S音频播放2022-09-16 4100

-

音频总线I2S协议:I2S收发模块FPGA的仿真设计2020-12-14 10136

-

几种常见的I2S数据格式2018-01-29 13049

-

CAN、I2S、I2C、SPI、SSP总线的介绍和比较2016-07-14 2180

-

基于FPGA和AD1836的I2S接口设计2011-03-29 7340

-

音频接口I2S实验2010-12-29 1722

全部0条评论

快来发表一下你的评论吧 !