FPGA学习:分布式RAM和Block ram

可编程逻辑

描述

以下分析基于xilinx 7系列

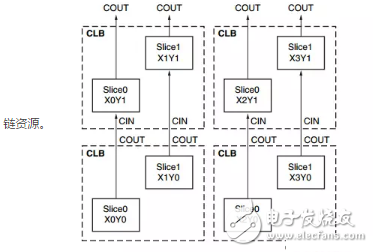

CLB是xilinx基本逻辑单元,每个CLB包含两个slices,每个slices由4个(A,B,C,D)6输入LUT和8个寄存器组成。

同一CLB中的两片slices没有直接的线路连接,分属于两个不同的列。每列拥有独立的快速进位链资源。

slice分为两种类型 SLICEL, SLICEM 。 SLICEL可用于产生逻辑,算术,ROM。 SLICEM除以上作用外还可配置成分布式RAM或32位的移位寄存器。每个CLB可包含两个SLICEL或者一个SLICEL与一个SLICEM.

7系列的LUT包含6个输入 A1 -A6 , 两个输出 O5 , O6 。

可配置成6输入查找表,O6此时作为输出。或者两个5输入的查找表,A1-A5作为输入 A6拉高,O5,O6作为输出。

一个LUT包含6个输入,逻辑容量为2^6bit,为实现7输入逻辑需要2^7容量,对于更多输入也一样。每个SLICES有4个LUT,256bit容量能够实现最多8bit输入的逻辑。为了实现此功能,每个SLICES还包括3个MUX(多路选择器)

F7AMUX 用于产生7输入的逻辑功能,用于连接A,B两个LUT

F7BMUX 用于产生7输入的逻辑功能, 用于连接C,D两个LUT

F8MUX 用于产生8输入的逻辑功能, 用于连接4个LUT

对于大于8输入的逻辑需要使用多个SLICES, 会增加逻辑实现的延时。

一个SLICES中的4个寄存器可以连接LUT或者MUX的输出,或者被直接旁路不连接任何逻辑资源。寄存器的置位/复位端为高电平有效。只有CLK端能被设置为两个极性,其他输入若要改变电平需要插入逻辑资源。例如低电平复位需要额外的逻辑资源将rst端输入取反。但设为上升/下降沿触发寄存器不会带来额外消耗。

分布式RAM

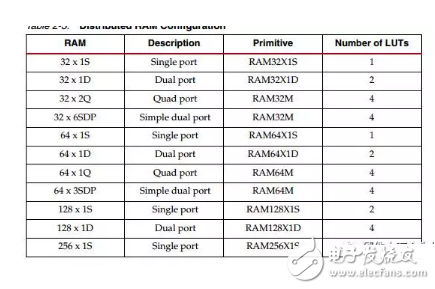

SLICEM可以配置成分布式RAM,一个SLICEM可以配置成以下容量的RAM

多bit的情况需要增加相应倍数的LUT进行并联。

分布式RAM和 BLOCK RAM的选择遵循以下方法:

1. 小于或等于64bit容量的的都用分布式实现

2. 深度在64~128之间的,若无额外的block可用分布式RAM。要求异步读取就使用分布式RAM。数据宽度大于16时用block ram。

3. 分布式RAM有比block ram更好的时序性能。 分布式RAM在逻辑资源CLB中。而BLOCK RAM则在专门的存储器列中,会产生较大的布线延迟,布局也受制约。

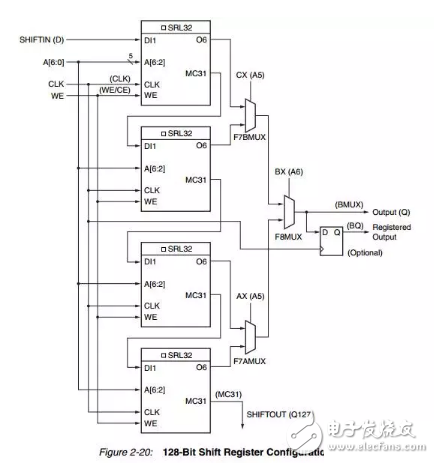

移位寄存器(SLICEM)

SLICEM中的LUT能在不使用触发器的情况下设置成32bit的移位寄存器,4个LUT可级联成128bit的移位寄存器。并且能够进行SLICEM间的级联形成更大规模的移位寄存器。

MUX

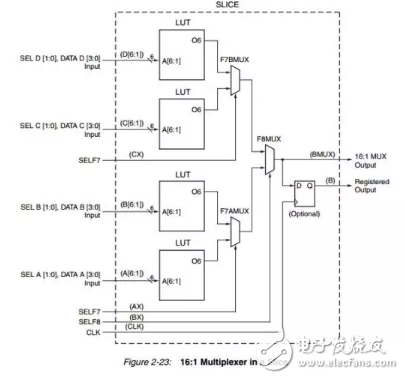

一个LUT可配置成4:1MUX.

两个LUT可配置成最多8:1 MUX

四个LUT可配置成16个MUX

同样可以通过连接多个SLICES达成更大规模设计,但是由于SLICE没有直接连线,需要使用布线资源,会增加较大延迟。

进位链

每个SLICE有4bit的进位链。每bit都由一个进位MUX(MUXCY)和一个异或门组成,可在实现加法/减法器时生成进位逻辑。该MUXCY与XOR也可用于产生一般逻辑。

-

FPGA中块RAM的分布和特性2023-11-21 5270

-

在FPGA设计中如何用LUT组建分布式的RAM2021-07-28 1523

-

使用FPGA调用RAM资源的详细说明2020-12-30 2143

-

FPGA的RAM存储资源详细资料说明2020-12-09 3233

-

xilinx 7系列FPGA里面的Block RAM2020-11-23 9397

-

分布式RAM和Block RAM之间究竟有什么区别?2020-07-19 2643

-

在7系列FPGA上阻止ram vs Distributed ram2020-03-23 2375

-

请问分布式RAM和Block RAM的芯片中有menexternalmemory或内存吗?2019-11-07 2609

-

分布式RAM综合问题2019-06-25 2483

-

分布式RAM中怎么异步读取2019-04-16 2142

-

Block RAM的功耗始终为0mW2019-03-13 2175

-

具有VHDL初始值的分布式RAM?2019-02-26 1957

-

3系列FPGA中使用LUT构建分布式RAM(2)2017-02-11 2854

-

Quartus II 中定制的RAM是分布式的还是块的2014-03-10 2891

全部0条评论

快来发表一下你的评论吧 !